The gem5 simulator

The gem5Simulator

Nathan Binkert1,Bradford Beckmann2,

Gabriel Black3,Steven K.Reinhardt2,Ali Saidi4,Arkaprava Basu5,Joel Hestness6, Derek R.Hower5,Tushar Krishna7,Somayeh Sardashti5,Rathijit Sen5,Korey Sewell8, Muhammad Shoaib5,Nilay Vaish5,Mark D.Hill5,and David A.Wood5

https://www.sodocs.net/doc/0319386950.html,

Abstract

The gem5simulation infrastructure is the merger of the best aspects of the M5[4]and GEMS[9]simulators. M5provides a highly con?gurable simulation framework, multiple ISAs,and diverse CPU models.GEMS comple-ments these features with a detailed and?exible mem-ory system,including support for multiple cache coher-ence protocols and interconnect models.Currently,gem5 supports most commercial ISAs(ARM,ALPHA,MIPS, Power,SPARC,and x86),including booting Linux on three of them(ARM,ALPHA,and x86).

The project is the result of the combined e?orts of many academic and industrial institutions,including AMD, ARM,HP,MIPS,Princeton,MIT,and the Universities of Michigan,Texas,and Wisconsin.Over the past ten years,M5and GEMS have been used in hundreds of pub-lications and have been downloaded tens of thousands of times.The high level of collaboration on the gem5 project,combined with the previous success of the com-ponent parts and a liberal BSD-like license,make gem5a valuable full-system simulation tool.

1Introduction

Computer architecture researchers commonly use soft-ware simulation to prototype and evaluate their ideas. As the computer industry continues to advance,the range of designs being considered increases.On one hand,the 1Hewlett-Packard Labs,Palo Alto,Cal.

2Advanced Micro Devices,Inc.,Bellevue,Wash.

3Google,Inc.,Mountain View,Cal.

4ARM,Inc.,Austin,Tex.

5University of Wisconsin,Madison,Wisc.

6University of Texas,Austin,Tex.

7Massachusetts Institute of Technology,Cambridge,Mass.

8University of Michigan,Ann Arbor,Mich.emergence of multicore systems and deeper cache hier-archies has presented architects with several new dimen-sions of exploration.On the other hand,researchers need a?exible simulation framework that can evaluate a wide diversity of designs and support rich OS facilities includ-ing IO and networking.

Computer architecture researchers also need a simula-tion framework that allows them to collaborate with their colleagues in both industry and academia.However,a simulator’s licensing terms and code quality can inhibit that collaboration.Some open source software licenses can be too restrictive,especially in an industrial setting, because they require publishing any simulator enhance-ments.Furthermore,poor code quality and the lack of modularity can make it di?cult for new users to under-stand and modify the code.

The gem5simulator overcomes these limitations by providing a?exible,modular simulation system that is capable of evaluating a broad range of systems and is widely available to all researchers.This infrastructure provides?exibility by o?ering a diverse set of CPU mod-els,system execution modes,and memory system models.

A commitment to modularity and clean interfaces allows researchers to focus on a particular aspect of the code without understanding the entire code base.The BSD-based license makes the code available to all researchers without awkward legal restrictions.

This paper provides a brief overview of gem5’s goals, philosophy,capabilities,and future work along with pointers to sources of additional information.

2Overall Goals

The overarching goal of the gem5simulator is to be a community tool focused on architectural modeling.Three key aspects of this goal are?exible modeling to appeal to a broad range of users,wide availability and utility to

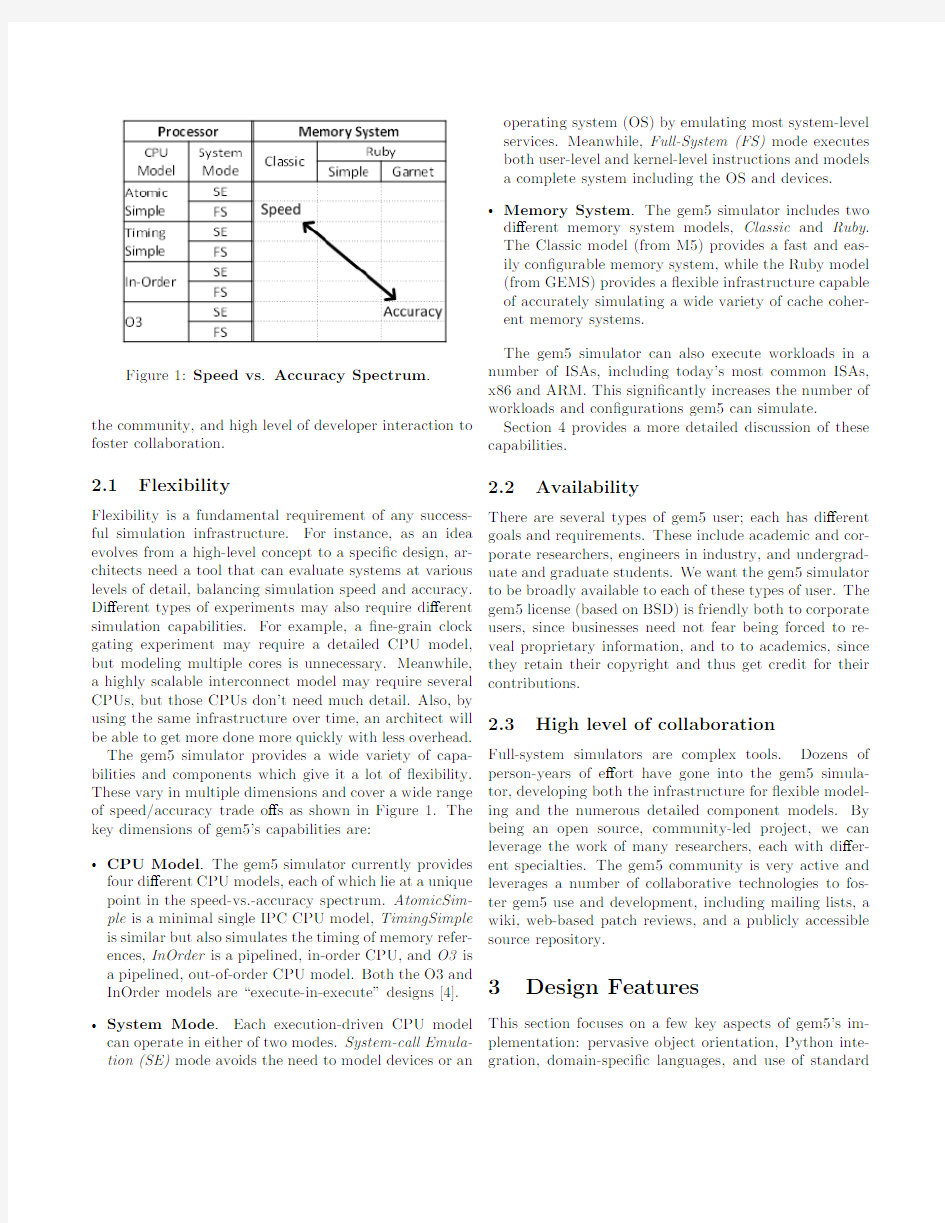

Figure1:Speed vs.Accuracy Spectrum.

the community,and high level of developer interaction to foster collaboration.

2.1Flexibility

Flexibility is a fundamental requirement of any success-ful simulation infrastructure.For instance,as an idea evolves from a high-level concept to a speci?c design,ar-chitects need a tool that can evaluate systems at various levels of detail,balancing simulation speed and accuracy. Di?erent types of experiments may also require di?erent simulation capabilities.For example,a?ne-grain clock gating experiment may require a detailed CPU model, but modeling multiple cores is unnecessary.Meanwhile, a highly scalable interconnect model may require several CPUs,but those CPUs don’t need much detail.Also,by using the same infrastructure over time,an architect will be able to get more done more quickly with less overhead. The gem5simulator provides a wide variety of capa-bilities and components which give it a lot of?exibility. These vary in multiple dimensions and cover a wide range of speed/accuracy trade o?s as shown in Figure1.The key dimensions of gem5’s capabilities are:

?CPU Model.The gem5simulator currently provides four di?erent CPU models,each of which lie at a unique point in the speed-vs.-accuracy spectrum.AtomicSim-ple is a minimal single IPC CPU model,TimingSimple is similar but also simulates the timing of memory refer-ences,InOrder is a pipelined,in-order CPU,and O3is a pipelined,out-of-order CPU model.Both the O3and InOrder models are“execute-in-execute”designs[4].?System Mode.Each execution-driven CPU model can operate in either of two modes.System-call Emula-tion(SE)mode avoids the need to model devices or an

operating system(OS)by emulating most system-level services.Meanwhile,Full-System(FS)mode executes both user-level and kernel-level instructions and models a complete system including the OS and devices.?Memory System.The gem5simulator includes two

di?erent memory system models,Classic and Ruby. The Classic model(from M5)provides a fast and eas-ily con?gurable memory system,while the Ruby model (from GEMS)provides a?exible infrastructure capable of accurately simulating a wide variety of cache coher-ent memory systems.

The gem5simulator can also execute workloads in a number of ISAs,including today’s most common ISAs, x86and ARM.This signi?cantly increases the number of workloads and con?gurations gem5can simulate. Section4provides a more detailed discussion of these capabilities.

2.2Availability

There are several types of gem5user;each has di?erent goals and requirements.These include academic and cor-porate researchers,engineers in industry,and undergrad-uate and graduate students.We want the gem5simulator to be broadly available to each of these types of user.The gem5license(based on BSD)is friendly both to corporate users,since businesses need not fear being forced to re-veal proprietary information,and to to academics,since they retain their copyright and thus get credit for their contributions.

2.3High level of collaboration

Full-system simulators are complex tools.Dozens of person-years of e?ort have gone into the gem5simula-tor,developing both the infrastructure for?exible model-ing and the numerous detailed component models.By being an open source,community-led project,we can leverage the work of many researchers,each with di?er-ent specialties.The gem5community is very active and leverages a number of collaborative technologies to fos-ter gem5use and development,including mailing lists,a wiki,web-based patch reviews,and a publicly accessible source repository.

3Design Features

This section focuses on a few key aspects of gem5’s im-plementation:pervasive object orientation,Python inte-gration,domain-speci?c languages,and use of standard

interfaces.While most of these features are simply good software engineering practice,they are all particularly useful for designing simulators.

3.1Pervasive Object-Oriented Design

Flexibility is an important goal of the gem5simulator and key aspect of its success.Flexibility is primarily achieved through object-oriented design.The ability to construct con?gurations from independent,composable objects leads naturally to advanced capabilities such as multi-core and multi-system modeling.

All major simulation components in the gem5simu-lator are SimObjects and share common behaviors for con?guration,initialization,statistics,and serialization (checkpointing).SimObjects include models of concrete hardware components such as processor cores,caches,in-terconnect elements and devices,as well as more abstract entities such as a workload and its associated process con-text for system-call emulation.

Every SimObject is represented by two classes,one in Python and one in C++which derive from SimObject base classes present in each language.The Python class de?nition speci?es the SimObject’s parameters and is used in script-based con?guration.The common Python base class provides uniform mechanisms for instantiation, naming,and setting parameter values.The C++class en-compasses the SimObject’s state and remaining behavior, including the performance-critical simulation model. 3.2Python Integration

The gem5simulator derives signi?cant power from tight integration of Python into the simulator.While85%of the simulator is written in C++,Python pervades all aspects of its operation.As mentioned in Section3.1, all SimObjects are re?ected in both Python and C++. The Python aspect provides initialization,con?guration, and simulation control.The simulator begins execut-ing Python code almost immediately on start-up;the standard main()function is written in Python,and all command-line processing and startup code is written in Python.

3.3Domain-Speci?c Languages

In situations that require signi?cant?exibility in perform-ing a specialized task,domain-speci?c languages(DSLs) provide a powerful and concise way to express a variety of solutions by leveraging knowledge and idioms common to that problem space.The gem5environment provides two domain-speci?c languages,one for specifying instruc-tion sets(inherited from M5)and one for specifying cache coherence protocols(inherited from GEMS).

ISA DSL.The gem5ISA description language uni?es the decoding of binary instructions and the speci?cation of their semantics.The gem5CPU models achieve ISA independence by using a common C++base class to de-scribe instructions.Derived classes override virtual func-tions like execute()to implement opcodes,such as add. Instances of these derived classes represent speci?c ma-chine instructions,such as add r1,r2,r3.Implementing a speci?c ISA thus requires a set of C++declarations for these derived classes,plus a function that takes a machine instruction and returns an instance of one of the derived classes that corresponds to that instruction.

The ISA description language allows users to specify this required C++code compactly.Part of the language allows the speci?cation of class templates(more general than C++templates)that cover broad categories of in-structions,such as register-to-register arithmetic opera-tions.Another portion of the language provides for the speci?cation of a decode tree that concisely combines op-code decoding with the creation of speci?c derived classes as instances of the previously de?ned templates.

While the original ISA description language targeted RISC architectures such as the Alpha ISA,it has been sig-ni?cantly extended to cope with complex variable-length ISAs,particularly x86,and ISAs with complex register semantics like SPARC.These extensions include a mi-crocode assembler,a predecoder,and multi-level register index translation.These extensions are discussed in more detail in a recent book chapter[5].

Cache Coherence DSL.SLICC is a domain-speci?c language that gives gem5the?exibility to implement a wide variety of cache coherence protocols.Essentially, SLICC de?nes the cache,memory,and DMA controllers as individual per-memory-block state machines that to-gether form the overall protocol.By de?ning the con-troller logic in a higher-level language,SLICC allows dif-ferent protocols to incorporate the same underlying state transition mechanisms with minimal programmer e?ort. The gem5version of SLICC is very similar to the prior GEMS version of SLICC[9].Just like the prior version, gem5SLICC de?nes protocols as a set of states,events, transitions,and actions.Within the speci?cation?les, individual transition statements de?ne the valid combi-nations and actions within each transition specify the op-erations that must be performed.Also similar to the pre-vious version,gem5SLICC ties the state machine-speci?c logic to protocol-independent components such as cache memories and network ports.

While gem5SLICC contains several similarities to its predecessor design,the language does include several en-hancements.First,the language itself is now imple-mented in Python rather than C++,making it easier to read and edit.Second,to adhere to the gem5SimOb-ject structure,all con?guration parameters are speci?ed as input parameters and gem5SLICC automatically gen-erates the appropriate C++and Python?les.Finally, gem5SLICC allows local variables to simplify program-ming and improve performance.

3.4Standard Interfaces

Standard interfaces are fundamental to object-oriented design.Two central interfaces are the port interface and the message bu?er interface.

Ports are one of the interfaces used to connect two memory objects together in gem5.In the Classic memory system,the ports interface connects all memory objects including CPUs to caches,caches to busses,and busses to devices and memories.Ports support three mecha-nisms for accessing data(timing,atomic,and functional) and an interface for things like determining topology and debugging.Timing mode is used to model the detailed timing of memory accesses.Requests are made to the memory system by sending messages,and responses are expected to return asynchronously via other messages. Atomic mode is used to get some timing information,but is not message-oriented.When an atomic call is made (via a function call),the state change for the operation is performed synchronously.This has higher performance but gives up some accuracy because message interactions are not modeled.Finally,functional accesses update the simulator state without changing any timing information. These are generally used for debugging,system-call emu-lation,and initialization.

Ruby utilizes the ports interface to connect to CPUs and devices,and adds message bu?ers to connect to Ruby objects internally.Message bu?ers are similar to ports in that they provide a standard communication interface. However,message bu?ers di?er in some subtle ways with regards to message typing and storage.In the future, ports and message bu?ers may evolve into a uni?ed in-terface.

4Simulation Capabilities

The gem5simulator has a wide range of simulation capa-bilities ranging from the selection of ISA,CPU model,and coherence protocol to the instantiation of interconnection networks,devices and multiple systems.This section de-scribes some of the di?erent options available in these categories.

ISAs.The gem5simulator currently supports a variety of ISAs including Alpha,ARM,MIPS,Power,SPARC, and x86.The simulator’s modularity allows these di?er-ent ISAs to plug into the generic CPU models and the memory system without having to specialize one for the other.However,not all possible combinations of ISAs and other components are currently known to work.An up-to-date list can be found on the gem5website. Execution Modes.The gem5simulator can oper-ate in two modes:System-call Emulation(SE)and Full-System(FS).In SE mode,gem5emulates most com-mon system calls(e.g.read()).Whenever the pro-gram executes a system call,gem5traps and emulates the call,often by passing it to the host operating system. There is currently no thread scheduler in SE mode,so threads must be statically mapped to cores,limiting its use with multi-threaded applications.The SPEC CPU benchmarks are often run in SE mode.

In FS mode,gem5simulates a bare-metal environment suitable for running an OS.This includes support for in-terrupts,exceptions,privilege levels,I/O devices,etc. Because of the additional complexity and completeness required,not all ISAs current support FS mode. Compared to SE mode,FS mode improves both the simulation accuracy and variety of workloads that gem5 can execute.While SPEC CPU benchmarks can be run in SE mode,running them in FS mode will provide more realistic interactions with the OS.Workloads that require many OS services or I/O devices may only be run in FS mode.For example,because a web server relies on the kernel’s TCP/IP protocol stack and a network interface to send and receive requests and a web browser requires a X11server and display adapter to visualize web pages these workloads must be run is FS mode.

CPU Models.The gem5simulator supports four dif-ferent CPU models:AtomicSimple,TimingSimple,In-Order,and O3.AtomicSimple and TimingSimple are non-pipelined CPU models that attempt to fetch,decode, execute and commit a single instruction on every cycle. The AtomicSimple CPU is a minimal,single IPC CPU which completes all memory accesses immediately.This low overhead makes AtomicSimple a good choice for sim-ulation tasks such as fast-forwarding.Correspondingly, the TimingSimple CPU also only allows one outstanding memory request at a time,but the CPU does model the timing of memory accesses.

The InOrder model is an“execute-in-execute”CPU model emphasizing instruction timing and simulation ac-

curacy with an in-order pipeline.InOrder can be con?g-ured to model di?erent numbers of pipeline stages,issue width,and numbers of hardware threads.

Finally,the O3CPU is a pipelined,out-of-order model that simulates dependencies between instructions,func-tional units,memory accesses,and pipeline stages.Pa-rameterizable pipeline resources such as the load/store queue and reorder bu?er allow O3to simulate superscalar architectures and CPUs with multiple hardware threads (SMT).The O3model is also“execute-in-execute”,mean-ing that instructions are only executed in the execute stage after all dependencies have been resolved.

Cache Coherence Protocols.SLICC enables gem5’s Ruby memory model to implement many di?er-ent types of invalidation-based cache coherence protocols, from snooping to directory protocols and several points in between.SLICC separates cache coherence logic from the rest of the memory system,providing the necessary abstraction to implement a wide range of protocol logic. Similar to its GEMS predecessor[9],SLICC performs all operations at a cache-block granularity.The word-level granularity required by update-based protocols is not cur-rently supported.This limitation has not been a issue so far because invalidation-based protocols dominate the commercial market.Speci?cally,gem5SLICC currently models a broadcast-based protocol based on the AMD Opteron TM[7],as well as a CMP directory protocol[10]. Not only is SLICC?exible enough to model di?erent types of protocols,but it also simulates them in su?cient depth to model detailed timing behavior.Speci?cally, SLICC allows specifying transient states within the in-dividual state machines as cache blocks move from one base state to another.SLICC also includes separate vir-tual networks(https://www.sodocs.net/doc/0319386950.html,work message classes)so message dependencies and stalls can be properly https://www.sodocs.net/doc/0319386950.html,ing these virtual networks,the SLICC-generated controllers connect to the interconnection network. Interconnection Networks.The Ruby memory model supports a vast array of interconnection topologies and includes two di?erent network models.In essence, Ruby can create any arbitrary topology as long as it is composed of point-to-point links.A simple Python?le declares the connections between components and short-est path analysis is used to create the routing tables. Once Ruby creates the links and routing tables,it can implement the resulting network in one of two ways. The?rst Ruby network model is referred to as the Sim-ple network.The Simple network models link and router latency as well as link bandwidth.However,the Simple network does not model router resource contention and ?ow control.This model is great for experiments that require Ruby’s detailed protocol modeling but that can sacri?ce detailed network modeling for faster simulation. The second Ruby network model is the Garnet network model[1].Unlike the simple network,Garnet models the router micro-architecture in detail,including all relevant resource contention and?ow control timing.This model is suitable for on-chip network studies.

Devices.The gem5simulator supports several I/O devices ranging from simple timers to complex network interface controllers.Base classes are available that en-capsulates common device interfaces such as PCI to avoid code duplication and simplify implementing new devices. Currently implemented models includes NICs,an IDE controller,a frame bu?er,DMA engines,UARTs,and interrupt controllers.

Modeling Multiple Systems.Because of the simu-lator’s object oriented design it also supports simulating multiple complete systems.This is done by instantiating another set of objects(CPU,memory,I/O devices,etc.). Generally,the user connects the systems via the network interfaces described above to create a client/server pair that communicate over TCP/IP.Since all the simulated systems are tightly coupled within gem5the results of multi-system simulation is still deterministic.

5Future Work

While gem5is a highly capable simulator,there is always a desire for additional features and other improvements.

A few of the e?orts underway or under consideration in-clude:

?A?rst-class power model.While external power mod-els such as Orion[6]and McPAT[8]have been used with GEMS and M5,we are working on a more com-prehensive,modular,and integrated power model for gem5.

?Full cross-product ISA/CPU/memory system support. The modularity and?exibility of gem5enables a wide variety of combinations of ISAs,CPU models,and memory systems,as illustrated in Figure1,each of which can be used in SE or FS mode.Because each component model must support the union of all fea-tures required by any ISA in any mode,particular com-ponent models do not always work in every conceivable circumstance.We continue to work to eliminate these inconsistencies.

?Parallelization.To address the inherent performance limitations of detailed simulation and leverage the ubiq-uity of multi-core systems,we have been refactoring

gem5’s internal event system to support parallel dis-crete event simulation[11].

?Checkpoint import.Although gem5’s simple CPU models are much faster than their detailed counter-parts,they are still considerably slower than binary translation-based emulators such as QEMU[3]and SimNow TM[2].Rather than duplicating the enor-mous e?ort of developing a binary translation capabil-ity within gem5,we plan to enable the transfer of state checkpoints from these emulators into https://www.sodocs.net/doc/0319386950.html,ers will be able to fast-forward large workloads to interesting points using these high-performance alternatives,then simulate from those points in gem5.Even higher per-formance may be possible by using a hardware virtual machine environment such as KVM1rather than binary translation.

6User Resources

All gem5simulator documentation and information is available at the website https://www.sodocs.net/doc/0319386950.html,.The web-site includes instructions on how to check out,build,and run the gem5simulator,as well as how to download sup-plemental support?les like OS binaries and disk images. The gem5user community is active and communicates through three mailing lists:(1)the announce mailing list is used to announce signi?cant modi?cations or achieve-ments;(2)the user mailing list is used for general discus-sions about gem5and for questions about how to use it; and(3)the dev mailing list is for discussions regarding mainline gem5development.

Developers will?nd support resources in the form of systems for revision control,bug tracking,code reviews, and code browsing.All of these can be accessed through the main website.

We encourage you to visit the web site,subscribe to the mailing lists,and help us make gem5a valuable com-munity resource.

Acknowledgements

The authors of this paper are only a small subset of peo-ple that have contributed to gem5over the years.We would like to specially thank all those prior contributors to GEMS and M5,especially Dan Gibson who played a key role in the initial integration e?ort.Without their work,the uni?cation of GEMS and M5would not have been possible.

1https://www.sodocs.net/doc/0319386950.html,

The gem5simulator has been developed with gen-erous support from several sources,including the Na-tional Science Foundation,AMD,ARM,Google,Hewlett-Packard,IBM,Intel,Microsoft,MIPS,Sandia National Laboratories and Sun.Individuals working on gem5 have also been supported by fellowships from Intel,Lu-cent,and the Alfred P.Sloan Foundation.This material is based upon work supported by the National Science Foundation under the following grants:CCR-0105503, CCR-0219640,CCR-0324878,EAI/CNS-0205286,CCR-0105721,CRI-0551401,CSR-0720565,CCF-0916725,and CCF-1017650.

Any opinions,?ndings and conclusions or recommenda-tions expressed in this material are those of the author(s) and do not necessarily re?ect the views of the National Science Foundation(NSF)or any other sponsor. References

[1]Agarwal,N.,Krishna,T.,Peh,L.-S.,and

Jha,N.K.GARNET:A detailed on-chip network model inside a full-system simulator.In Proceedings of IEEE International Symposium on Performance Analysis of Systems and Software(ISPASS)(Apr.

2009),pp.33–42.

[2]Barnes,B.,and Slice,J.SimNow:A fast and

functionally accurate AMD X86-64system simula-tor.Tutorial at the IEEE International Workload Characterization Symposium,2005.

[3]Bellard,F.QEMU,a fast and portable dynamic

translator.In Proceedings of the USENIX Annual Technical Conference(2005),pp.41–46.

[4]Binkert,N.L.,Dreslinski,R.G.,Hsu,L.R.,

Lim,K.T.,Saidi,A.G.,and Reinhardt,S.K.

The M5Simulator:Modeling Networked Systems.

IEEE Micro26,4(Jul/Aug2006),52–60.

[5]Black,G.,Binkert,N.,Reinhardt,S.K.,

and Saidi,A.Processor and System-on-Chip Sim-ulation.Springer,2010,ch.5,“Modular ISA-Independent Full-System Simulation”.

[6]Kahng,A.B.,Li,B.,Peh,L.-S.,and Samadi,

K.ORION2.0:a fast and accurate NoC power and area model for early-stage design space explo-ration.In Proceedings of the Conference on Design, Automation and Test in Europe(2009),pp.423–428.

[7]Keltcher,C.N.,McGrath,K.J.,Ahmed,A.,

and Conway,P.The AMD Opteron Processor for

Multiprocessor Servers.IEEE Micro23,2(Mar/Apr 2003),66–76.

[8]Li,S.,Ahn,J.H.,Strong,R.D.,Brockman,

J.B.,Tullsen,D.M.,and Jouppi,N.P.Mc-PAT:an integrated power,area,and timing modeling framework for multicore and manycore architectures.

In Proceedings of the42nd Annual IEEE/ACM In-ternational Symposium on Microarchitecture(2009), pp.469–480.

[9]Martin,M.M.K.,Sorin, D.J.,Beckmann,

B.M.,Marty,M.R.,Xu,M.,Alameldeen,

A.R.,Moore,K.E.,Hill,M.D.,and Wood,

D. A.Multifacet’s general execution-driven mul-

tiprocessor simulator(GEMS)toolset.SIGARCH Comput.Archit.News33,4(2005),92–99.

[10]Marty,M.R.,Bingham,J.D.,Hill,M.D.,

Hu,A.J.,Martin,M.M.K.,and Wood,D.A.

Improving multiple-CMP systems using token coher-ence.In Proceedings of the11th Annual International Symposium on High-Performance Computer Archi-tecture(HPCA)(2005),pp.328–339.

[11]Reinhardt,S.K.,Hill,M.D.,Larus,J.R.,

Lebeck,A.R.,Lewis,J.C.,and Wood,D.A.

The Wisconsin Wind Tunnel:Virtual prototyping of parallel computers.In Proceedings of the1993 ACM SIGMETRICS Conference on Measurement and Modeling of Computer Systems(1993),pp.48–

60.

虚拟演播室方案

虚拟演播室是视频技术于计算机技术结合的产物,把计算机图形图像处理技术与传统的色键技术集合起来形成的。是一种新颖的独特的电视节目制作技术。 虚拟演播室技术原理:虚拟演播室技术与色键技术十分相像,他是由前景主持人为主的画面和背景画面,采用色键的方法构成一个整体,产生人物置身于背景中的组合画面。 虚拟演播室工作原理 虚拟演播室装修的总体要求: 建立一个功能完善的虚拟演播室,需要做到如下基本要求: 1、要求演播室的拾音空间首先具有较好的语言清晰度、可懂度,其次是要有良好的声音丰满度, 2、要求演播室内各处要有合适的响度和均匀度,具有相应的满足拾音要求的混响频率特性。 3、抑制影响听、拾音音质的声缺陷,防止出现声聚焦、驻波、颤动回声、低频嗡声等。 4、演播室内墙面的声学装饰考虑在装饰大方美观、造型新颖的基础上对于高中低各频段的声学处理方式,特别是低频段的声学处理方式方法。 演播室的建声指标:混响时间≤0.6S±0.05S;噪声评价曲线NR-30---NR-35。 设计的隔声门隔声量大于35dB并具有好的密封性。 5、演播室声学建声装饰所选用的材料符合国家相应的强制消防要求,要求采用达到B1、B2级标准的材料。 6、演播室声学建声装饰所选用的材料符合国家相应的强制环保要求,特别是要求甲醛的释放量为<0。1mg/m3。墙面装饰层内禁止使用不安全和危害性较高的吸声材料。 7、装饰踢脚线兼做视音频线槽并做屏蔽处理。 8、演播室配置录制指示灯和紧急逃生指示灯。 9、装饰层内的综合布线按要求做穿管处理。 10、演播室现有的位置南边部分为玻璃幕墙,不利于演播室的隔声,所以要对原幕墙部分进行隔断,制作隔声封闭处理,在保证整体装饰的美观性和隔声性的同时,还应保证演播室正常的通风换气。 11、导控室地面用防静电地板,装修过程中做好设备布线(强电,弱电),做好防雷,接地各类设施的设计施工。 12、装修预留好空调位置,并配合本台做好空调,配电等设备的安装施工。

虚拟演播室系统方案

VS-VSCENE 虚拟演播室系统方案建议书北京华视恒通系统技术有限公司

北京华视恒通系统技术有限公司 目栩 公司简介................................................................................................................................................................... 3.. . 惊)前悅........................................................................................................................................................................................ 4.. . . 二)系统方案设计.................................................................................................................................................. 4.. . 1、设计原则........................................................................................................................................... 4.. . 2、设计方案........................................................................................................................................... 5.. . 3、系统结构原枞图............................................................................................................................. 7.. . 4、系统功能特点 ................................................................................................................................ 1..0. 5、TOPACK-C抠K 像卡................................................................................................................ 1..2 6、TOPACK-CG/AUD旓IO幕混愃卡 ................................................................................ 1..3 三)软件系统功能................................................................................................................................................. 1..5. 1、系统参数设敢 ................................................................................................................................ 1..5. 2、抠像参数设敢 ................................................................................................................................ 1..7. 3、场景编排.......................................................................................................................................... 1..8. 4、实时控敥.......................................................................................................................................... 2..0. 5、远程旓幕客户端............................................................................................................................ 2..2. 四)设备悪本及效果图........................................................................................................................................ 2..3. 五)系统配敢........................................................................................................................................................................................ 2..4 . 售后服务措施及承诺 ............................................................................................................................................. 2..6.

虚拟演播室灯光技术说明

虚拟演播室技术说明 由于虚拟演播室系统不同于传统演播室的抠像,它允许几台摄象机在不同的角度分做推、拉、摇、移等动作。为了保证摄象机在蓝箱中拍摄的人物与计算机制作的虚拟场景通过色键组合成系统准确合成,要求虚拟演播室系统中人物的活动空间(蓝箱)要有非常均匀和柔和的照明,不能有硬的影子出现,所以首先应用柔光灯把蓝箱铺满打匀,形成一个基本光。 根据贵台的实际情况,设计方案如下: 1.篮箱立面墙的布光:在灯具的选择上,虽然近年来国内一些灯 光企业相继推出了虚拟演播室专用灯光设备,但是由于大多数 电视台虚拟演播室是在原有传统演播室中设置的,所以虚拟演 播室的布光可利用传统演播室的灯具进行布光。布光时,我们 首先考虑选用冷光源——4×55W三基色柔光灯9台,由于它是 散射型光源,布光面积大,容易将墙体的光布匀。 2.篮箱地面布光:在虚拟演播室节目制作时,画面如果出人物的 全景,出现虚拟的地面时,这时不但主持人身后和两侧的蓝墙 要有均匀的布光,而且蓝箱的地面也要有非常均匀的照明。本 方案我们采用4×55W三基色柔光灯6台,作为地面布光,使 篮箱地面光线均匀; 3.人物布光:虚拟演播室人物的布光基本方法和对光比的要求, 仍采用传统演播室的三点式布光和对光比的要求,但同时要考 虑到虚拟演播室的特点。灯光人员在布光前要使人物的主光方

向与虚拟场景中的主光方向一致,同时使光的强弱、硬柔、色彩也都要与虚拟场景中的主光方向一致。使人和景在画面上融为一体,看起来真实。方案采用冷热光源混合式布光,用2台6×55W三基色柔光灯作为侧光,4×55W、6×55W三基色柔光灯各2台,1KW透射式聚光灯2台,作为人物的主面光和辅助面光,使拍摄人物更加丰满圆润; 4.吊挂系统采用格珊架式悬挂,充分利用室内空间高度,避免拍 摄全景时发生“穿帮”现象; 5.整个虚拟演播室采用冷热混合光源布光,总功率为9KW、色温 3200k、中心照度900Lux,满足贵台的虚拟演播室拍摄需求。

虚拟演播室方案

SUNUR-VS三维虚拟演播室系统集成方案 一、系统综述 如何在有限的时间内,不用花费大量的精力和财力,就能轻松地搭建出富有创意的演播室,制作出精彩新颖又充满无限魅力的节目?如何在现有的标清环境下选择面向未来的高清系统而不浪费投资?福州索普电子科技有限公司推出的面向未来创新虚拟演播室系统——SUNUR-VS,一个先进的、实用的、高度集成的、真三维、全场景的虚拟演播室完整解决方案,可以轻而易举地让您的梦想成真。 SUNUR VS三维虚拟场景解决方案使虚拟演播室系统去除了烦琐的硬件配置和大规模的数据运算,凭借简单的设置和直观的用户界面,使之成为一套功能强大的广播电视节目制作工具。只要利用摄影棚中的一小部分空间搭配绿色或蓝色背景,加上摄影灯光,把人物拍下,通过系统集成的色键器,对摄像机获得的信号与虚拟演播室系统信号进行处理,即可实现演播主体与虚拟场景的合成。从此,不再受狭小空间和景物的限制,使用SUNUR VS三维虚拟演播室系统,充分发挥您的想象力和创造力,便可满足任何电视节目现场直播、后期制作及应用的需要。并且,SUNUR VS 无三维虚拟演播室系统具有颠覆传统的业界最优的性价比。通过极快速的启动时间和极低的成本,SUNUR VS三维虚拟演播室系统能为新闻电视广播、体育、财经、现场访谈、气象、远程教育、娱乐节目、广告、游戏秀以及许多其他应用领域提供理想的硬件和软件解决方案。 二、系统方案设计原则 随着电视业和计算机技术的极速发展,高清制作和播出的要求也离我们越来越

近,虚拟演播室的更新步伐不断加快,大家对节目的制作水平和信号质量要求不断提高,SUNUR VS三维虚拟演播室系统本着"简捷至上"的设计宗旨,充分体现系统的技术先进性、功能完整性、经济实用性、运行可靠性、操作灵活性及系统扩展性,不仅能满足现阶段的需要,同时确保系统在今后相当长一段时间内具有先进性并留有扩展余地。在设计方案的过程中,首先考虑到系统要满足演播室现行技术要求,及其应用领域,同时又符合当今虚拟化的趋势,我们遵循以下几个原则: 1、技术的先进性 SUNUR VS三维虚拟演播室系统是福州索普公司在国外虚拟现实软件的基础上开发而来的真三维虚拟演播室系统,该系统是针对市场反馈,专为广电和电教系统应用量身定做和特别优化设计。 SUNUR VS三维虚拟演播室系统,采用革命性的独特设计,无需传感器,采用独有的虚拟摄像机结构,使得产品的安装、初始调试、使用极其方便,省却了繁琐的安装调试过程,真正作到随架随用,一开就用,迅速快捷。一人即可实现多机位的节目演播操作工作,并且真实人像与实时渲染的三维虚拟背景同步运行。如果用户习惯使用传感器系统时可通过增加传感器实现传统虚拟演播室功能。 SUNUR VS三维虚拟演播室系统一开始设计就采用HDSDI高清输入,并能兼容标清输入。在用户预算可能的情况下可以直接使用高清设备,并实现高清、标清、N制、P制混合输入。并在此基础上开发出基于模拟及HDMI接口输入的配套产品,以满足不同经济条件的用户的不同个性化需求。 2、功能完整性 SUNUR VS三维虚拟演播室系统功能完善。 系统集成了色键器、切换台等多种功能。 您无需使用昂贵的摄像机动作传感器,系统采用独有的虚拟摄像机结构。能够轻松的在3D场景中设置和改变8个不同的虚拟摄像机位置(模拟配置),还可方便地编辑3D场景中摄像机的运动速度和运动轨迹。通过与3D虚拟场景进行实时地无缝结合,可进行多重虚拟摄像机的显示与切换。 在系统配置的动作设计模块中,可以生成实时的镜像反射效果,增强了场景的真实感。

VR虚拟演播室系统方案

VR虚拟演播室系统建设方案Make your dream magic ,make your life magic

目录 1.建设背景 (3) 2.设计原则 (4) 3.需求分析 (8) 4.VR情景互动虚拟演播室系统 (10) 方案概述 (10) 系统拓扑图 (11) 核心设备及功能 (11) VStage情景互动虚拟演播室系统 (11) 摄像采集设备 (25) 快速编辑模块 (25) 5.方案优势 (30) 6.售后服务与技术支持 (33) VR虚拟演播室系统建设方案

1.建设背景 虚拟演播室系统(The Virtual Studio System,简称VSS)是近年发展起来的一种独特的电视节目制作技术。它的实质是将计算机制作的虚拟三维场景与摄像机现场拍摄的人物活动图像进行数字化的实时合成,使人物与虚拟背景能够同步变化,从而实现两者天衣无缝的融合,以获得完美的合成画面。采用虚拟演播室技术,可以制作出任何想象中的布景和道具。无论是静态的,还是动态的,无论是现实存在的,还是虚拟的。这只依赖于设计者的想象力和三维软件设计者的水平。许多真实演播室无法实现的效果,对于虚拟演播室来说,却是“小菜一碟”。 从跟踪方式的区分,虚拟演播室分为有轨虚拟演播室和无轨虚拟演播室。有轨跟踪虚拟演播室系统应用摄像机跟踪技术,获得真实摄像机数据,并与计算机生成的背景结合在一起,背景成像依据的是真实的摄像机拍摄所得到的镜头参数,因而和主持人的三维透视关系完全一致,避免了不真实、不自然的感觉。虚拟演播室的跟踪技术有4种方式可以实现,网格跟踪技术、传感器跟踪技术、红外跟踪技术、超声波跟踪技术,其基本原理都是采用图形或者机械的方法,获得摄像机的参数,包括摄像机的X、Y、Z、(位置参数)Pan、Till、(云台参数)Zoom、Focus(镜头参数)由于每一帧虚拟背景只有20ms的绘制时间,所以要求图形工作站实时渲染能力非常强大,对摄像机的运动没有更多的限制,一般适合专业电视台,对节目制作要求较高的用户使用。但调试非常复杂,耗时长,需要专业人士才能操控。无轨虚拟演播室相对比较简单,它是预生成三维背景,即首先要制作好背景的三维模型,然后预先定义好虚拟摄像机的机位和镜头参数,根据这些数据生成每台虚拟摄像机的视图画面,最

SUNUR-VS虚拟演播室操作说明

SUNUR-VS虚拟演播室界面说明导入场景 1、点击导入场景按钮,选择D盘下所要应用的场景; 2、场景载入。

场景管理 视频:点击视频,显示select live and mic操作界面,选择视频decklink video capture(2),选择音频decklink audio capture(2),选择select完成,选择1280*720 50帧(与来自摄像机信号相匹配),出现来自摄像机信号。

文件:点击文件,选择来自计算机的视频文件,导入完成。 物体:物体是对视频活文件的一个赋予(可以将文件或视频赋予给大屏或主持人) 物体控制:点击此按钮,可对主持人、LOGO或物体,对其进行大小、位置进行改变。 隐藏:对当前选中的对象进行隐藏和显示操作。(一般当前操作的对象会在下方显示) 定向、跟随:在被选对象的旋转操作时,进行定向或跟随操作(建议一般在旋转场景时不要使用跟随)。 16:9:点击按钮,进行4:3和16:9的切换。 抠像设置 应用抠像:对当前对象进行抠像操作应用。

取消抠像:对当前对象取消抠像操作应用。 网格背景:对当前所选对象进行网格背景和黑色背景的切换。黑色背景:对当前所选对象进行网格背景和黑色背景的切换。ALPHA:对所选视频进行alpha通道的抠像。(使要被保留的对象全部变成白色,要去掉的对象全部变成黑色。即黑透白不透)COLOR:对所选视频进行彩色通道的抠像。 黑色通道:对所选视频进行黑色通道抠像的参数调整(不要的对象如背景通过此按钮全部调成黑色) 白色通道:对所选视频进行白色通道抠像的参数调整(要保留的对象如主持人通过此按钮全部调成白色) 边缘色溢:对所选视频进行色溢参数调整(其实是对住要扣的对象进行实际色彩的调整,类似于条白平衡)。 色阀调节:对所选视频进行色阀参数调整(可以理解为对一开始的取色进行色彩饱和度的调整)。另外通过此按钮和白色通道的调整可对要抠对象的边缘进行更加完美的调整。 上边裁边:对所选视频进行上裁边操作。 下边裁边:对所选视频进行下裁边操作。 左边裁边:对所选视频进行左裁边操作。 右边裁边:对所选视频进行右裁边操作。 人物反射:对人物在地面上的反射进行参数调整。 地面反射:对虚拟背景进行在地面上反射参数的调整。

虚拟演播室使用说明

虚拟演播室管理制度 为规范虚拟演播室管理,保证灯光、音响及拍摄系统的正常使用,充分发挥虚拟演播室的作用,特制定本制度。 一、虚拟演播室的使用程序 1、进机房后,先打开配电柜,按从左到右的顺序依次打开第一排和第二排的开关。将调光台总输出推到9的位置,再将分输出推到3的位置,预热1到2分钟后在将分输出推到10的位置。 2、虚拟演播室操作人员先打开主控设备后,摄像人员打开摄像机,通过麦克联系,调节场景,操作人员不得擅自挪动灯位,避免妨碍他人使用。调节时,摄像人员先将摄像机拉至远景,虚拟演播室操作人员激活场景后,摄像人员按摄像机架黑盒上的红钮,使场景与摄像机同步,不得擅自挪动机位。 3、灯光调节结束后,虚拟演播室操作人员再调节场景的位置,并进行抠像。主持人试音,录制人员调节调音台。 4、录制结束后,摄像人员先将调光台总输出缓慢拉到3,关闭摄像机,把摄像机用布盖好后,再将调光台总输出拉到0。关闭配电柜中第二排开关,再按照从右至左的顺序关闭第一排开关并锁好门。虚拟演播室人员退出程序,关闭所有设备的开关。 5、因操作失误或不规范造成灯光、蓝箱、提字器、摄像机等机房设备损坏,处罚金100元以上。 二、虚拟演播室卫生 保持清洁的环境。拍摄结束后打扫卫生,恢复演播室内设施,将杂物

带离演播室。人员在蓝箱中要注意安全区域,不可踩踏蓝箱的连接部分,以免损坏蓝箱。 三、虚拟演播室防火 演播室内存在易燃材料,严谨吸烟,发现吸烟现象,将予以重罚。由于吸烟引起的火灾将,肇事人应负法律责任。 四、虚拟演播室的所有节目录制和技术保障由总编室技术人员负责,遇到技术故障请及时报知总编室进行排除。

虚拟演播室教程

1、界面速览 (1)输入区,界面的左上方,可以选择,浏览和改变在(素材预览监示)处输入素材。 (2)输入按钮,显示在防前屏幕上的输入素材,可通过向按钮上拖拉兼容的视频文件来改变内容。点击按钮会在(素材预览监示)上显示视频素材。 (3)输出预览监视是所有输入素材的合并。 (4)在输入区,你可以在下拉菜单中选择想要浏览哪个素材,或使用实况预览来设置或调整你的抠像结果。 (5)抠像校准、颜色、视频位置和输入/输出设置,和载入虚拟演播室和他们输入的调整。后面的手册内容将详述这些性能。 2、输入和激活输入 下面介绍VS-3000的可用的虚拟演播室输入。 覆盖(i):覆盖是虚拟演播室的最上一层。覆盖层是视频素材或带Alpha透明的静止图形。他可以是简单的文本图形或更复杂的前景动画。 输入素材(ii):输入素材是想要抠像的主要视频素材。参考下面的其他情况的可选的输入素材。 背景(iii):背景是虚拟演播室的后面或底层。在背景层你可以有透明区来通过他显示其他的视频素材。 可选的输入素材(iv):这些素材用于填充背景层的透明区。取决于使用的虚拟演播室,

视频可以是素材B,素材C等。每个输入按钮的位置在界面的中下方,这些位置用于通过拖拉载入你的输入,并选择哪个输入是激活的用于处理。挨着输入的小的显示灯和按钮可显示状态; 红色 -在当前虚拟场景中是不可用的。 黄色- 在当前虚拟场景中是可选的 绿色- 在当前虚拟场景中被使用的 亮绿色- 激活输入素材 有用的提示:如果你双击一个文件夹的一个文件或把文件拖到(素材预览监视),将通过亮绿灯来指派哪个输入文件是“激活的”。 要切换激活素材,点击输入按钮或点击他的指示灯,或使用激活输入顺着向下移动到下一个输入的文件名,并点击。因为一些虚拟演播室可以有多于一个的输入–素材B,素材C 等–你可以顺着向下移动到素材B/C/等来改变用于编辑的激活素材。同样,如果你增加了多于一个的覆盖,使用覆盖1,2等,顺着向下移动来改变要激活的覆盖。 如果一个素材变为“激活”素材,将会发生几个改变。素材被载入到素材预览监示,文件名显示在下面的编辑框。 透明控制和滑块可以预览已是视频文件的素材。抠像,颜色,场景和输入标签可提供激活素材的持续的改变,因此请确认在改变设置前,你选择了正确的输入。 对输入文件的抠像设置,颜色设置,输入补偿,位置,补偿效果,场景位置和定位所做的调整,也应用于指定输入的新素材。你会看到不用重新设置,不同版本的类似镜头看起来的效果。在资源文件改变时,只有装饰点会丢失(如果有的话)。如果你在改变输入,灯光或抠像彩色背景改变的太明显,你将不得不在改变素材后重新调整抠像器。 有用的提示:还可以访问虚拟演播室里提供的输入。在浏览菜单下,点击显示输入,你将看到选择用户定义和合成定义。默认选择为用户定义,但是如果你选择合成定义,你将会看到虚拟演播室内容的颜色变了,或也可以被你自己的图形给替换。虚拟轨迹效果的图形不可以被替换,因为这个效果是摄像机位置的特殊信息所建立的,但是颜色是可以被处理的。 3、实况输入预览 在实际摄影时,运行VS-3000并浏览抠像的视频。在看抠像镜头时,可以设置灯光和摄像机位置。这样可以充分的提高抠像的质量。

虚拟演播室蓝箱设计

虚拟演播室蓝箱设计 蓝箱设计概述: 虚拟演播室系统是现代计算机图形处理技术与传统色键抠像技术相结合的产物,它可以把现场视频与计算机生成的场景影像,按照一定的透视关系实时无缝的进行合成,虚拟出真实演员置身于虚拟场景中的画面输出,以满足人们不断提高的欣赏要求。它的出现是对传统演播室技术的一次重大变革。在虚拟演播室系统中,跟踪技术和色键技术的好坏,是一个系统性能好坏的关键,但这些技术的应用均是建立在一个最基本的环境中,即我们所称的虚拟演播室的蓝箱。 大家知道,蓝箱是主持人活动的实际场景,及虚拟制作的根本依据。蓝箱的好坏,可能给后续的虚拟制作工作带来很大的影响。我频道拟于2001年购买一套二机位的RE-SET的IBIS虚拟演播室系统,在进行蓝箱的设计施工时,有一些心得和经验,在此与各位同行交流。 蓝箱+一个机位 虚拟后的效果

1、施工要求 在实际进行蓝箱设计时,首要考虑的问题就是蓝箱所在演播室的空间问题。目前各电视台的演播室多是一室多用,即同一个演播室由多个节目共用,也就有多个场景。这就要求在设计蓝箱时要充分考虑到其它场景的位置和灯光需求,不能使节目在录制时出现质量下降或穿帮现象。倘若演播室一室一用,专为虚拟演播室所用,就不存在这个问题。所以,建议最好是选用面积适合的小演播室作为虚拟系统专用。 其次,要根据虚拟系统的机位,来设计蓝箱的形状并计算其大小。也就是说,蓝箱的大小一定要能够满足摄像机的推拉摇移的范围要求,既不能过小而限制镜头的活动,又不能盲目加大蓝箱面积而导致造价的大幅度提高。 然后,就是要根据使用虚拟演播室制作节目的性质来规划蓝箱的大小。大家知道,新闻及小型访谈类的节目在录制时镜头一般较为简单,大多是以正面近景辅以少量侧面全景,且镜头固定,无需推拉摇移,主持人的位置也固定不动,这样对蓝箱的要求也就不高,只要顾及到侧面全景不穿即可,蓝箱可以做的较小。如果是录制文艺性节目,主持人不但会来回走动,且镜头的推拉摇移较多,变化较大。这就要求蓝箱要相对较大,给出足够的镜头活动空间。另外,在施工期期间,不能影响演播室正常的节目录制。 2、具体设计 ①确定位置与大小:根据我频道的实际条件,最终确定在250平米演播室的一角装修蓝箱,大小以70平米左右为宜。 ②蓝箱装修包括两个成90度夹角的立面和一个地台。立面与地台的夹角应大于90度(我们采用了立面向外倾斜10度的方案),以减少反射到主持人身上的蓝光;立面与地台间最好采取弧形过渡,这将更容易均匀布光,而且墙壁间也不会互相反射。圆滑的角落可以帮助减少灯光的明暗差异。地板应该足够大,以避免主持人的面光形成的强阴影打上立面,有时这会为制作带来一些麻烦。蓝箱整体设计如图1、图2所示。 1)确定制作工艺 制作工艺是蓝箱质量的保证,也就是说,蓝箱是否能顺利完成虚拟演播室的录制任务,制作工艺的好坏是关键之一。在制定制作工艺时,要从以下几个方面来考虑: ①制作材料 目前国内制作蓝箱的厂家主要使用两种材料,一种是玻璃钢,另一种就是木材。采用玻璃钢材料,优点就是材料强度高,几乎不会产生变形,且具有不可燃性。这样在制作前就无需对材料进行防火、防变形等预处理工作,大大节省了工期。缺点是造价过高,每平方米费用大约为2000元左右,这样如果建造一个大约100平方米左右的中型蓝箱,就需要花费20万元左右,这对于多数中小型电视台来说,都是一笔不小的开支。而如果采用木料的话,其造价大约为每平方米500元左右,是玻璃钢材料的1/4。但由于木料本身具有易燃、易变形等特点,所以在施工前期需进行大量的预处理工作,延长工期,增加了施工难度。目前国内各用户多采用木材来进行蓝箱的搭建。 ②蓝箱的搭建结构方式 蓝箱体积较大,搭建起来较为复杂,施工周期也较长。如果所有工作都在演播室中完成,势必会影响演播室的正常使用。所以我们建议蓝箱整体结构采用积木式拼接方式,即将蓝箱整体分为若干部分,先将每一部分在演播室外施工场地进行加工完成,最后将各部分在演播室中通过榫接等方式结合在一起,形成整体结构。采用这种方式的好处就是缩短室内施工时间,而且预先单独制作球形区域和各弧形区域,也较容易保证其成型。但这样对施工者的施工水平要求很高,在整体拼接时应能进行准确的校正,保证由多个部分组成的各平面、弧面、球面的平滑过渡性。我们的蓝箱所采用的积木式结构将整个蓝箱分为二十多个部分进行分别制作,最后再进行整体拼装。 3、选材的预处理 根据自身目前的预算状况,我们选择了使用木料搭建蓝箱,所用蓝漆为国产阻燃漆。由于蓝箱搭