TimeQuest快速入门实例及时序查看

1.在quartus中对设计进行时序分析

2.1TimeQuest 工具

Quartus? II TimeQuest Timing Analyzer是一个功能强大的ASIC型时序分析工具,能够以工业标准方法论来约束,分析和报告用户设计中所有逻辑的时序性能。这个工具是一个严格的静态工具,使用时不需要搭建硬件环境及进行调试。本节将介绍如何使用Quartus II TimeQuest Timing Analyzer工具的图形化功能来约束,分析及报告设计中的时序结果。

使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时间。我们通过后缀名为sdc(Synopsys Design Constraints)的文件来指定时序要求,然后The Quartus II Fitter将优化逻辑布局等来满足我们的时序要求。

在时序分析过程中,Quartus II TimeQuest Timing Analyzer分析设计中的每一条时序路径,计算每条路径的延迟,检查是否存在时序违例,并且报告时序结果。一旦发现时序违例,可以精确定位到违例路径的时序细节,然后用户约束它以纠正违例。如果时序分析没有报告违例,那么恭喜你,在这个器件中的逻辑行为将与你的设计意图一致。

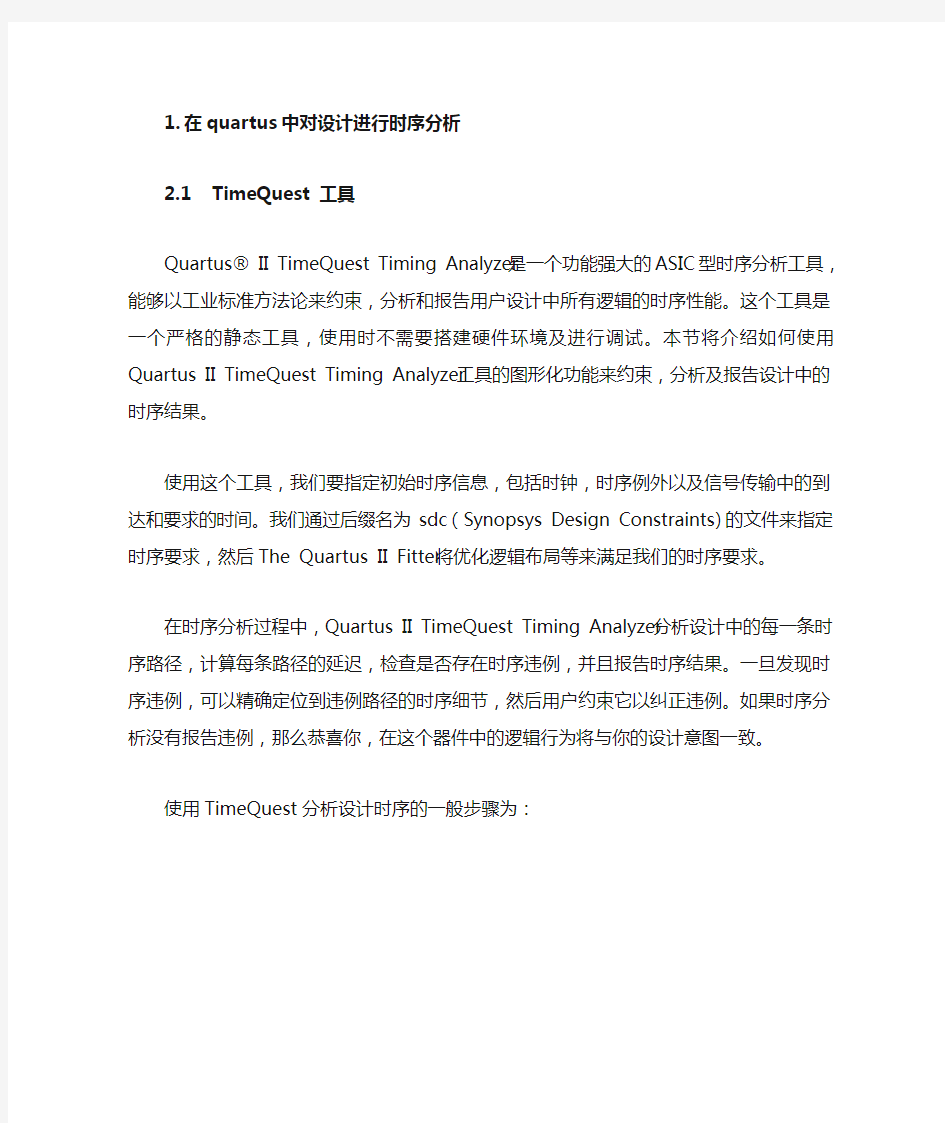

使用TimeQuest分析设计时序的一般步骤为:

图使用TimeQuest分析设计时序的一般步骤第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。第二次编译的时序需要把包含指定时序要求的文件(后缀为sdc 的文件)添加到工程文件中执行编译,这样工具就能够按照我们的时序要求来进行映射了。

2.2timequest快速入门示例

下面我们按照altera公司所给的timequest快速入门教程示例来讲解该时序分析工具的大致用法。使用的工具是目前使用最广泛的quartusII9.1版本

提供的TimeQuest工具。

首先我们打开quartus工具的例程。在quartus工具中选择File下的open project,选择qdesigns目录下的fir_filter工程。打开后我们能够看到如图示的模块结构图。

图qdesigns目录下的FIR例程

这个工程实现了一个FIR模块。其输入端口为clk,clkx2,reset,newt,d[7:0];输出端口为follow,yvalid,yn_out[7:0]。clkx2这个时钟是乘法器输出数据的寄存器触发时钟,而clk是整个模块其余部分的系统时钟。

对这个设计进行时序分析,首先需要在软件中设置timequest作为默认的时序分析工具。以下为设置方法:在Assignments 菜单中,点击Settings,Settings 对话框出现后,在Category列表下选择Timing Analysis Settings,开启Use TimeQuest Timing Analyzer during compilation,选择OK。

设置好后,执行Start Analysis & Synthesis,对项目进行编译。这一步建立了一个post-map的数据库,给给时序分析工具使用。当然也可以给post-fit数据库,但是对于时序预估,post-map已经足够了,而且运行的时间会更短。

在tools菜单下,选择TimeQuest Timing Analyzer,启动TimeQuest工具。此时自动打开的是当前的工程。当出现"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?" 对话框时,选择NO。

图timequest界面

在Netlist菜单下点击Create Timing Netlist.在出现的对话框的Input netlist, 选择Post-Map. 点击OK。

完成这些步骤之后,我们就可以开始对设计指定时序上的要求了。在软件界面的constraints菜单下,我们能够看到当前版本软件的所有可以指定的约束。这里简要解释一下他们的功能。

第一部分是关于时钟的。Create clock是用来指定系统中存在的时钟的信息,包括时钟的频率,占空比等。可以指定多个时钟,或者给一个时钟指定多个频率分别进行时序分析。Create generated clock是指定由输入时钟信号在FPGA内部生成的时钟,通常需要指定生成这个时钟的时钟源及生成关系。Set clock latency和set clock uncertainty是指定时钟的输入延时以及时钟信号的不确定性,时钟间隙或者时钟转移的。Set clock group是将设计中互斥的时钟放在不同的group里面,互斥的时钟可能是不同时钟域的,也可能是同一个时钟信号进行分析时指定了2种频率各自分析。Remove clock是将之前指定的时钟从设计中移除。

第二部分是关于输入输出端口的。只有约束了输入输出的时序,才是一个完整严谨的约束。否则有些寄存器的时序无法进行分析。

第三部分是一些时序的例外。包括False Path(忽略路径),Multicycle path(多周期路径),最大最小路径延时等。

菜单的第四部分支持从QSF 文件格式的标准时序分析器约束转换为TimeQuest 分析器的SDC 文件格式,将约束写入SDC文件,或者从SDC文件中读

出时序信息。

图TimeQuest指定时序约束的界面

接下来我们对FIR的设计指定时序要求。首先是时钟。

FIR这个设计存在2个时钟,我们需要对时钟特性进行指定。例子里面这两个时钟的要求为:

Clk频率50 MHz,50/50占空比;clkx2为100 MHz,占空比是60/40。在如下图所示的creat clk对话框中,可以指定时钟名称,Period是周期,默认单位ns;波形不填默认占空比50%,上升沿在前,否则时钟按照你指定的边沿时刻跳变,;targets 用来将指定的时钟与设计的端口进行匹配,最下面是显示将要添加进入SDC文件

的命令行。按照图中的示例指定clk与clkx2分别为50MHz和100MHz。

图指定设计中的时钟

添加了时钟其实就可以在tasks框下的diagnosis里面快速查看时序报告了。依次双击每一项,左上角report框中会出现相应的报告。黑色字体的为时序正确的报告项,红色字体表示该项存在问题。如下图所示,点击红色报告会出现问题的原因。从图中可以看到,问题是因为有10个没有约束的输入端口,涉及了79条输入端口路径,以及10个没有约束的输出端口,涉及10条输出端口路径。也就是说,时序工作认为一个完整的约束,每一个端口,每一条路径都需要指定时序要求,否则时序分析无法覆盖所有的触发器。

图快速报告时序结果及显示时序异常

在clock transfers报告下,可以看到时钟转移路径。FIR设计中不需要分析从clk 到clkx2的路径,因为他们是虚假路径。因此需要设置false path。在clk到clkx2路径上右击鼠标,选择set false path。之后工具背景变成淡黄色,出现out of data

水印。整个分析结果需要update一次。

设置了时钟的约束,可以得到分析报告,还可以将指定的时序要求写入SDC 文件中。双击Task窗口下的Write SDC File,填写自定义的文件名称,就可以将之前设置的约束写入后缀名的.sdc的文件中。之后在TimeQuest的File目录下选择Open SDC文件,打开刚才自己命名的文件,就能够看到文本形式的时序约束信息,还包括使用的期间,创立工程的日期等。这个SDC文件将添加到工程中重新执行编译,以约束映射及布局布线。

图SDC文件的内容

除了指定时钟信号,完整的时序约束还需要Set input和output delay,这样可以指定外部器件以及板级的时序。如果设定了这两项,TimeQuest将对整个系统执行静态时序分析。

设置输入输出的时序可以将信息写入新的SDC文件,也可以在之前的文件中继续添加时序信息。

在Constraints菜单下单击Set Input Delay,出现相应对话框。按照如下输入,其余默认:

Clock name: clk

Delay value: 2

Targets: [get_ports {d[0] d[1] d[2] d[3] d[4] d[5] d[6] d[7] newt reset}] 在Constraints菜单下单击Set Input Delay,出现相应对话框。按照如下输入:Clock name: clk

Delay value: 1.5

Targets: [get_ports {yn_out[0] yn_out[1] yn_out[2] yn_out[3] yn_out[4] yn_out[5]

yn_out[6] yn_out[7] yvalid follow}]

这里的约束的意思是,将输入信号的到达触发器端口时间相对于时钟clk 的有效边沿的延时设置为2ns。将输出端口的数据要求时间与给定时钟的延时设

置为1.5ns。这样再生成Unconstrained Paths Summary report,就可以看到未约束的路径数为0。也就是所有的路径都得到了约束。

2.3查看时序报告

添加了完整约束后将约束写入SDC文件。这种我们就可以查看每一条指定的路径具体的时序结果了,当然也可以看到最差的时序路径是哪一条。这里的报告非常多,甚至包括很多本书作者一时无法解释的报告项,读者需要自行尝试锻炼。

这里仅介绍customer report 下面的timing项的使用方法时序报告的理解。选择了customer report 下面的timing,会出现如下对话框:

图report customer timing对话框

在这个对话框中,用户可以自行指定需要报告的时序路径,包括时钟域的,也可以指定特定node,还可以选择分析的是建立时间,还是保持,恢复以及移除时间;可以选择一次报告的时序路径数目等。点击report timing之后,工具会将

相应数量的时序路径按照时序余量由小到大排列出来。如果存在时序违例,特定的路径将被标红并且放到列表的最前。

在出现的报告之中,有3个主要的框。上面的一个框将所有路径结果以表格的形式列出。下面的2个一模一样的对话框显示的是表格中选中路径的时序结果,2个显示框是为了方便对照着查看该路径的时序。

图特定路径时序结果报告

这两个一样的对话框有4个子目录可以看到path summary,statistics,data path,以及waveform。Path summary给出了data arrival time和data required time 的和,以及对于的时序裕度;statistics跟data path分别给出详细的数据要求的路径时间关系与数据实际路径各部分延时,从中可以看到数据传输中经过了些什么单元,各部分的延时是多少。最后的waveform则是以波形图的方式将数据建立或者保持关系与实际情况进行了分析。下面我们主要介绍如何认识这个波形图。

图时序报告中的波形图

图中的波形是FIR中指定的一条分析建立时间关系的数据路径示意图。Launch clock是第一级触发器触发的时钟,以其有效边沿作为这个图中时序分析的时刻起点,即0时刻。Latch clock是第二级触发器接收数据的时钟,与launch clock一样周期是20ns。所以建立时钟的关系是20ns。图中的data arrival time是从0时刻开始,数据到达第二级触发器的时间,数据触发时钟的延时2.277ns,又经过data delay 的延时(包括第一节所说的Tco和Tdelay)为8.383ns,所以数据在10.66ns时刻到达第二级寄存器。而第二级寄存器相应的时钟边沿时间是20ns+2.277ns的时钟延时,要求的数据在第二级寄存器有效沿之前uTsu到来,uTsu是-0.029,所以要求数据在20.248ns时刻之前到来。实际数据是10.66ns就到来了,计算出来的裕度是data required time减去data arrival time,结果是绿色所指示的11.588ns。

除了图中的建立时间以外,读者需要自己尝试对照图中的波形理解保持时间,恢复时间以及移除时间检查的是哪些规则。读者也需要多使用TimeQuest工具下的各种报告,来分析你设计的系统能够在多高的频率运行而不产生时序错误。

TimeQuest工具随着Quartus 软件版本提升相应的变动也不小。里面一些不常用的约束及报告,建议读者阅读Altera官方教程《The Quartus II TimeQuest Timing Analyzer》,从中查找应用。

触发器和时序逻辑电路习题答案

第21章 触发器和时序逻辑电路 191、触发器按其工作状态是否稳定可分为( b )。 (a)RS 触发器,JK 触发器,D 触发器,T 触发器; (b)双稳态触发器,单稳态触发器,无稳态触发器; (c)主从型触发器,维持阻塞型触发器。 192、逻辑电路如图所示,当A=“1”时,基本RS 触发器( c )。 (a)置“1”; (b)置“0”; (c)保持原状态。 ≥1A ""1R D Q Q S D 193、 逻辑电路如图所示,分析C ,S ,R 的波形,当初始状态为“0”时,输出Q 是“0”的瞬间为( c )。 (a)1t ; (b)2t ; (c)3t 。 C S R t 1t 2t 3S C R D R S D Q Q 194、 某主从型JK 触发器,当J=K=“1”时,C 端的频率f=200Hz ,则Q 的频率为( c )。 (a)200Hz ; (b)400Hz ; (c)100Hz 。 195、逻辑电路如图所示,当A=“1”时,C 脉冲来到后JK 触发器( a )。 (a)具有计数功能; (b)置“0”; (c)置“1”。 ≥1 A J C R D K S D Q Q "" 1""1 196、 逻辑电路如图所示,A=“0”时,C 脉冲来到后D 触发器( b )。 (a)具有计数器功能; (b)置“0”; (c)置“1”。

D C Q Q & A 197、逻辑电路如图所示,分析C 的波形,当初始状态为“0”时,输出Q 是“0”的瞬间为( a )。 (a) 1t ; (b)2t ; (c)3t 。 D C Q Q C t 1t 2t 3 198、逻辑电路如图所示,它具有( a )。 (a)D 触发器功能; (b)T 触发器功能; (c)T'触发器功能。 J C R D K S D Q Q 1 199、逻辑电路如图所示,它具有( b )。 (a)D 触发器功能; (b)T 触发器功能; (c)T'触发器功能。 J C R D K S D Q Q 200、时序逻辑电路与组合逻辑电路的主要区别是( c )。 (a)时序电路只能计数,而组合电路只能寄存; (b)时序电路没有记忆功能,组合电路则有; (c)时序电路具有记忆功能,组合电路则没有。 201、寄存器与计数器的主要区别是( b )。 (a)寄存器具有记忆功能,而计数器没有; (b)寄存器只能存数,不能计数,计数器不仅能连续计数,也能存数; (c)寄存器只能存数,计数器只能计数,不能存数。 202、移位寄存器与数码寄存器的区别是( a )。 (a)前者具有移位功能,后者则没有; (b)前者不具有移位功能,后者则有; (c)两者都具有移位功能和计数功能。

集成计数器及寄存器的运用 实验报告

电子通信与软件工程 系2013-2014学年第2学期 《数字电路与逻辑设计实验》实验报告 --------------------------------------------------------------------------------------------------------------------- 班级: 姓名: 学号: 成绩: 同组成员: 姓名: 学号: --------------------------------------------------------------------------------------------------------------------- 一、 实验名称:集成计数器及寄存器的运用 二、实验目的: 1、熟悉集成计数器逻辑功能与各控制端作用。 2、掌握计数器使用方法。 三、 实验内容及步骤: 1、集成计数器74LS90功能测试。74LS90就是二一五一十进制异步计数器。逻辑简图为图8、1所示。 四、 五、 图8、1 六、 74LS90具有下述功能: ·直接置0(1)0(2)0(.1)R R ,直接置9(S9(1,·S,.:,=1) ·二进制计数(CP 、输入QA 输出) ·五进制计数(CP 2输入Q D Q C Q B 箱出) ·十进制计数(两种接法如图8.2A 、B 所示) ·按芯片引脚图分别测试上述功能,并填入表 8、1、表8、2、表8、3中。

图8、2 十进制计数器 2、计数器级连 分别用2片74LS90计数器级连成二一五混合进制、十进制计数器。 3、任意进制计数器设计方法 采用脉冲反馈法(称复位法或置位法)。可用74LS90组成任意模(M)计数器。图8、3就是用74LS90实现模7计数器的两种方案,图(A)采用复位法。即计数计到M异步清0。图(B)采用置位法,即计数计到M一1异步置0。 图8、3 74LS90 实现七进进制计数方法 (1)按图8、3接线,进行验证。 (2)设计一个九进制计数器并接线验证。 (3)记录上述实验的同步波形图。 四、实验结果:

数字钟设计报告——数字电路实验报告

数字钟设计实验报告 专业:通信工程 姓名:王婧 班级:111041B 学号:111041226

数字钟的设计 目录 一、前言 (3) 二、设计目的 (3) 三、设计任务 (3) 四、设计方案 (3) 五、数字钟电路设计原理 (4) (一)设计步骤 (4) (二)数字钟的构成 (4) (三)数字钟的工作原理 (5) 六、总结 (9) 1

一、前言 此次实验是第一次做EDA实验,在学习使用软硬件的过程中,自然遇到很多不懂的问题,在老师的指导和同学们的相互帮助下,我终于解决了实验过程遇到的很多难题,成功的完成了实验,实验结果和预期的结果也是一致的,在这次实验中,我学会了如何使用Quartus II软件,如何分层设计点路,如何对实验程序进行编译和仿真和对程序进行硬件测试。明白了一定要学会看开发板资料以清楚如何给程序的输入输出信号配置管脚。这次实验为我今后对 EDA的进一步学习奠定了更好的理论基础和应用基础。 通过本次实验对数电知识有了更深入的了解,将其运用到了实际中来,明白了学习电子技术基础的意义,也达到了其培养的目的。也明白了一个道理:成功就是在不断摸索中前进实现的,遇到问题我们不能灰心、烦躁,甚至放弃,而要静下心来仔细思考,分部检查,找出最终的原因进行改正,这样才会有进步,才会一步步向自己的目标靠近,才会取得自己所要追求的成功。 2

二、设计目的 1.掌握数字钟的设计方法。 2熟悉集成电路的使用方法。 3通过实训学会数字系统的设计方法; 4通过实训学习元器件的选择及集成电路手册查询方法; 5通过实训掌握电子电路调试及故障排除方法; 6熟悉数字实验箱的使用方法。 三、设计任务 设计一个可以显示星期、时、分、秒的数字钟。 要求: 1、24小时为一个计数周期; 2、具有整点报时功能; 3、定时闹铃(未完成) 四、设计方案 一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器和定时器组成。干电路系统由秒信号发生 3

iPhone手机使用手册—“照片”操作说明

查看照片和视频删除照片和视频幻灯片显示共享照片和视频拷贝并粘贴照片和视频从电子邮件信息、彩信或网页存储图像将照片指定给联系人墙纸常见问题 iPhone手机使用手册—“照片”操作说明 iPhone 可让您随身携带照片,从而使您可以与家人、朋友和同事共享它们。在 iPhone 上查看照片,或者通过 AirPlay (IOS4.2)在使用 Apple TV 的电视机上查看它们。您可以从电脑同步照片和视频、查看用IPHONE拍摄的照片和视频、将照片用做墙纸,或者指定照片以识别来电的联系人。您还可以用电子邮件和彩信发送照片和视频,将照片和视频上传到MobileMe 画廊,以及打印照片。 【注】视频功能仅在 iPhone 3GS或新款机型上可用。 一、与电脑同步照片和视频 iTunes 可以使照片和视频与以下应用程序来同步: Mac: iPhoto 4.0.3(苹果电脑的图片管理软件,同步视频需要iPhoto 6.0.6或更新版本),或者 Aperture(apple公司图片处理软件,仅限照片) PC: Adobe Photoshop Elements 8.0或更高版本(仅限照片)。 您还可以从电脑上包含图像的任何文件夹同步照片和视频。 创建 iPhone 版本的视频 iPhone 支持 H.264 和 MPEG-4 视频格式(带 AAC 音频)。如果在将视频同步到 iPhone 时遇到问题,您可以使用 iTunes 创建一个 iPhone 版本的视频。 1、将视频拷贝到您的 iTunes 资料库。 2、在 iTunes 中,从“资料库”列表中选择“影片”,然后选择您想要同步的视频。 3、选取“高级”>“创建 iPod 或 iPhone 版本”。 二、查看照片和视频 您可以在“照片”中浏览从电脑上同步来的照片。您还可以查看使用 iPhone 的内建摄像头拍摄的照片和录制的视频。 使用 iPhone 拍摄的照片和视频、从电脑同步的照片和视频,或者从电子邮件或彩信存储的照片和视频可在“照片”中查看。如果使照片与 iPhoto 8.0(iLife 09 的一部分)或更高版本同步,则可以按您所识别的事件和面孔查看您的照片和视频。如果标记了位置数据,您还可以看到照片和视频的拍摄地点。 操作步骤: 1、在“照片”中,轻按相簿。轻按屏幕底部的按钮,以按事件、面孔或地点(如果适用)

数字电路实验计数器的设计

数字电路与逻辑设计实验报告实验七计数器的设计 :黄文轩 学号:17310031 班级:光电一班

一、实验目的 熟悉J-K触发器的逻辑功能,掌握J-K触发器构成异步计数器和同步计数器。 二、实验器件 1.数字电路实验箱、数字万用表、示波器。 2.虚拟器件: 74LS73,74LS00, 74LS08, 74LS20 三、实验预习 1. 复习时序逻辑电路设计方法 ①根据设计要求获得真值表 ②画出卡诺图或使用其他方式确定状态转换的规律 ③求出各触发器的驱动方程 ④根据已有方程画出电路图。 2. 按实验内容设计逻辑电路画出逻辑图 Ⅰ、16进制异步计数器的设计 异步计数器的设计思路是将上一级触发器的Q输出作为下一级触发器的时钟信号,置所有触发器的J-K为1,这样每次到达时钟下降沿都发生一次计数,每次前一级 触发器从1变化到0都使得后一级触发器反转,即引发进位操作。 画出由J-K触发器组成的异步计数器电路如下图所示:

使用Multisim仿真验证电路正确性,仿真图中波形从上到下依次是从低位到高位 触发器的输出,以及时钟信号。: 可以看出电路正常执行16进制计数器的功能。 Ⅱ、16进制同步计数器的设计 较异步计数器而言,同步计数器要求电路的每一位信号的变化都发生在相同的时间点。

因此同步计数器各触发器的时钟脉冲必须是同一个时钟信号,这样进位信息就要放置在J-K 输入端,我们可以把J-K端口接在一起,当时钟下降沿到来时,如果满足进位条件(前几位触发器输出都为1)则使JK为1,发生反转实现进位。 画出由J-K触发器和门电路组成的同步计数器电路如下图所示 使用Multisim仿真验证电路正确性,仿真图中波形从上到下依次是从低位到高位触发器的输出,计数器进位输出,以及时钟信号。:

91手机助手For iPhone(苹果)详细使用教程

91手机助手For iPhone详细使用教程 91手机助手(iPhone版)是由网龙公司开发的一款PC端使用的iPhone手机第三方管理工具,以其美观的界面,方便的操作为一直以来iPhone手机没有方便的配套PC端使用工具提供了一套完美的解决方案,给您带来全新的操作体验。 91手机助手For iPhone 点击下载 一、91手机助手For iPhone版简介 91手机助手(iPhone版)是由网龙公司开发的一款PC端使用的iPhone手机第三方管理工具,以其美观的界面,方便的操作为一直以来iPhone手机没有方便的配套PC端使用工具提供了一套完美的解决方案,给您带来全新的操作体验。 iPhone版手机助手功能列表: 固件支持:iPhone 1.X | 2.X | 3.X |4.X 固件 ; 操作系统:支持32位和 64位的Windows XP / Vista / Windows 7 资料管理:联系人管理、电脑收发管理短信、定制日程、管理任务 媒体娱乐:轻松编辑设置手机铃声、手机主题、壁纸 阅读管理:几十万免费电子书在线/本地化管理;新闻RSS订阅等 软件管理:本地软件管理;海量手机软件免费安装 系统管理:系统信息查阅;进程管理;注册表管理等 备份还原:备份还原短信、通话记录、主题铃声、联系人等十几种信息 为什么要使用91手机助手? FREE/免费-都是免费的,91手机助手免费,软件游戏电子书也是免费的 轻松管理智能手机-还有什么比把智能机当傻瓜机玩更开心的呢? 海量资源尽情下载使用-真的是海量,几万手机软件,几十万电子书 完美个性体验-从界面到功能打造最安全最轻松的智能手机PC端管理工具

第21章习题 触发器和时序逻辑电路

第21章时序逻辑电路 S13101B 在逻辑电路中,任意时刻的输出状态仅取决于该时刻输入信号的状态,而与信号作用前电路的状态无关,这种电路称为。因此,在电路结构上一般由 组合而成。 解: 组合逻辑电路,门电路 S13102B 在任何时刻,输出状态仅仅决定于同一时刻各输入状态的组合,而与电路以前所处的状态无关的逻辑电路称为,而若逻辑电路的输出状态不仅与输出变量的状态有关,而且还与系统原先的状态有关,则称其为。 解: 组合逻辑电路,时序逻辑电路。 S13102I 在同步计数器中,各触发器的CP输入端应接时钟脉冲。 解: 同一 S13201B 有四个触发器的二进制计数器,它的计数状态有( )。 A. 8 B. 16 C. 256 D. 64 解: B S13104B 个逻辑电路,如果某一给定时刻t的输出不仅决定于该时刻t的输入,而且还决定于该时刻前电路所处的状态,则这样的电路称为电路。 解: 时序 S13105B 一个逻辑电路,如果某一给定时刻t的稳态输出仅决定于该时刻的输入,而与t前的状态无关,则这样的电路称为电路。 解: 组合 S13106B 按触发器状态更新方式划分,时序电路可分为和两大类。 解: 同步、异步 S13108B 计数器中有效状态的数目,称为计数器的。 解: 模或长度

S13106N 如图所示电路是 步 进制计数据。 解: 异,十六 S13107N 如图所示电路是 步,长度为 的 法计数器。 解: 异,8,加 S13108N 在如图所示电路中,若将第二级、第三级触发器的CP 改接在21Q Q 、上,则该电路是 步,长度为 的 法计数器。 解: 异,8,减 S13110N 如图所示电路是 步,长度为 的 法计数器。 解: 异,4,加 S13111N 如图所示电路是 步,长度为 的 法计数器。 解: 异,8,减

实验五--时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告 一、实验目的 1.掌握同步计数器设计方法与测试方法。 2.掌握常用中规模集成计数器的逻辑功能和使用方法。 二、实验设备 设备:THHD-2型数字电子计数实验箱、示波器、信号源 器件:74LS163、74LS00、74LS20等。 三、实验原理和实验电路 1.计数器 计数器不仅可用来计数,也可用于分频、定时和数字运算。在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。 2.(1) 四位二进制(十六进制)计数器74LS161(74LS163) 74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表5.1。 74LSl63是同步置数、同步清零的4位二进制加法计数器。除清零为同步外,其他功能与74LSl61相同。二者的外部引脚图也相同,如图5.1所示。 表5.1 74LSl61(74LS163)的功能表 清零预置使能时钟预置数据输入输出 工作模式R D LD EP ET CP A B C D Q A Q B Q C Q D 0 ××××()××××0 0 0 0 异步清零 1 0 ××D A D B D C D D D A D B D C D D同步置数 1 1 0 ××××××保持数据保持 1 1 ×0 ×××××保持数据保持 1 1 1 1 ××××计数加1计数3.集成计数器的应用——实现任意M进制计数器 一般情况任意M进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。第二类是由集成二进制计数器构成计数器。第三类是由移位寄存器构成的移位寄存型计数器。第一类,可利用时序逻辑电路的设计方法步骤进行设计。第二类,当计数器的模M较小时用一片集成计数器即可以实现,当M较大时,可通过多片计数器级联实现。两种实现方法:反馈置数法和反馈清零法。第三类,是由移位寄存器构成的移位寄存型计数器。 4.实验电路: 十进制计数器 同步清零法 同步置数法

最新苹果iPad2使用说明书完整超详细

苹果iPad2平板电脑新手使用教程 有需求请下载,因为超详细 最近关于苹果最火的无非就是iPad2的发售,之前用过iPhone的朋友对iPad2的使用还算了解,但也有没用iPhone但入手iPad2的朋友,这样对苹果官方的套件iTunes就不是很熟悉了,小编有幸入手了一台iPad2,这里给刚入手iPad2但又不是很熟悉不太会用的朋友一个简单的初级入门iPad2使用教程。 什么是iTunes iTunes是苹果所有移动设备的PC套件,不管是iPod、iTouch、iPhone还是今天要说的iPad2,都要使用iTunes 来安装应用程序。 下载完毕后,安装好下载的iTunes,把iPad2用数据线连上电脑,iTunes就会识别了。 同步程序 因为现在iPad2的越狱还没有高人放出,大家只能花钱购买正版或者是免费的试玩版的游戏或者软件了。 注册好了之后,找到你喜欢的一个应用程序,比如我选的这个 点开之后是这个界面,然后点击这里的免费字样

然后就会显示正在下载 下载好了之后,在应用程序选项卡,就会看到刚刚下载的游戏。 这时点击设备中的应用程序选项卡,然后选中要同步的程序

接着点击右下角的同步字样,等待同步完毕即可。 这样就同步完毕之后就会在iPad2的桌面上看到刚刚下载的网球游戏了,QQ等其他一些免费的软件也是一样的道理。 下面是我用iPad2专用的QQ上的一些截图,看着确实很过瘾。

同步音乐 同步音乐其实也是很简单的,首先先把你电脑中要同步到iPad2中的音乐添加到iPad2的资料库中。 这样iPad2中的资料库的音乐标签里就会显示 然后找到设备中的音乐标签,选中要同步的音乐,

数字钟设计报告——数字电路实验报告

. 数字钟设计实验报告 专业:通信工程 :王婧 班级:111041B 学号:111041226 .

数字钟的设计 目录 一、前言 (3) 二、设计目的 (3) 三、设计任务 (3) 四、设计方案 (3) 五、数字钟电路设计原理 (4) (一)设计步骤 (4) (二)数字钟的构成 (4) (三)数字钟的工作原理 (5) 六、总结 (9) 1

一、前言 此次实验是第一次做EDA实验,在学习使用软硬件的过程中,自然遇到很多不懂的问题,在老师的指导和同学们的相互帮助下,我终于解决了实验过程遇到的很多难题,成功的完成了实验,实验结果和预期的结果也是一致的,在这次实验中,我学会了如何使用Quartus II软件,如何分层设计点路,如何对实验程序进行编译和仿真和对程序进行硬件测试。明白了一定要学会看开发板资料以清楚如何给程序的输入输出信号配置管脚。这次实验为我今后对 EDA的进一步学习奠定了更好的理论基础和应用基础。 通过本次实验对数电知识有了更深入的了解,将其运用到了实际中来,明白了学习电子技术基础的意义,也达到了其培养的目的。也明白了一个道理:成功就是在不断摸索中前进实现的,遇到问题我们不能灰心、烦躁,甚至放弃,而要静下心来仔细思考,分部检查,找出最终的原因进行改正,这样才会有进步,才会一步步向自己的目标靠近,才会取得自己所要追求的成功。 2

二、设计目的 1.掌握数字钟的设计方法。 2熟悉集成电路的使用方法。 3通过实训学会数字系统的设计方法; 4通过实训学习元器件的选择及集成电路手册查询方法; 5通过实训掌握电子电路调试及故障排除方法; 6熟悉数字实验箱的使用方法。 三、设计任务 设计一个可以显示星期、时、分、秒的数字钟。 要求: 1、24小时为一个计数周期; 2、具有整点报时功能; 3、定时闹铃(未完成) 四、设计方案 一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器和定时器组成。干电路系统由秒信号发生器、“时、 3

第13章触发器及时序逻辑电路习题汇总

第十三章触发器和时序逻辑电路 13.1重点内容提要 时序逻辑电路由组合逻辑电路和具有记忆作用的触发器构成。时序逻辑电路的特点是:其输出不仅仅取决于电路的当前输入,而且还与电路的原来状态有关。 1.双稳态触发器 双稳态触发器的特点: 1).有两个互补的输出端Q 和Q。 2).有两个稳定状态。“1”状态和“0” 状态。通常将Q = 1和Q= 0 称为“1”状态,而把Q = 0和Q = 1称为“0” 状态。 3).当输入信号不发生变化时,触发器状态稳定不变。 4).在一定输入信号作用下,触发器可以从一个稳定状态转移到另一个稳定状态。 按其逻辑功能,触发器可分为:RS触发器,JK触发器、D触发器、T触发器和T’触发器。 各时钟控制触发器的逻辑符号和逻辑功能见表13.1.1: 把一种已有的触发器通过加入转换逻辑电路,可以转换成为另一种功能的触发器。 2.同步时序逻辑电路的分析

同步时序逻辑电路的分析步骤如下: 1.由给定的逻辑电路图写出下列各逻辑方程式: (1)各触发器的特性方程。 (2)各触发器的驱动方程。 (3)时序电路的输出方程。 2.将驱动方程代入相应触发器的特性方程,求得电路的状态方程(或次态方程)。 3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态转换图或时序图。 4.根据电路的状态转换图说明该时序逻辑电路的逻辑功能。 3.典型的时序逻辑电路 在数字系统中,最典型的时序逻辑电路是寄存器和计数器。 1)寄存器 寄存器是用来存储数据或运算结果的一种常用逻辑部件。寄存器的主要组成部分是在双稳态触发器基础上加上一些逻辑门构成。按功能分,寄存器分为数码寄存器和移位寄存器。移位寄存器是既能寄存数码,又能在时钟脉冲的作用下使数码向高位或向低位移动的逻辑功能部件。通常有左移寄存器、右移寄存器、双向移位寄存器和循环移位寄存器。移位寄存器可实现数据的串行、并行转换,数据的运算和数据的处理等。 2)计数器 计数器是一种对输入脉冲数目进行计数的时序逻辑电路,被计数的脉冲信号称为计数脉冲。计数器除计数外,还可以实现定时、分频等,在计算机及数字系统中应用极广。 计数器种类很多,通常有如下不同的分类方法。 (1)按逻辑功能可分为加法计数器、减法计数器和可逆计数器。 (2)按计数进制可分为二进制计数器、十进制计数器和任意进制计数器等。 (3)按工作方式可分为同步计数器和异步计数器。 集成电路74161型四位同步二进制计数器 图13.1.1为74161型四位同步二进制可预置计数器的外引线排列图及其逻辑符号,其中D R 是异步 (a ) 外引线排列图 (b ) 逻辑符号 图13.1.1 74161型四位同步二进制计数器 清零端,LD 是预置数控制端,0123A A A A 是预置数据输入端,EP 和ET 是计数控制端,Q 3Q 2Q 1Q 0是计数输出端,RCO 是进位输出端。74161型四位同步二进制计数器具有以下功能: ① 异步清零。D R =0时,计数器输出被直接清零,与其他输入端的状态无关。 ② 同步并行预置数。在D R =1条件下,当LD =0且有时钟脉冲CP 的上升沿作用时,3A 、2A 、1A 、0A 输入端的数据3d 、2d 、1d 、0d 将分别被3Q 、2Q 、1Q 、0Q 所接收。 ③ 保持。在D R LD ==1条件下,当=?EP ET 0,不管有无CP 脉冲作用,计数器都将保持原有状态

计数器的设计实验报告

计数器的设计实验报告 篇一:计数器实验报告 实验4 计数器及其应用 一、实验目的 1、学习用集成触发器构成计数器的方法 2、掌握中规模集成计数器的使用及功能测试方法二、实验原理 计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。 计数器种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等等。目前,无论是TTL还是

CMOS集成电路,都有品种较齐全的中规模集成计数器。使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。 1、中规模十进制计数器 CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。 图5- 9-1 CC40192引脚排列及逻辑符号 图中LD—置数端CPU—加计数端CPD —减计数端CO—非同步进位输出端BO—非同步借位输出端 D0、D1、D2、D3 —计数器输入端 Q0、Q1、Q2、Q3 —数据输出端CR—清除端 CC40192的功能如表5-9-1,说明如下:表5-9-1 当清除端CR为高电平“1”时,计数

器直接清零;CR置低电平则执行其它功能。当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。 当CR为低电平,LD为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421 码十进制加、减计数器的状态转换表。加法计数表5-9- 减计数 2、计数器的级联使用 一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。 同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。 图5-9-2是由CC40192利用进位

苹果Mac操作系统使用教程

Mac使用教程 Mac使用教程(基础篇) 如果您是计算机新手,或只是需要一些教学课程,帮助您将Mac的功能发挥到淋漓尽致,那么您就来对地方了。我们将带领您以最有效率的方式使用Mac。无论您想知道如何操作使用Mac桌面(或只是要知道什么是桌面)、找出连接打印机、iPod、数字相机或其他设备的方式、搜寻电子邮件和Internet、认识各种功能的操作方式、学习如何使用Mac随附的软件,或在无法得心应手地操作时需要协助指点,这种种问题的答案,我们都为您准备好了。准备好了吗?请把您的问题告诉我们:第一课:Mac基础操作如果您是初次接触计算机,才刚开始学习各项操作技巧,不用紧张,其实操作Mac不过就是靠一连串的点选动作。这一课将为您介绍与计算机界面互动的基本方式,也会教您如何在Mac上完成一些基本工作。让我们进入课程内容吧! 第一次使用Mac吗?那就从学习Mac基础操作开始吧!点点选选轻松操作如果您对Mac桌面和Finder视窗的操作不是很熟练,建议您从这里开始学起,如果已经很熟悉了,可以直接跳到“建立帐号”那部分。我们先来谈谈计算机操作的基本技巧。移动鼠标时(iBook或PowerBook的使用者是以手指在触

控式轨迹板上滑动),您会看到有个箭头(即光标)在屏幕上四处游移。您可以利用这个箭头选取或操作屏幕上的项目,像是选取档案、按下按钮、拖移滑杆等等。有时候在执行不同的操作或应用程式时,箭头会变成手、十字型、I型或其他图像。举例来说,如果您用Safari来浏览这个网页,并在网页上移动箭头,您会发现,当箭头移到文字或文字栏位(如Google文字框或URL栏位)上的时候,它会变成I型光标(有点像字母"I"的形状),通常这表示您可以与文字或栏位有所互动(例如输入或拷贝文字)。当箭头移到按钮或链接上,它会变成手的形状,告诉您这个项目可以点选。有时候Mac忙于工作时,箭头会暂时变成旋转中的彩色圆盘(有的Mac使用者称之为海滩球或风车),这代表某项工作正在执行中。 在您执行不同的工作或应用程式时,箭头(图中最左边)可能会以不同的样子出现。按一下鼠标(或触控式轨迹板按钮)可以选取箭头指向的项目。换句话说,如果箭头落在档案图像上,按一下即可选取该档案;如果箭头落在按钮或链接上,按一下可以启用该按钮或链接;要是落在文字栏位上,按一下可以反白该栏位并输入文字。对话框里出现蓝色按钮时(可参考“打印”或“储存”对话框),您可以按下Return键来选取该按钮,不一定要用鼠标。若想开启档案、档案夹或应用程式,请按两下鼠标按钮。通常您需要按两下Finder视窗或桌面上的项目才能将其开启,不过Dock里的项目除外,想开启Dock里的项目,按其图像一下即可。

触发器是构成时序逻辑电路的基本单元

触发器是构成时序逻辑电路的基本单元,触发器按逻辑功能分为RS触发器、JK触发器、D触发器、T触发器和T′触发器等多种类型;按其电路结构分为主从型触发器和维持阻塞型触发器等。 1.JK触发器 (1)JK触发器符号及功能 JK触发器有两个稳定状态:一个状态是Q=1,Q=0,称触发器处于“1”态,也叫置位状态;另一个状态是Q=0,Q=1,称触发器处于“0”态,也叫复位状态。JK触发器具有“置0”、“置1”、保持和翻转功能,符号如图l所示。 反映JK触发器的Q n和Q n、J、K之间的逻辑关系的状态表见表1。状态表中,Qn表示时钟脉冲来到之前触发器的输出状态,称为现态,Q n+1表示时钟脉冲来到之后的状态,称为次态。

图l JK触发器符号表1 JK触发器的状态表 JK触发器的特性方程为 JK触发器的种类很多,有双JK触发器74LS107,双JK触发器74LS114,741S112,74HC73,74HCT73等,有下降沿触发的,也有上升沿触发的。图l所示的JK触发器是下降沿触发的。

(2)双JK触发器74LS76 74LS76是有预置和清零功能的双JK触发器,引脚如图2所示,有16个引脚。功能表见表2,74LS76是下降沿触发的。 图2 74LS76引脚图表 2 74LS76的功能表 ①当R D=0,S D=1时

不论CP,J,K如何变化,触发器的输出为零,即触发器为“0”态。由于清零与CP脉冲无关,所以称为异步清零。 ②当R D=1,S D=0时 不论CP,J,K如何变化,触发器可实现异步置数,即触发器处于“1”态。 ③当R D=1,S D=1时 只有在CP脉冲下降沿到来时,根据J,Κ端的取值决定触发器的状态,如无CP脉冲下降沿到来,无论有无输人数据信号,触发器保持原状态不变。 2.D触发器 (1)D触发器符号及功能 D触发器具有置“0”和置“1”功能,其逻辑符号如图3所示,其逻辑功能为:在CP上升沿到来时,若D=I,则触发器置1;若D=0,则触发器置0,D触发器的特性方程为 D触发器的状态表见表3

实验四、 计数器的设计 电子版实验报告

实验四:计数器的设计 实验室:信息楼247 实验台号: 4 日期: 专业班级:机械1205 姓名:陈朝浪学号: 20122947 一、实验目的 1. 通过实验了解二进制加法计数器的工作原理。 2. 掌握任意进制计数器的设计方法。 二、实验内容 (一)用D触发器设计4位异步二进制加法计数器 由D触发器组成计数器。触发器具有0和1两种状态,因此用一个触发器 就可以表示1位二进制数。如果把n个触发器串起来,就可以表示N位二进制 数。(用两个74LS74设计实现) (二)利用74LS161设计实现任意进制的计数器 设计要求:学生以实验台号的个位数作为所设计的任意进制计数器。 先熟悉用1位74LS161设计十进制计数器的方法。 ①利用置位端实现十进制计数器。 ②利用复位端实现十进制计数器。 提示:设计任意计数器可利用芯片74LS161和与非门设计,74LS00为2输 入与非门,74LS30为8输入与非门。 74LS161为4位二进制加法计数器,其引脚图及功能表如下。

三、实验原理图 1.由4个D触发器改成的4位异步二进制加法计数器 2.由74LS161构成的十进制计数器

四、实验结果及数据处理 1.4位异步二进制加法计数器实验数据记录表 2. 画出你所设计的任意进制计数器的线路图,并说明设计思路。

设计思路:四进制为四个输出Q3Q2Q1Q0=0000,0001,0010,0011循环,第一个无效状态为0100 1,置位法设计四进制计数器:当检测到输入为0011时,先输出显示3,然后再将D 置于低电位,计数器输出Q3Q2Q1Q0复位。 2,复位法设计四进制计数器:当检测到第一个无效状态0100时,通过与非门的反馈计数器的Cr首先置于低电平使计数器复位为0000。 五、思考题 1. 由D触发器和JK触发器组成的计数器的区别? 答:D触发器是cp上升沿触发,JK触发器是下降沿触发。 2. 74LS161是同步还是异步,加法还是减法计数器? 答:同步。加法计数器。 3. 设计十进制计数器时将如何去掉后6个计数状态的? 答:加一个与非门形成负反馈。当计数到第一个无效状态Q3Q2Q1Q0==1010时,Q3和Q1全为1,Q1,Q3接与非门,输出作为复位信号,使所有触发器复位,从而去掉了后6个状态。

数电实验 计数器电路

实验5 计数器实验电路 1实验目的 1.1掌握计数器的工作原理及特性 1.2采用触发器及集成计数器构成任意进制计数器 2实验仪器与元器件 2.1实验仪器 数字电路实验箱、数字万用表、示波器 2.2芯片 74LS00/74ls04 74LS48 74LS161 共阴数码管电位器电阻等其它元件若干 3预习要求 3.1 预习计数器相关内容。 3.2 作出预习报告。 4实验原理 计数器是用来实现计数功能的时序部件,它能够计脉冲数,还可以实现定时、分频、产生节拍脉冲和脉冲序列等。计数器的种类很多,按时钟脉冲输入方式的不同,可以分为同步计数器和异步计数器。按进位体制不同,可以分二进制和非二进制计数器。按计数的增减趋势,可分加法或减法计数器等。目前,无论是TTL还是CMOC集成电路,都有品种齐全的中规模集成计数电路。作为使用者可以借助器件手册提供的功能表和工作波形以及引脚分布图,就能正确地使用这些器件。 4.1异步计数器

异步计数器是指计数脉冲不是直接加到所有触发器的时钟脉冲端。这样, 当一个计数脉冲作用后,计数器中某些触发器的状态发生变化,而其它触发器保持原来状态,即计数器中各触发器状态的更新与输入时钟脉冲异步。 在设计模为整数N 的异步计数器时,如果K N 2=,则为二进制计数器,例 如设计一个4位二进制计数器,1624==N ,K=4,用4个触发器级联即可。如果N 不等于2的整次幂,则是非二进制计数器,这时,可将N 写N=1*2N K 其中1N 为奇数,这样由模为K 2和模为1N 的两个计算器级联而成,其中模为1N 的计数器通常用反馈的方法构成.例如设计一个异步十进制计数器,可令 K 2=12,1N =5,就是用一个模2计数器和一个模5计数器级联.图7.1所示集成 接在各位触发器的时钟脉冲输入端,当计数脉冲来到时,应该翻转的触发器在同一时刻翻转。因此,同步计数器的工作速度比异步计数器快。同步计数器的设计可按“状态表+卡诺图+写出各触发器控制输入端的逻辑方程”,进行,然后画出逻辑电路。也可以根据状态表中各触发器输出的变化规律,直接写出各触发器控制输入端的逻辑方程,最后画出逻辑电路图。例如设计一个同步十进制加法计数器,其状态转换表如表7.1所示。采用双JK 触发器74LS76,通过分析状态转换表,可得到各触发器控制输入端的逻辑方程如下。

实验五计数器的设计实验报告

实验五计数器的设计——实验报告 邱兆丰 15331260 一、实验目的和要求 1.熟悉JK触发器的逻辑功能。 2.掌握用JK触发器设计同步计数器。 二、实验仪器及器件 1、实验箱、万用表、示波器、 2、74LS73,74LS00,74LS08,74LS20 三、实验原理 1.计数器的工作原理 递增计数器----每来一个CP,触发器的组成状态按二进制代码规律增加。递减计数器-----按二进制代码规律减少。 双向计数器-----可增可减,由控制端来决定。 2.集成J-K触发器74LS73 ⑴符号: 图1 J-K触发器符号

⑵功能: 表1 J-K触发器功能表 ⑶状态转换图: 图2 J-K触发器状态转换图

⑷特性方程: ⑸注意事项: ①在J-K触发器中,凡是要求接“1”的,一定要接高电平(例如5V),否则会出现错误的翻转。 ①触发器的两个输出负载不能过分悬殊,否则会出现误翻。 ② J-K触发器的清零输入端在工作时一定要接高电平或连接到实验箱的清零端子。3.时序电路的设计步骤 内容见实验预习。 四、实验内容 1.用JK触发器设计一个16进制异步计数器,用逻辑分析仪观察CP和各输出波形。2.用JK触发器设计一个16进制同步计数器,用逻辑分析仪观察CP和各输出波形。3.设计一个仿74LS194 4.用J-K触发器和门电路设计一个特殊的12进制计数器,其十进制的状态转换图为:5.考虑增加一个控制变量D,当D=0时,计数器按自定义内容运行,当D=1时,反方向运行 五、实验设计及数据与处理 实验一

16进制异步计数器 设计原理:除最低级外,每一级触发器用上一级触发器的输出作时钟输入,JK都接HIGH,使得低一级的触发器从1变0时高一级触发器恰好接收下降沿信号实现输出翻转。实验二 16进制同步计数器 设计原理:除最低级外,每一级的JK输入都为所有低级的输出的“与”运算结果实验三 仿74LS194 设计原理:前两个开关作选择端输入,下面四个开关模仿预置数输入,再下面两个开关模仿左移、右移的输入,最后一个开关模仿清零输入。四个触发器用同一时钟输入作CLK输入。用2个非门与三个与门做成了一个简单译码器。对于每一个触发器,JK输入总为一对相反值,即总是让输入值作为输出值输入。对于每一个输入,当模式“重置”输出为1时,其与预置值结果即触发器输入;当模式“右移”、“左移”输出为1时,其值为上一位或下一位对应值;当各模式输出均为0时各触发器输入为0,使输出为0。 实验四 设计原理: 在12进制同步计数器中,输出的状态只由前一周期的状态决定,而与外来输入无关,因此目标电路为Moore型。而数字电路只有0和1两种状态,因此目标电路要表达12种状态需

数电实验计数器电路

数电实验计数器电路 SANY标准化小组 #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#

实验5 计数器实验电路 1实验目的 掌握计数器的工作原理及特性 采用触发器及集成计数器构成任意进制计数器 2实验仪器与元器件 实验仪器 数字电路实验箱、数字万用表、示波器 2.2 芯片 74LS00/74ls04 74LS48 74LS161 共阴数码管 电位器 电阻等其它元件若干 3预习要求 预习计数器相关内容。 作出预习报告。 4实验原理 计数器是用来实现计数功能的时序部件,它能够计脉冲数,还可以实现定时、分频、产生节拍脉冲和脉冲序列等。计数器的种类很多,按时钟脉冲输入方式的不同,可以分为同步计数器和异步计数器。按进位体制不同,可以分二进制和非二进制计数器。按计数的增减趋势,可分加法或减法计数器等。目前,无论是TTL 还是CMOC 集成电路,都有品种齐全的中规模集成计数电路。作为使用者可以借助器件手册提供的功能表和工作波形以及引脚分布图,就能正确地使用这些器件。 异步计数器 异步计数器是指计数脉冲不是直接加到所有触发器的时钟脉冲端。这样,当一个计数脉冲作用后,计数器中某些触发器的状态发生变化,而其它触发器保持原来状态,即计数器中各触发器状态的更新与输入时钟脉冲异步。 在设计模为整数N 的异步计数器时,如果K N 2=,则为二进制计数器,例如设计一个 4位二进制计数器,1624==N ,K=4,用4个触发器级联即可。如果N 不等于2的整次幂,则是非二进制计数器,这时,可将N 写N=1*2N K 其中1N 为奇数,这样由模为K 2和模为1N 的两个计算器级联而成,其中模为1N 的计数器通常用反馈的方法构成.例如设计一个异步十进制计数器,可令K 2=12,N =5,就是用一个模2计数器. T '触发器,+写出各触发

第13章触发器及时序逻辑电路习题

第十三章 触发器和时序逻辑电路 13.1重点内容提要 时序逻辑电路由组合逻辑电路和具有记忆作用的触发器构成。时序逻辑电路的特点是:其输出不仅仅取决于电路的当前输入,而且还与电路的原来状态有关。 1. 双稳态触发器 双稳态触发器的特点: 1).有两个互补的输出端 Q 和Q 。 2).有两个稳定状态。“1”状态和“0” 状态。通常将 Q = 1和Q = 0 称为“1”状态,而把Q = 0和Q = 1称为“0” 状态。 3).当输入信号不发生变化时,触发器状态稳定不变。 4).在一定输入信号作用下,触发器可以从一个稳定状态转移到另一个稳定状态。 按其逻辑功能,触发器可分为:RS 触发器,JK 触发器、D 触发器、T 触发器和T ’触发器。 各时钟控制触发器的逻辑符号和逻辑功能见表13.1.1: 名称 逻辑符号 次态方程 RS 触发器 Q R S Q n +=+1 =?S R 0 (约束方程) JK 触发器 1n n n Q JQ KQ +=+ D 触发器 D Q n =+1 T 触发器 1n n Q T Q +=⊕ T ’ 触发器 1n n Q Q += 把一种已有的触发器通过加入转换逻辑电路,可以转换成为另一种功能的触发器。 2.同步时序逻辑电路的分析

同步时序逻辑电路的分析步骤如下: 1.由给定的逻辑电路图写出下列各逻辑方程式: (1)各触发器的特性方程。 (2)各触发器的驱动方程。 (3)时序电路的输出方程。 2.将驱动方程代入相应触发器的特性方程,求得电路的状态方程(或次态方程)。 3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态转换图或时序图。 4.根据电路的状态转换图说明该时序逻辑电路的逻辑功能。 3.典型的时序逻辑电路 在数字系统中,最典型的时序逻辑电路是寄存器和计数器。 1)寄存器 寄存器是用来存储数据或运算结果的一种常用逻辑部件。寄存器的主要组成部分是在双稳态触发器基础上加上一些逻辑门构成。按功能分,寄存器分为数码寄存器和移位寄存器。移位寄存器是既能寄存数码,又能在时钟脉冲的作用下使数码向高位或向低位移动的逻辑功能部件。通常有左移寄存器、右移寄存器、双向移位寄存器和循环移位寄存器。移位寄存器可实现数据的串行、并行转换,数据的运算和数据的处理等。 2)计数器 计数器是一种对输入脉冲数目进行计数的时序逻辑电路,被计数的脉冲信号称为计数脉冲。计数器除计数外,还可以实现定时、分频等,在计算机及数字系统中应用极广。 计数器种类很多,通常有如下不同的分类方法。 (1)按逻辑功能可分为加法计数器、减法计数器和可逆计数器。 (2)按计数进制可分为二进制计数器、十进制计数器和任意进制计数器等。 (3)按工作方式可分为同步计数器和异步计数器。 集成电路74161型四位同步二进制计数器 图13.1.1为74161型四位同步二进制可预置计数器的外引线排列图及其逻辑符号,其中D R 是异步 (a ) 外引线排列图 (b ) 逻辑符号 图13.1.1 74161型四位同步二进制计数器 清零端,LD 是预置数控制端,0123A A A A 是预置数据输入端,EP 和ET 是计数控制端,Q 3Q 2Q 1Q 0是计数输出端,RCO 是进位输出端。74161型四位同步二进制计数器具有以下功能: ① 异步清零。D R =0时,计数器输出被直接清零,与其他输入端的状态无关。 ② 同步并行预置数。在D R =1条件下,当LD =0且有时钟脉冲CP 的上升沿作用时,3A 、2A 、1A 、0A 输入端的数据3d 、2d 、1d 、0d 将分别被3Q 、2Q 、1Q 、0Q 所接收。 ③ 保持。在D R LD ==1条件下,当=?EP ET 0,不管有无CP 脉冲作用,计数器都将保持原有状态