当前位置:搜档网 › FPGA招聘笔试题

FPGA招聘笔试题

FPGA 专项部分试题。注:以下涉及代码时,可以使用verilog ,systemverilog 或VHDL 中任何一种。

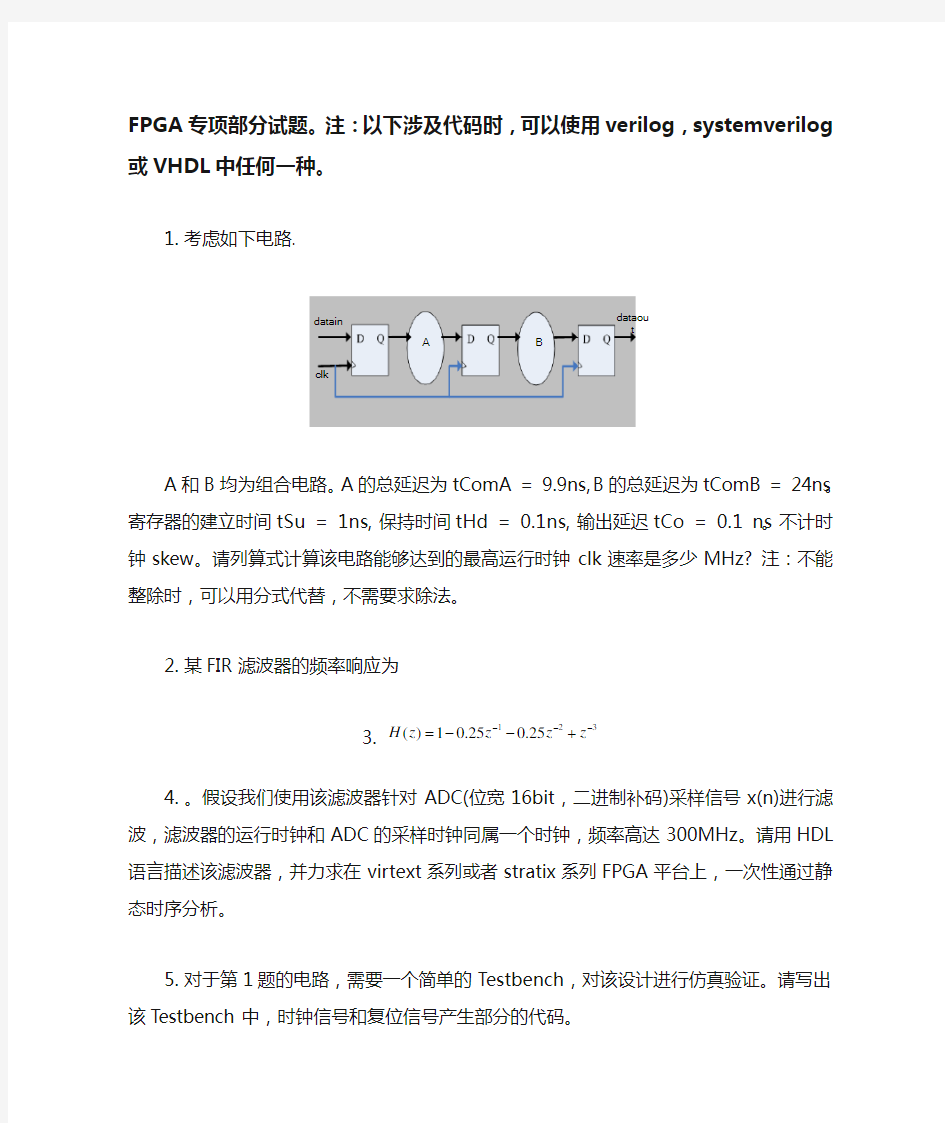

1. 考虑如下电路.

A

B clk datain

dataou t

A 和

B 均为组合电路。A 的总延迟为tComA = 9.9ns ,B 的总延迟为tComB = 24ns 。寄

存器的建立时间tSu = 1ns ,保持时间tHd = 0.1ns ,输出延迟tCo = 0.1 ns 。不计时钟skew 。请列算式计算该电路能够达到的最高运行时钟clk 速率是多少MHz? 注:不能整除时,可以用分式代替,不需要求除法。

2. 某FIR 滤波器的频率响应为123()10.250.25H z z z z ---=--+。假设我们使用该滤波器

针对ADC(位宽16bit ,二进制补码)采样信号x(n)进行滤波,滤波器的运行时钟和ADC 的采样时钟同属一个时钟,频率高达300MHz 。请用HDL 语言描述该滤波器,并力求在virtext 系列或者stratix 系列FPGA 平台上,一次性通过静态时序分析。

3. 对于第1题的电路,需要一个简单的Testbench ,对该设计进行仿真验证。请写出该

Testbench 中,时钟信号和复位信号产生部分的代码。

4. 一个系统,有两个时钟域的电路,其时钟频率分别为fClka = 64MHz 和fClkb = 34MHz 。

Clka 时钟域驱动一个脉冲信号pulse_a(位宽为1bit),传输到Clkb 时钟域的电路中,用于触发b 模块的某些动作。电路模型和关键时序如下图。请写出a2b 模块的rtl 代码。并给出评估,你的设计大约使用了多少个寄存器?

Clka

pulse_

a

相关主题