Verilog HDL数字设计与综合 夏宇闻译(第二版)课后题答案

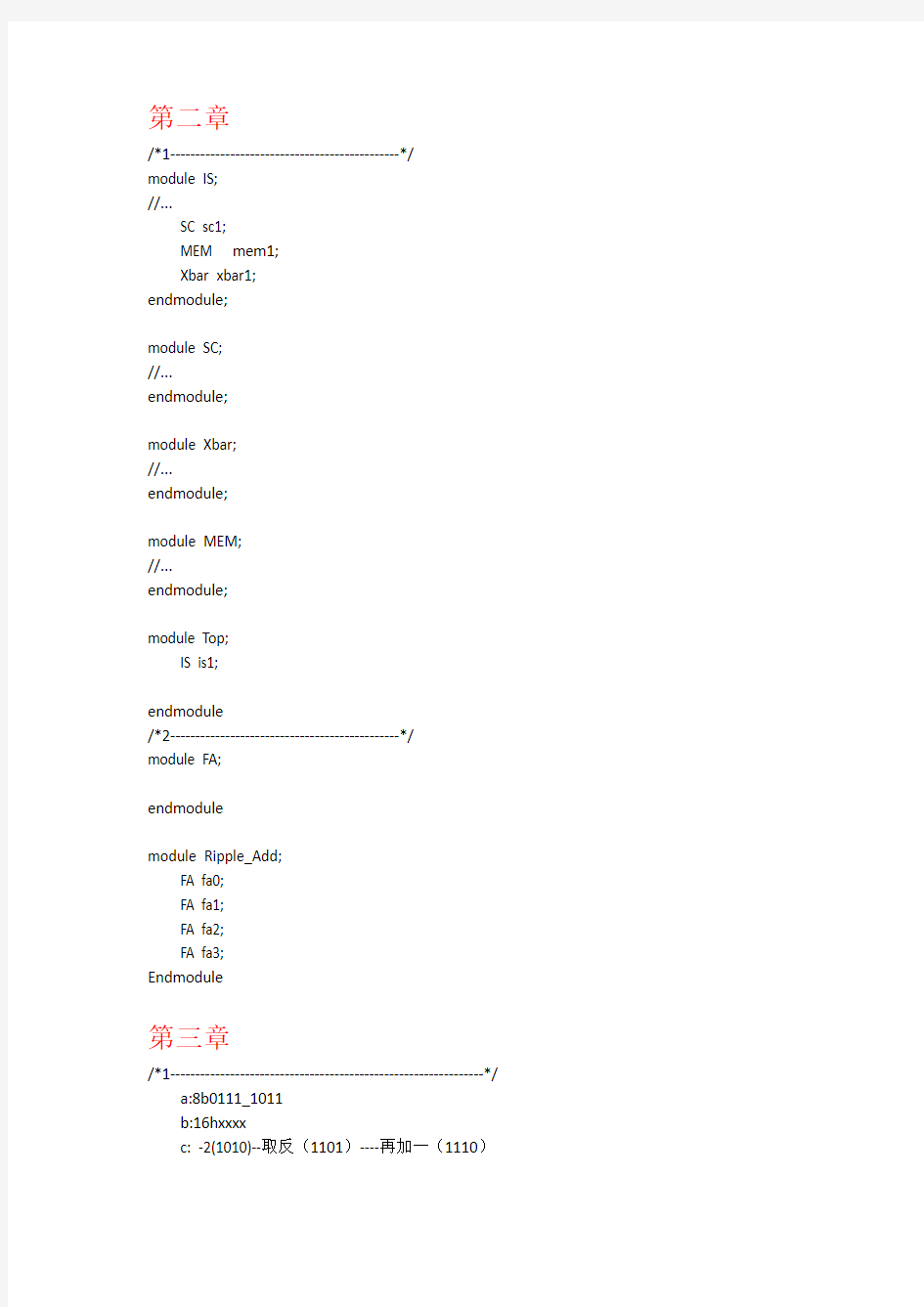

第二章

/*1----------------------------------------------*/

module IS;

//...

SC sc1;

MEM mem1;

Xbar xbar1;

endmodule;

module SC;

//...

endmodule;

moduleXbar;

//...

endmodule;

module MEM;

//...

endmodule;

module Top;

IS is1;

endmodule

/*2----------------------------------------------*/

module FA;

endmodule

moduleRipple_Add;

FA fa0;

FA fa1;

FA fa2;

FA fa3;

Endmodule

第三章

/*1---------------------------------------------------------------*/ a:8b0111_1011

b:16hxxxx

c: -2(1010)--取反(1101)----再加一(1110)

d: 'h1234

/*2---------------------------------------------------------------*/

a:正确

b:正确

c:正确

d:正确

/*3---------------------------------------------------------------*/

a :合法

b :合法

c :不合法,含有$ 为延时含义

d :标识符组成:字母数字下划线。

/*4---------------------------------------------------------------*/

a: wire [7:0] a_in;

b: reg [31:0]

c: integer count;

d: time snap_shot;

e: integer delays[20];

f: reg [63:0] mem[256];

g: parameter cach_size=256;

/*5---------------------------------------------------------------*/

a : 1010

b: 10

c : 400

第四章

/*1-----------------------------------------------------------------------*/

//模块的基本组成部分有哪些?哪几个部分必须出现?

模块定义已关键字module开始,模块名,端口列表,端口声明和可选的参数声明出现在其他部分的前面

,endmodule必须为最后一条语句

1)wire。reg和其他类型的变量的声明

2)数据流语句(assign,连续赋值语句)

3)低层模块实例

4)always和initial块,所有的行为语句都在这些块中

5) 任务和函数。

其中module和模块名和endmodule是必不可少的。

/*2-----------------------------------------------------------------------*/

//一个不与外界环境交互的模块是否有端口?模块定义中是否有端口列表?

不与外界交互即没有端口列表,在没有端口的情况下端口列表也是不存在的。

/*3-----------------------------------------------------------------------*/ moduleshift_reg(reg_in[3:0] , clock , reg_out[3:0] );

input [3:0] reg_in;

input clock;

output [3:0] reg_out;

//......

endmodule;

/*4-----------------------------------------------------------------------*/ //connect in order

module stimulus();

reg [3:0] REG_IN;

wire [3:0] REG_OUT;

reg CLK;

shift_regsr1(REG_IN,CLK,REG_OUT);

endmodule

/*5-----------------------------------------------------------------------*/ //connect by name

module stimulus();

reg [3:0] REG_IN;

wire [3:0] REG_OUT;

reg CLK;

shift_regsr1(.clock(CLK) ,.reg_in(REG_IN) , .reg_out(REG_OUT) );

endmodule

/*6-----------------------------------------------------------------------*/ stimulus.REG_IN

stimulus.CLK;

stimulus.REG_OUT;

/*7-----------------------------------------------------------------------*/ stimulus.sr1;

stimulus.sr1.clock;

stimulus.sr1.reg_in;

stimulus.sr1.reg_out;

第五章

/*1--------------------------------------------------------------------*/

//利用双输入的nand门设计自己的与或非门。

//my_and

modulemy_and(out , in1,in2);

input in1,in2;

output out;

endmodule

//my_not

modulemy_not(out , in1);

input in1;

output out;

nand(out , in1 ,in1 );

endmodule

//my_and

modulemy_or(out ,in1 ,in2);

wire t;

nand(t,in1,in2);

nand(out,t,t);

//

endmodule

/*2--------------------------------------------------------------------*/ //使用上题中完成的my_or,my_and,my_not构造一个双//输入的xor门,其功能是计算z=x'y+xy'

/*3--------------------------------------------------------------------*/ //全加器

module sum(a,b,c_in,sum,c_out);

inputa,b,c_in;

outputsum,c_out;

wire y1,y2,y3,y4;

wire x1,x2,x3;

or(sum,y1,y2,y3,y4);

and(y1,a,b,c_in);

and(y2,x1,b,x3);

and(y3,x1,x2,c_in);

and(y4,a,x2,x3);

not(x1,a);

not(x2,b);

not(x3,c);

wire j1,j2,j3;

or(c_out,j1,j2,j3);

and(j1,a,b);

and(j2,b,c_in);

and(j3,a,c_in);

endmodule

/*4--------------------------------------------------------------------*/

//带有延时的SR锁存器

module SR(reset , q ,set , qbar);

inputreset,set;

outputq,qbar;

wire line1,line2;

nor( line2 , reset ,line1 );

nor( line1, set ,line2 );

endmodule

/*---------------------------ISE中一个端口如何接多根线?????????????????????*/

/*5--------------------------------------------------------------------*/

module select(out,in1,in2,s);

input in1,in2,s;

output out;

//3为上升延迟,4为下降延时,5为关断延迟。

bufif1 #(1:2:3,3:4:5,5:6:7) b2(out,in1,s);

bufif0 #(1:2:3,3:4:5,5:6:7) b1(out,in2,s);

endmodule

/*--------------------------------------------------------------------*/

第六章

/*1----------------------------------------------------------------*/

//全减器

//输入:x,y,z(前面的借位)

//输出:差和借位

module sub(x,y,z,D,B);

inputx,y,z;

output D,B;

wire y0,y1,y2,y3;

wire j1,j2,j0;

//非门

not(j0,x);

not(j1,y);

not(j2,z);

and(y0,j0,j1,j2);

and(y1,j0,y,j2);

and(y2,x,j1,j2);

and(y3,x,y,z);

or(D,y0,y1,y2,y3);

//B

wire a1,a0,a2;

and(a0 , j0 ,y);

and( a1, j0, z);

and( a2, y , z);

or(B,a1,a0,a2);

endmodule

//激励模块:

module stimulus;

//initial 从仿真0时刻开始,而且只执行一次,若程序中有若干个initial块,则并发执行。

rega,b,c;

wired,e;

regi;

sub sub(a,b,c,d,e);

initial

for(i=1 ;i>0;) begin

#5 ;

a=1;

b=1;

c=0;

#5;

a=1;

b=0;

c=0;

end

endmodule

/*2----------------------------------------------------------------*/

//大小比较器

modulecmp(A ,B ,A_gt_B , A_lt_B,A_eq_B);

input [3:0] A,[3:0] B;

outputA_gt_B , A_lt_B , A_eq_B ;

endmodule

/*3 ----------------------------------------------------------------*/

modulesyn_counter(clear,clock,count_enable,Q);

inputclear,clock,count_enable;

output [3:0] Q;

wire [3:0] Q;

wire b1,b2,b3;

nand(b1,count_enable,Q[1]);

nand(b2,b1,Q[2]);

nand(b3,b2,Q[3]);

jk jk1(count_enable,count_enable,clear,clock,Q[0],);

jk jk2(b1,b1,clear,clock,Q[1],);

jk jk3(b2,b2,clear,clock,Q[2],);

jk jk4(b3,b3,clear,clock,Q[3],);

endmodule

modulejk(J,K,clear,clock,q,qbar);

inputJ,K,clear,clock;

outputq,qbar;

wirea,y,c,b,ybar,cbar,d;

not (cbar,clock);

nand a1(a,qbar,J,clock,clear);

nand a2(b,clock,K,q);

nand a3(y,a,ybar);

nand a4(ybar,y,clear,b);

nand a5(c,y,cbar);

nand a6(d,cbar,ybar);

nand a7(q,c,qbar);

nand a8(qbar,q,clear,d);

endmodule

第七章

/*1----------------------------------------------------------------*/ reg oscillate=0;

initial

begin

forever

#30 oscillate=~oscillate;

end

/*2----------------------------------------------------------------*/ initial

clock=0;

always

begin

#30 clock=1;

#10 clock=0;

end

/*3 ----------------------------------------------------------------*/ 执行时刻:0,10,15,35.

最终结果:a=0,b=1,c=0;d=3'b010;

/*4----------------------------------------------------------------*/ 执行时刻:0,10,5,20.

最终结果:a=0,b=1,c=0;d=3'b010;

/*5 ----------------------------------------------------------------*/ a,b,c,d: 0 ,1,1,0

//每个initial中的语句是串行执行的。

/*6 ----------------------------------------------------------------*/ d=0;

夏宇闻verilog设计示范和上机习题

设计示范和上机习题 练习一.简单的组合逻辑设计 //(方法一): //---------------文件名compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal = (a==b)? 1 : 0; //a等于b时,equal输出为1;a不等于b时,equal输出为0。 endmodule //(方法二): module compare(equal,a,b); input a,b; output equal; reg equal; always @(a or b) if(a==b) //a等于b时,equal输出为1; equal =1; else //a不等于b时,equal输出为0。 equal = 0; //思考:如果不写else 部分会产生什么逻辑? endmodule //------------------------------------------------------------- //----------测试模块源代码(方法之一): `timescale 1ns/1ns // 定义时间单位。 `include "./compare.v" //包含模块文件。在有的仿真调试环境中并不需要此语句。 //而需要从调试环境的菜单中键入有关模块文件的路径和名称module t; reg a,b; wire equal; initial // initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 a=0; b=0;

Verilog HDL数字设计与综合 夏宇闻译(第二版)课后题答案

第二章 /*1----------------------------------------------*/ module IS; //... SC sc1; MEM mem1; Xbar xbar1; endmodule; module SC; //... endmodule; moduleXbar; //... endmodule; module MEM; //... endmodule; module Top; IS is1; endmodule /*2----------------------------------------------*/ module FA; endmodule moduleRipple_Add; FA fa0; FA fa1; FA fa2; FA fa3; Endmodule 第三章 /*1---------------------------------------------------------------*/ a:8b0111_1011 b:16hxxxx c: -2(1010)--取反(1101)----再加一(1110)

d: 'h1234 /*2---------------------------------------------------------------*/ a:正确 b:正确 c:正确 d:正确 /*3---------------------------------------------------------------*/ a :合法 b :合法 c :不合法,含有$ 为延时含义 d :标识符组成:字母数字下划线。 /*4---------------------------------------------------------------*/ a: wire [7:0] a_in; b: reg [31:0] c: integer count; d: time snap_shot; e: integer delays[20]; f: reg [63:0] mem[256]; g: parameter cach_size=256; /*5---------------------------------------------------------------*/ a : 1010 b: 10 c : 400 第四章 /*1-----------------------------------------------------------------------*/ //模块的基本组成部分有哪些?哪几个部分必须出现? 模块定义已关键字module开始,模块名,端口列表,端口声明和可选的参数声明出现在其他部分的前面 ,endmodule必须为最后一条语句 1)wire。reg和其他类型的变量的声明 2)数据流语句(assign,连续赋值语句) 3)低层模块实例 4)always和initial块,所有的行为语句都在这些块中 5) 任务和函数。 其中module和模块名和endmodule是必不可少的。 /*2-----------------------------------------------------------------------*/ //一个不与外界环境交互的模块是否有端口?模块定义中是否有端口列表? 不与外界交互即没有端口列表,在没有端口的情况下端口列表也是不存在的。

verilog数字系统设计教程第5章例题

第五章例题 例如:if(a>b) out1 = int1; else out1 = int2; 例如:always @( some_event) //虚的字体表示块语句 begin if(a>b) out1 = int1; else if (a==b) out1 = int2; else out1 = int3; end if(a>b) begin out1<=int1; out2<=int2; end else begin out1<=int2; out2<=int1; end //有时begin_end块语句的不慎使用会改变逻辑行为。见下例: if(index>0) for(scani=0;scani if(memory[scani]>0) begin $display("..."); memory[scani]=0; end end else /*WRONG*/ $display("error-indexiszero"); //定义寄存器和参数。 reg [31:0] instruction, segment_area[255:0]; reg [7:0] index; reg [5:0] modify_seg1, modify_seg2, modify_seg3; parameter segment1=0, inc_seg1=1, segment2=20, inc_seg2=2, segment3=64, inc_seg3=4, data=128; //检测寄存器index的值 if(index 五层楼电梯运行控制逻辑设计 摘要:电梯是高层建筑不可缺少的运输工具,用于垂直运送乘客和货物,传统的电梯控制系统主要采用继电器,接触器进行控制,其缺点是触点多,故障率高、可靠性差、维修工作量大等,本设计根据电梯自动控制的要求利用V erilog语言编写并完成系统设计,在利用软件仿真之后,下载到了FPGA上进行硬件仿真。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了之前的可编程器件门电路数有限及速度上的缺点。 关键词:电梯控制FPGA V erilog软件设计硬件设计 在当今社会,随着城市建设的不断发展,高层建筑的不断增多,电梯作为高层建筑中垂直运行的交通工具已与人们的日常生活密不可分。目前电梯控制系统主要有三种控制方式:继电路控制系统(早期安装的电梯多位继电器控制系统),FPGA/CPLD [1] 的控制系统、微机控制系统。继电器控制系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,目前已逐渐被淘汰,而微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷。而FPGA/CPLD控制系统由于运行可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点 [2] ,倍受人们重视等优点,已经成为目前在电梯控制系统中使用最多的控制方式,目前也广泛用于传统继电器控制系统的技术改造。 随着现代化城市的高度发展,每天都有大量人流及物流需要输送,因此在实际工程应用中电梯的性能指标相当重要,主要体现在:可靠性,安全性,便捷快速性。电梯的可靠性非常重要,直接或间接的影响着人们的生产,生活,而电梯的故障主要表现在电力拖动控制系统中,因此要提高可靠性也要从电力拖动控制系统入手。 本次设计尝试用V erilog实现电梯控制器部分,进行了多层次的电梯控制,也进行了软件及硬件上的仿真验证,时序分析以保证设计的正确。在设计中先用软件进行模拟仿真,然后又下载到FPGA开发板上进行硬件仿真,以确保设计的正确性。 第六章例题 [例1]:用initial 块对存储器变量赋初始值 initial begin areg=0; //初始化寄存器areg for(index=0;indexVerilog实现的基于FPGA的五层楼电梯运行控制逻辑设计

夏宇闻 verilog源代码 第6章例题