ISE12.4使用手册

Xilinx ISE 12.4使用手册

------Edit by C2_305 1.Xilinx ISE 12.4用户界面

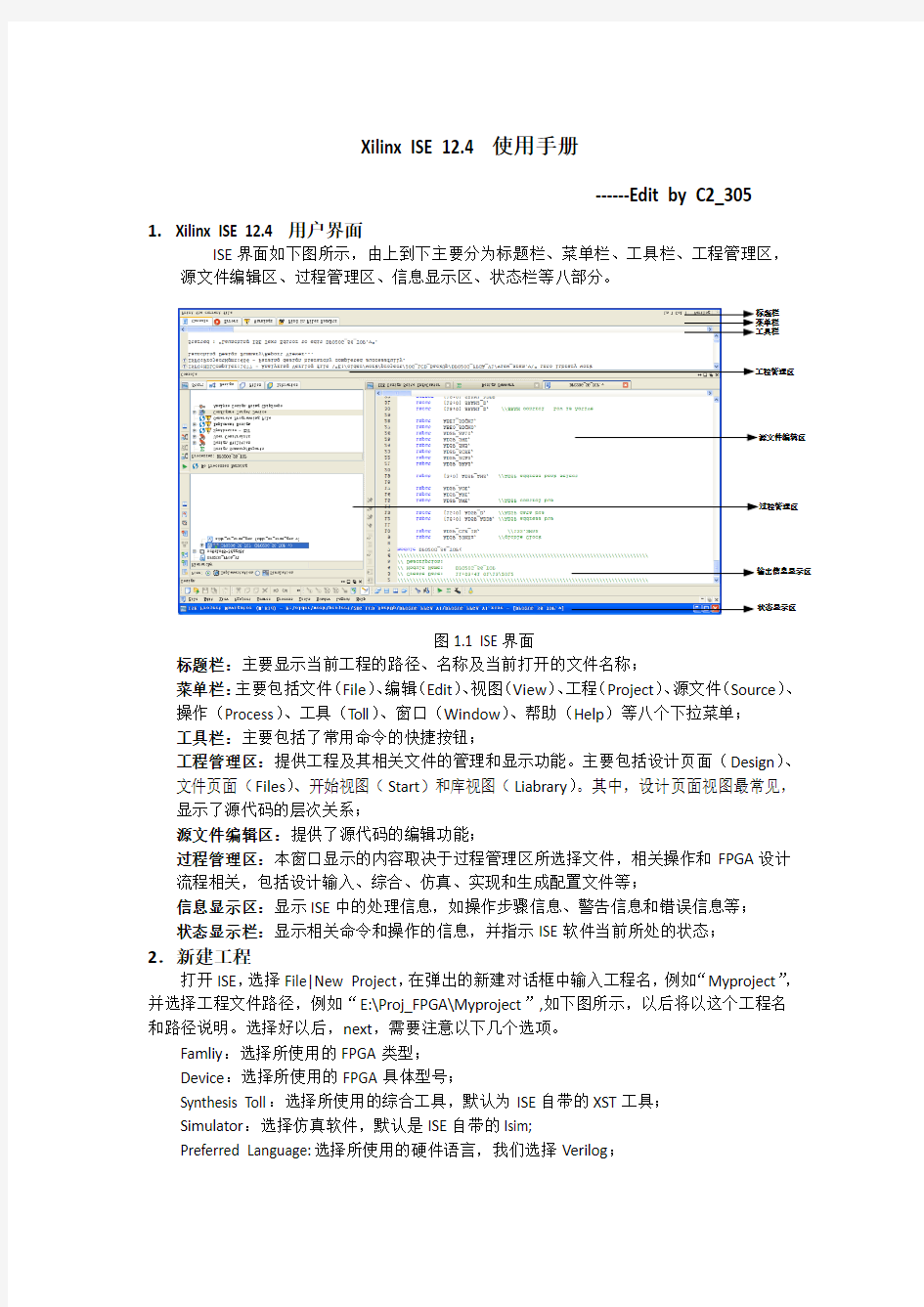

ISE界面如下图所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区,源文件编辑区、过程管理区、信息显示区、状态栏等八部分。

过程管理区

图1.1 ISE界面

标题栏:主要显示当前工程的路径、名称及当前打开的文件名称;

菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、工具(Toll)、窗口(Window)、帮助(Help)等八个下拉菜单;

工具栏:主要包括了常用命令的快捷按钮;

工程管理区:提供工程及其相关文件的管理和显示功能。主要包括设计页面(Design)、文件页面(Files)、开始视图(Start)和库视图(Liabrary)。其中,设计页面视图最常见,显示了源代码的层次关系;

源文件编辑区:提供了源代码的编辑功能;

过程管理区:本窗口显示的内容取决于过程管理区所选择文件,相关操作和FPGA设计流程相关,包括设计输入、综合、仿真、实现和生成配置文件等;

信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等;

状态显示栏:显示相关命令和操作的信息,并指示ISE软件当前所处的状态;

2.新建工程

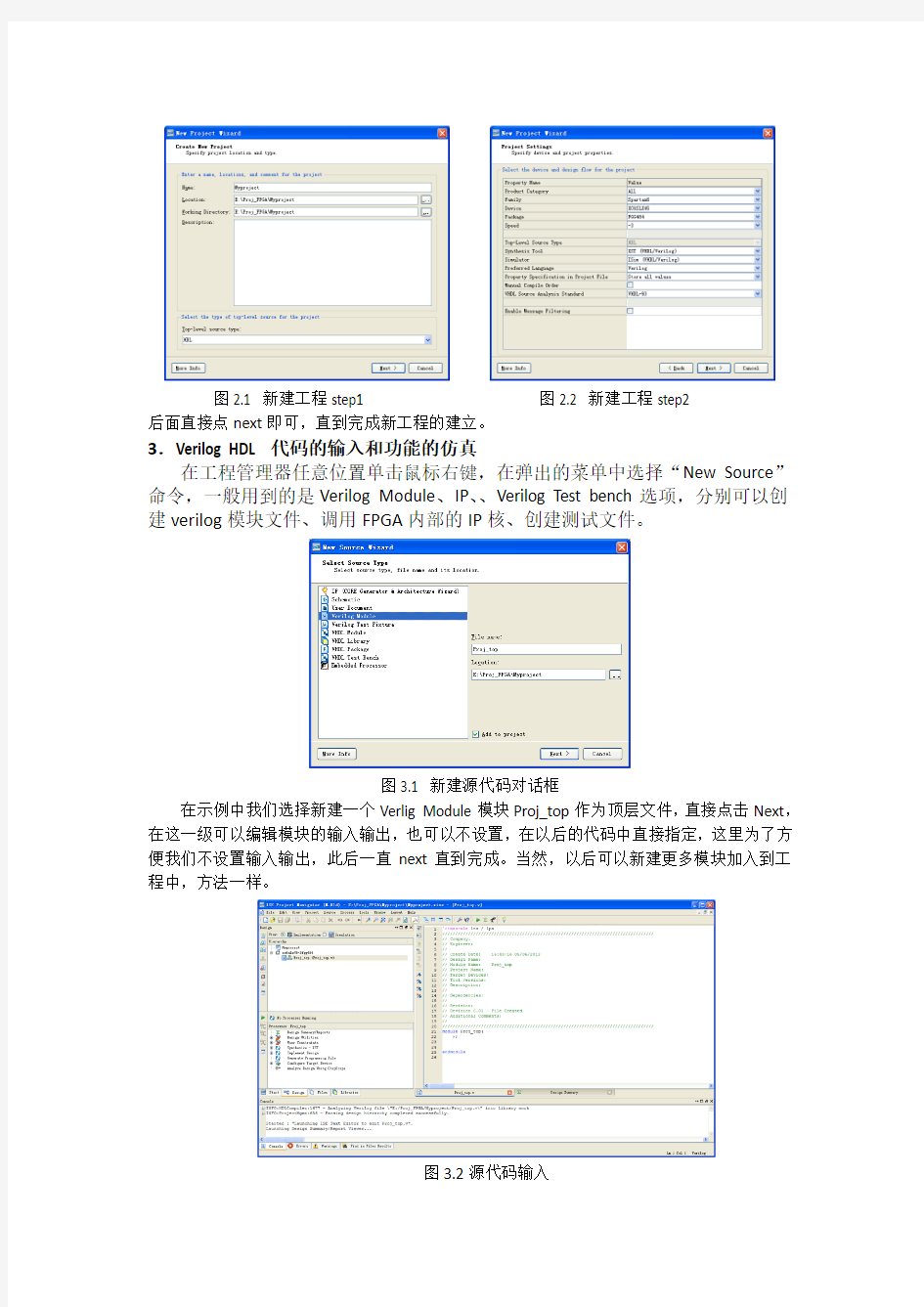

打开ISE,选择File|New Project,在弹出的新建对话框中输入工程名,例如“Myproject”,并选择工程文件路径,例如“E:\Proj_FPGA\Myproject”,如下图所示,以后将以这个工程名和路径说明。选择好以后,next,需要注意以下几个选项。

Famliy:选择所使用的FPGA类型;

Device:选择所使用的FPGA具体型号;

Synthesis Toll:选择所使用的综合工具,默认为ISE自带的XST工具;

Simulator:选择仿真软件,默认是ISE自带的Isim;

Preferred Language:选择所使用的硬件语言,我们选择Verilog;

图2.1 新建工程step1 图2.2 新建工程step2

后面直接点next即可,直到完成新工程的建立。

3.Verilog HDL代码的输入和功能的仿真

在工程管理器任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,一般用到的是Verilog Module、IP、、Verilog Test bench选项,分别可以创建verilog模块文件、调用FPGA内部的IP核、创建测试文件。

图3.1 新建源代码对话框

在示例中我们选择新建一个Verlig Module模块Proj_top作为顶层文件,直接点击Next,在这一级可以编辑模块的输入输出,也可以不设置,在以后的代码中直接指定,这里为了方便我们不设置输入输出,此后一直next直到完成。当然,以后可以新建更多模块加入到工程中,方法一样。

图3.2源代码输入

创建完成后如图3.2所示,这时,我们已经创建了一个Verilog模块的例子,剩余工作就是在源文件编辑区编写代码以实现设计功能。以下是一个简单的例子。

例1:利用Verilog代码实现8bit计数器

module Proj_top(

input clk,

input rst,

output reg [7:0] dout

);

always @ (posedge clk)

begin

if(!rst)//low act

dout <= 8'h00;

else

dout <= dout + 1'b1;

end

endmodule

输入代码完成后,保存,双击过程管理区中的Synthesize XST,出现对工程进行综合。综合过程中,如在信息显示区出现error,需要根据提示查看修改代码。当工程正确无误后,该选项将变为绿色的对号(代码正确)或者黄色的感叹号(含有警告,可以忽略,需要具体分析)。

图3.3 工程的综合图3.4测试文件的创建为了对设计程序做逻辑上的验证,一般,我们可以添加一个测试文件来验证所设计的程序的正确性。在工程管理区的View这一栏,选择Simulation,并在下面的hierarchy空白处右键NewSource,选择Verilog Test Fixture,其创建方式其实和上面所讲的文件的创建类似。在此示例中,我们创建一个名为“test”的测试模块。测试代码如下:

module test;

// Inputs

reg clk;

reg rst;

// Outputs

wire [7:0] dout;

// Instantiate the Unit Under Test (UUT)

Proj_top uut (

.clk(clk),

.rst(rst),

.dout(dout)

);

initial begin

// Initialize Inputs

clk = 0;

rst = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

rst = 1;//add by yourself

end

always #10 clk = ~clk;//add by yourself

endmodule

这时,在工程管理区选中到测试文件名“test”上,在过程管理区中双击Simulate Behavioral Model,如果正确,运行结束将弹出仿真界面Isim。

图3.5综合测试文件

Isim界面大体和ISE相似,下面列举几个常用的工具:

从左到右:波形放大、缩小、波形全部显示、将光标移到波形中央、刷新、光标的左移、

右移、添加新光标、重新产生测试波形、一直运行、按设定的时间步进运行。

在这里可以观察波形是否和设计一致。

至此,一个最简单的ISE工程从设计到逻辑验证完成。

4.综合与实现

一个完整的FPGA工程,需要进行综合、实现2个过程。

综合(Synthesize):将HDL语言、原理图等设计输入翻译成由与、或、非门和RAM、触

发器等基本逻辑单元连接(网表),并根据目标和要求(约束条件)优化所生成的逻辑连接,

生成NGC、NCR以及LOG文件。综合之后可双击View RTL Schematic来查看门级电路;

实现(Implement):将综合输出的逻辑网表翻译为所选器件的底层模块与硬件源语,将

涉及映射到器件结构上,进行布局布线,以达到在选定的器件上实现设计的目的。主要分为

3步:翻译(Translate)逻辑网表、映射(Map)到器件单元、布局布线(Place&Route);

图4.1 FPGA的综合和实现

5.FPGA文件的下载

在安装目录寻找打开impact,在左侧impact flow窗口中双击,然后在

右面空白区域右键单击ADD Xilinx Device,选择所需加载的.bit文件,然后右侧窗口出现FPGA

的绿色符号,在符号上右键单击Program,等待下载完毕。

图5.1 FPGA文件下载step1 图5.2 FPGA文件下载step2 6.添加chipscope

FPGA在线调试一般要需要用到chipscope(逻辑分析仪),这样可以实时抓取我们感兴趣的信号状态,用来分析工程的正确性。添加方式和新建Verilog文件一样,选择Chipscope Definition and Connection File。这里,创建了一个名为test的chipscope。

图6.1 新建chipscope

新建完成后,在工程管理区双击test.cdc,弹出如下界面:

图6.2 chipscope配置step1

Next,设置来设定所抓取的数据的个数,Next,设置数据存储深度,默认为1k,注意勾选,next,点击Modefy Connection,

图6.3 chipscope配置step2

图6.4 chipscope配置step3

左上区域可以选择具体模块,左下框图中的Pattern选项中可搜索信号名,格式为“*信号名*”(引号内部),在右面的区域可以添加触发信号和所需抓取的数据。设置完毕ok,点击。

添加完成后,在ISE界面的过程管理区双击Generate Programming File,完成工程得综合、翻译。布局布线、映射和产生输出文件。正确以后,双击Analyaze Design Using ChipScope,打开逻辑分析仪调试程序。

图6.5 编译并打开chipscope调试

在连接JTAG Chain之前,首先必须确认FPGA仿真器连接到目标板上,目标板上电且仿真器连接正确以后,仿真器指示灯显示为绿色。

确认以后,点击图标,连接仿真器。成功后,选中DEV:0MyDevice0,右键单击configure,勾选Clean previous project setting,OK。

图6.6 ChipScope Pro Analyzer界面

图6.7 Configure

图6.8 配置好的ChipScope Pro Analyzer

配置好ChipScope Pro Analyzer,需要特别关注Trigger Setup和Waveform这2个窗口,可以在Trigger Setup中设置触发条件,在Waveform中查看触发后的波形;

工具栏中需特别关注:左起分别为触发(必需等待设置的触发状态到来)、

停止触发、马上触发(不等待设置的触发状态是否到来,在当前状态立即触发);

利用这几个最常用的工具和其他一些工具可以完成带电调试FPGA,和DSP配合使用调试目标板。