panel显示原理与LVDS屏线制作

笔记本显示通道介绍及北桥到Panel的连接

一、Panel 显示介绍

我们目前给panel传输数据用的是LVDS(Low Voltage Differential Signal)信号,也就是在我们TFT cable线上传输的是LVDS信号,但是在MCH和panel内部都有一个transmitter,MCH里面是把并行的数字信号变成串行的LVDS信号,Panel内部是把LVDS信号分解成并行的数字信号,然后显示。

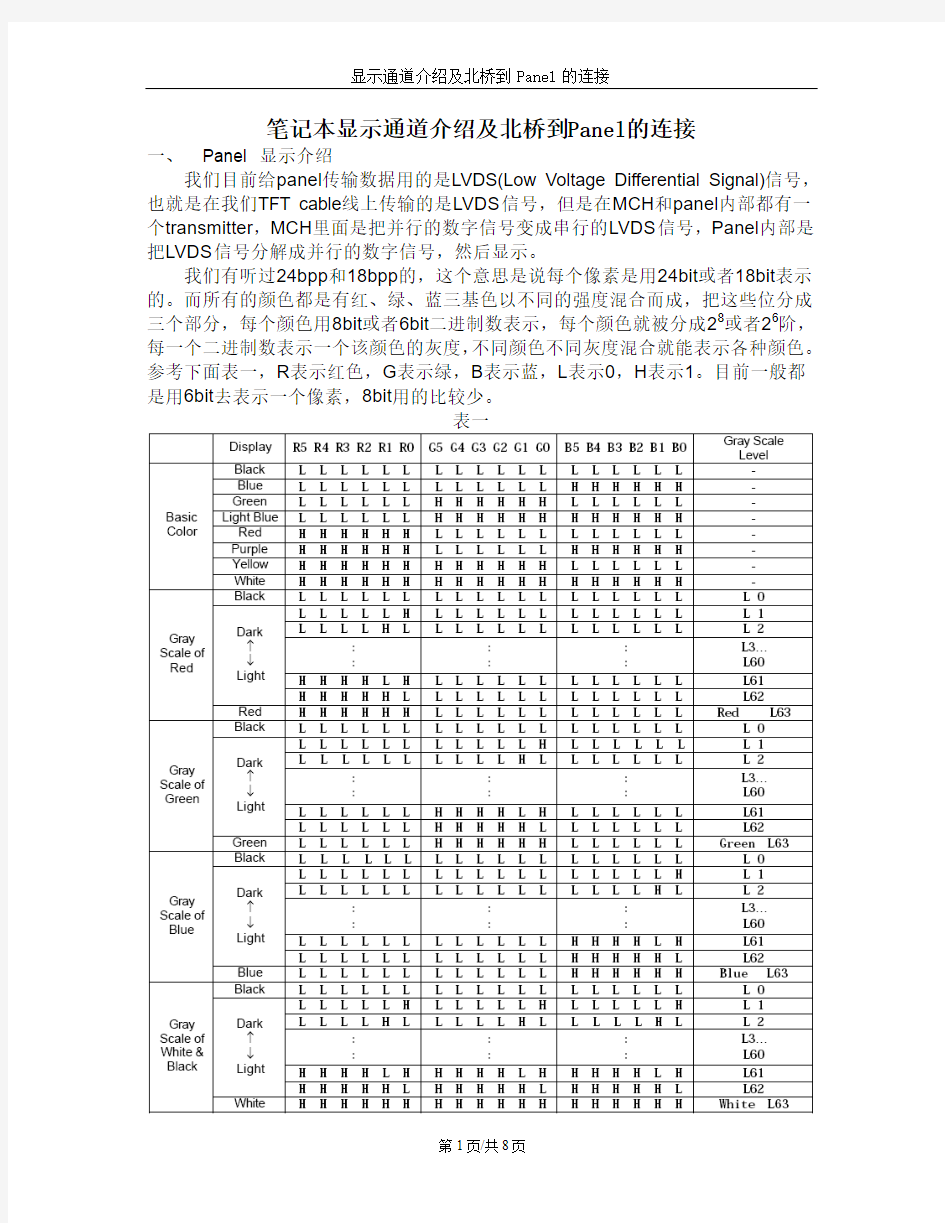

我们有听过24bpp和18bpp的,这个意思是说每个像素是用24bit或者18bit表示的。而所有的颜色都是有红、绿、蓝三基色以不同的强度混合而成,把这些位分成三个部分,每个颜色用8bit或者6bit二进制数表示,每个颜色就被分成28或者26阶,每一个二进制数表示一个该颜色的灰度,不同颜色不同灰度混合就能表示各种颜色。参考下面表一,R表示红色,G表示绿,B表示蓝,L表示0,H表示1。目前一般都是用6bit去表示一个像素,8bit用的比较少。

表一

我们目前北桥所用的Transmitter,一个时钟周期传输一个像素的数据,也有一个之中周期里面传输两个像素的,比如ATI的M24就有支持这种模式,但是不能只是发送端支持,也要接收端支持该模式才可以。具体一个时钟周期里面dada线里面有些什么数据,在下面的第二部分有写到。

Panel目前有XGA (1024x768)、WXGA (1280x760)、SXGA+ (1400x1050)、WSXGA+ (1680x1050)、UXGA (1600x1200)、WUXGA (1920x1200)、and QXGA (2048x1536),这些像素与实际的panel,有些出入,具体请参考panel的资料。在XGA和大多数WXGA的时候还可以用一个通道去传输数据。由于LVDS的边沿变化率(典型为1 V/ns)和EMI的限制,使得时钟输速度不能上的太高,北桥内部把时钟设置在25MHZ和112MHZ之间,单通道最高理论速度是112MP。

当在XGA时,满屏的像素为1024x768=786432Pixel

当在WXGA时,满屏的像素为1280x760=972800Pixel,WXGA的分辨率还有其他的几种,如1400x900=1260000pixel,此时大于112MP。

当在SXGA时,满屏的像素为1400x1050=1470000pixel只能以增加通道来弥补。

当像素大于112MP,一个通道就不够传输这么多的数据,必需要增加到两个通道。在目前大多数分辨率的WXGA像素也是小于112MP的,所以在WXGA以上的模式和部分像素高于112MP的WXGA,一定要用双通道。

二、 北桥端的LVDS 信号(18bpp )

GMCH 这边提供两个通道,Channel A and Channel B :如下表二,每个通道包括三个data pairs 和一个Clock pair ,然后加共用的VDD Enable 、Back light Enable Back light control (PWM )。

表二

通过GPIO 或者EDID 去判断是多高分辨率的panel ,我们老的机种上面用的都是GPIO 拉出两个作为Panel ID 去判断的,目前新开发的机种上用的EDID 去判断panel 类型。

{21}{21}

的GPIO

上图是我们用的panel ID部分原理图,从南桥的GPIO出来,通过电阻上拉到

+V3.3s上,然后连接到LCD 的connector上,最后这两个ID的状态,根据用的是什么分辨率的panel,在cable上拉到不同状态。当要为“0”时,就把该pin拉到地上,浮空状态则为“1”。通过这两个ID的不同组合,去对应不同分辨率的panel。

EDID判断方法是通过把北桥上的LDDC_CLK和LDDC_DATA拉到EDID的CLK 和DATA上,这个BUS就相和SMBUS一样,bios从Panel里面读出该panel的参数,然后配置BIOS,从而实现智能的调整,不必对于不同的panel,人为地去给定状态。

在XGA或者WXGA的模式下,有效的通道只会用Channel A,而channel B被disable,当发现panel的分辨率在XGA或者WXGA之上时,就会打开另一个通道channel B,用双通道去传输数据,但是第一个数据是在Channel A上传输的。此时,Channel A 和Channel B的比特率是相同的,不会出现不同的比特率传输数据。

在data pairs里面压缩有同步信号(HS和VS,与CRT一样panel显示也要同步信号去完成扫描)与DE信号。当用双通道显示时,Channel A里面一定要有同步信号与DE信号,Channel B里面可以有也可以没有同步信号与DE信号,这个可以通过工具去修改register (Address offset: 61180h–61183h Bit 18:17) 去设置,default值是含有这些信号。

在这个两个通道里面,时钟周期是非对称的,一个clock周期里面高低电平时间比例是4:3,时钟的周期是随着像素数在变化。在一个时钟周期里,包涵有七个数据,一个周期的时钟类型是1100011,如下图。在这个图中,上面的LVDS Clock Pair 的实际波形并不是这样,这个只是为了更好看出1100011的格式,而这样去表示。

在8bit编码里面,为了与6bit兼容,把低六位按照6bit的形式去编码,然后高两位,总共6位放到最后一组数据里面。我们的北桥都是6bit编码的,有的显卡有8bit,如ATI的M24就可以通过8Bit编码。

显卡端的LVDS界面与MCH相似,可以对应理解。

想更深入了解MCH端的LVDS interface请参考MCH EDS。

三、Panel端的信号。(SPWG中只是说明到6Bit编码,18bpp(Bit Per Pixel))

Panel这一端总共也有两个通道,一个EVEN 一个ODD,在XGA或者WXGA的

panel的界面,只有ODD有效,有的panel里面在只有一个通道的时候,不会区分ODD 和EVEN;当panel的分辨率在XGA或者WXGA之上时,两个通道都会有效。

Panel的connector各个pin的定义在SPWG规范中有规定,只要满足该规范的panel,就会按照该规范去定义各个pin。在SPWG中,定义了有两种connector,一个20pin的,只是给XGA和WXGA用;另一个30pin,可以用于所有分辨率的panel,当只是XGA和WXGA,EVEN通道就不接收数据,只有ODD有效。参考下面两个表格及对应数据mapping figure。R0 –R5表示红色的6位二进制数,G0-G5表示绿色的6位二进制数,B0-B5表示蓝色的6位二进制数,HS/VS表示同步信号。

Single Channel LVDS Data Mapping (18bpp) 20-Pin Connector

Dual Channel LVDS Data Mapping (18bpp) 30-Pin Connector

Active Area Pixel Layout

在双通道显示的时候,Odd(奇)通道对应第奇数个像素,EVEN(偶)对应第偶数个像素,即第一个点显示的是ODD通道的数据。上图形象说明了像素的排列及一个像素的组成。在single channel时,就只有一个通道的数据显示在所有的像素上。

注:更深的了解请参考SPWG SPEC Ver3.5。

四、panel与MCH显示通道的连接及panel cable线注意。

1、在XGA或者WXGA的模式下。

通过前面的介绍,已经了解到,在该模式下,只要利用一个通道就足够传输所需的数据。

在MCH这一端,我们只需要连接出Channel A的信号;在Panel端,只是从ODD通道读数据,所以通过同轴线连接这两个通道即可。如果出现Channel A 连接到EVEN通道或者Channel B连接到ODD或者EVEN,都是不可以显示的。

因为此时channel B和EVEN都是disable的。

2、在XGA或者WXGA的以上模式下。

此时我们必须要把两个通道都连接上,Channel A 连接到ODD,Channel B 连接到EVEN。

在默认状况下,MCH端的Channel B里面是有同步信号和DE信号的。这时如果通道连接反了,即channel A连接到EVEN,Channel B连接到ODD,也是可以显示的,但是我们会发现,图像显示不正常,图像模糊,有点乱。从理论上分析,这是由于像素的前一点和后一点刚好对调,所以会出现这种情况。

我们目前的Panel Cable中,在料号为1401001125(for Toshiba LTD141LMOS)的cable信号定义表中发现,刚好是channel A连接到EVEN,Channel B连接到ODD,但是却显示正常的,这个问题我已经和供应商联系过,是由于他们给我们的资料错误,刚好EVEN通道和ODD通道对调。所以我们这样制作的线材显示是正常的,实际上还是channel A连接到ODD,Channel B连接到EVEN。

3、panel cable线制作注意

3.1、通道连接不能出错,这个一定要对这panel本身的pin脚定义,因为发现

有的panel并不是完全符合SPWG规范,发现有什么异常情况,一定要

联系供应商,以免出现上面资料错的情况。

3.2、差分信号的正负不能对调,从以往的经验来看,differential clock信号的

正负关系与数据不一样,具体可以打开一个cable的机构图查看。

3.3、差分信号至少要求是同轴线,如果不从成本考虑,用同轴双绞线最好。

3.4、注意在这些线的外面包上地,隔离外界地干扰。