Verilog程序5、VGA接口实验

本地地址:E:\FPGA\myown\myvga\myvga.v

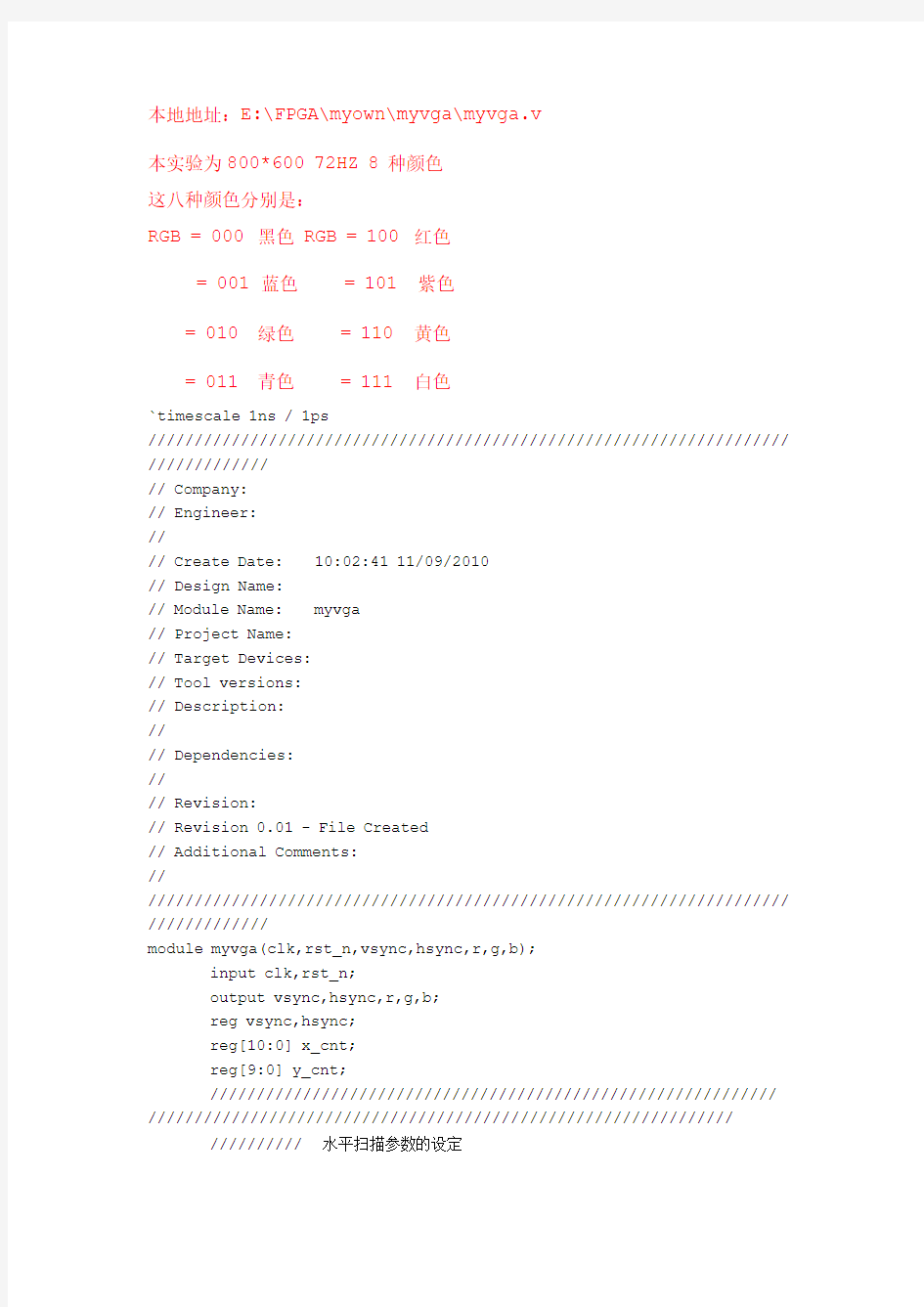

本实验为800*600 72HZ 8种颜色

这八种颜色分别是:

RGB = 000 黑色 RGB = 100 红色

= 001 蓝色 = 101 紫色

= 010 绿色 = 110 黄色

= 011 青色 = 111 白色

`timescale 1ns / 1ps

///////////////////////////////////////////////////////////////////// /////////////

// Company:

// Engineer:

//

// Create Date: 10:02:41 11/09/2010

// Design Name:

// Module Name: myvga

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

///////////////////////////////////////////////////////////////////// /////////////

module myvga(clk,rst_n,vsync,hsync,r,g,b);

input clk,rst_n;

output vsync,hsync,r,g,b;

reg vsync,hsync;

reg[10:0] x_cnt;

reg[9:0] y_cnt;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 水平扫描参数的设定

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

parameter LinePeriod =12'd1040; //行同步周期

parameter H_SyncPulse=10'd120; //行同步信号

parameter H_BackPorch=10'd61; //行同步后肩

parameter H_ActivePix=10'd806; //行同步数据有效

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 垂直扫描参数的设定

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

parameter FramePeriod=10'd666;

parameter V_SyncPulse=10'd6;

parameter V_BackPorch=10'd21;

parameter V_ActivePix=10'd604;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 水平扫描计数x_cnt只负责计数从0计数计到1040

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) x_cnt <= 1;

else if(x_cnt == LinePeriod) x_cnt <= 1;

else x_cnt <= x_cnt+ 1;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 水平扫描信号vsync产生在0到120时为低电平

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) hsync <= 1'b1;

else if(x_cnt == 1) hsync <= 1'b0; //产生hsync 信号

else if(x_cnt == H_SyncPulse+1) hsync <=

1'b1;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 垂直扫描计数

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) y_cnt <= 1;

else if(y_cnt == FramePeriod) y_cnt <= 1;

else if(x_cnt == LinePeriod) y_cnt <= y_cnt+1;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 垂直扫描信号hsync产生

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) vsync <= 1'b1;

else if(y_cnt == 1) vsync <= 1'b0; //产生vsync信号

else if(y_cnt == V_SyncPulse+1) vsync <=

1'b1;

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

////////// 垂直扫描信号hsync产生

///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////

wire valid; //有效显示区标志

assign valid =

(x_cnt >= (H_SyncPulse+H_BackPorch)) &&

(x_cnt < (H_SyncPulse+H_BackPorch+H_ActivePix)) &&

(y_cnt >= (V_SyncPulse+V_BackPorch)) &&

(y_cnt < (V_SyncPulse+V_BackPorch+V_ActivePix));

//三原色的分配,显示整屏红色

/*assign r=valid?1:0;

assign g=valid?0:0;

assign b=valid?0:0;

*/

wire[9:0] x_pos=x_cnt-H_SyncPulse-H_BackPorch;

wire[9:0] y_pos=y_cnt-V_SyncPulse-V_BackPorch;

//---------------------------------------

//显示一个矩形框

wire a_dis,b_dis,c_dis,d_dis;

assign a_dis=((x_pos>=200)&&(x_pos<=220)) &&

((y_pos>=140)&&(y_pos<=460));

assign b_dis=((x_pos>=580)&&(x_pos<=600)) &&

((y_pos>=140)&&(y_pos<=460));

assign c_dis=((x_pos>=220)&&(x_pos<=580)) &&

((y_pos>=140)&&(y_pos<=160));

assign d_dis=((x_pos>=220)&&(x_pos<=580)) &&

((y_pos>=440)&&(y_pos<=460));

//显示一个小矩形

wire e_rdy;

assign e_rdy = (x_pos>=385) && (x_pos<=415) && (y_pos>=285) &&

(y_pos<=315);

assign r=valid?e_rdy:0;

assign g=valid?(a_dis|b_dis|c_dis|d_dis):0;

assign b=valid?~(a_dis|b_dis|c_dis|d_dis):0;

endmodule

Test Benth File

`timescale 1ns / 1ps

///////////////////////////////////////////////////////////////////// ///////////

// Company:

// Engineer:

//

// Create Date: 10:21:21 11/09/2010

// Design Name: myvga

// Module Name: E:/FPGA/myown/myvga/t_vga.v

// Project Name: myvga

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: myvga

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

///////////////////////////////////////////////////////////////////// ///////////

module t_vga_v;

// Inputs

reg clk;

reg rst_n;

// Outputs

wire vsync;

wire hsync;

wire r;

wire g;

wire b;

// Instantiate the Unit Under Test (UUT)

myvga uut (

.clk(clk),

.rst_n(rst_n),

.vsync(vsync),

.hsync(hsync),

.r(r),

.g(g),

.b(b)

);

always #50 clk=~clk;

initial begin

// Initialize Inputs

clk = 0;

rst_n = 1;

// Wait 100 ns for global reset to finish #100 rst_n=0;

#100 rst_n=1;

// Add stimulus here

end

endmodule

Implementation Constrants Flie

NET "clk" LOC = P54;

NET "rst_n" LOC = P38;

NET "hsync" LOC = P39;

NET "vsync" LOC = P35;

NET "r" LOC = P68;

NET "g" LOC = P52;

NET "b" LOC = P44;

vga图像显示控制

VGA图像显示控制器 一、摘要和关键词 摘要:VGA显示屏显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。通过控制扫描计数器不同值时对RGB三原色信号的控制,来完成显示设计。 关键词:行列扫描行列同步RGB三原色控制 二、设计任务要求 实验目的 1. 熟练掌握VHDL 语言和QuartusII 软件的使用; 2. 理解状态机的工作原理和设计方法; 3. 掌握利用EDA 工具进行自顶向下的电子系统设计方法; 4. 熟悉VGA 接口协议规范。 实验要求: 设计一个VGA 图像显示控制器,达到如下功能: 显示模式为640×480×60HZ 模式; 用拨码开关控制R、G、B(每个2 位),使显示器可以显示64种纯色; 在显示器上显示横向彩条信号(至少6 种颜色); 在显示器上显示纵向彩条信号(至少8 种颜色); 在显示器上显示自行设定的图形、图像等。 选做:自拟其它功能。 三、实验原理 1、显示控制原理 常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。VGA显示控制器控制CRT显示图象的过程如图1所示

LCD-VGA 嵌入式微型显示控制系统软件设计说明书

编号: 版本: LCD-VGA微型显示驱动电路 软件详细设计说明书 编写: 2015年05月18日 校对: 2015年06月12日 审核: 2015年06月15日 批准: 2015年06月20日 目录 一、项目背景 (2) 二、软件功能介绍 (2) 三、软件特性介绍 (2) 四、软件的运行环境介绍 (2) 五、系统的物理结构 (2) 六、系统总结构 (3) 七、系统各个模块介绍 (5) 七、算法设计 ............................................................ 错误!未定义书签。 八、接口设计 ............................................................ 错误!未定义书签。 九、需求规定 (10) 十、测试计划 (10)

一、项目背景 随着便携式多媒体终端需求量迅速增加,在视频解码等方面对芯片低功耗的要求也越来越高。因此,只有将模拟视频信号转换成为符合ITU-R BT、656标准的数字信号,才可方便地利用FPGA或者DSP甚至PC机来进行信号处理。本模块就就是利用TI公司的超低功耗视频解码芯片TVP5150对视频信号A/D解码,由单片机通过I2C总线控制,实现驱动VGA级别(640X480)的微型显示模组,并预留地址数据等接口,作为模块验证以及后续数字信号处理之用。 二、软件功能介绍 本系统主要由视频转换模块TVP5150、按键模块、8051内核单片机与液晶图形缩放引擎(A912)组成,系统框图6、1所示。STC单片机通过I2C接口控制其余三部分模块的工作,视频解码IC把复合视频转换成标准8位的ITU-RBI、656格式的数字信号传输到A912,A912通过解码矩阵电路把解调后的信号转换成三基色RGB信号,最后通过增益/偏移控制、伽马校正、抖动处理与图形缩放变RGB信号输出到液晶屏、 三、软件特性介绍 以STC单片机 MCU为控制中心,以视频转换芯片TVP5150为硬件核心。电路将模拟视频信号编码为ITU-R BT.656类型的数据流。单片机管理整个工作流程,缩放引擎芯片进行图像处理,把数据流转换为RGB信号,最终在液晶屏上获得显示图像。该显示器结构轻薄,电路简单,性能可靠,图像显示清晰稳定。 四、软件的运行环境介绍 软件应在以下环境中运行: 硬件环境:选用256字节 RAM+1K AUX-RAM、4KB ROM、S0P 型号为STC11F04E 单片机 计算机软件:采用C语言进行编译并生成相应执行文件格式,在STC11F04E 单片机上运行。 五、系统的物理结构 微型显示嵌入式软件中的硬件就是由主控、显示驱动模块、按键输入模块、视频解码器模块TVP5150组成,其物理结构图如下图所示

网络程序设计实验报告-Winsock编程接口实验

网络程序设计 实验报告 实验名称: Winsock编程接口实验 实验类型:____验证型实验_____ __ 指导教师:______________________ 专业班级:_____________________ 姓名:_______________________ 学号:_____________________ 电子邮件:____________ 实验地点:______ _______ 实验日期2013 年 3 月29 日 实验成绩:__________________________

一、实验目的 ●掌握Winsock的启动和初始化; ●掌握gethostname(),gethostbyname(),GetAdaptersInfo()等信息查询函数的使用。 二、实验设计 由实验内容可以知道: 1、编写程序能同时实现对多个域名的解析。比如在控制台输入:getip https://www.sodocs.net/doc/ab702352.html, https://www.sodocs.net/doc/ab702352.html,,能输出https://www.sodocs.net/doc/ab702352.html,和https://www.sodocs.net/doc/ab702352.html,对应的IP地址列表。 2、编写程序获取并输出本地主机的所有适配器的IP地址,子网掩码,默认网关,MAC 地址。 首先要了解一些基本的知识gethostname(),gethostbyname(),GetAdaptersInfo()等信息查询函数的基本知识gethostbyname()返回对应于给定主机名的包含主机名字和地址信息的hostent结构指针。结构的声明与gethostaddr()中一致。 之后要根据内容画出函数流程图

三、实验过程(包含实验结果) 1.在实验过程中调用GetAdaptersInfo()时,出现了undeclared identifier的报错,原因是没有包含其头文件,之后进行一些修改解决了问题. 2.实验结果 3.选择查看本机信息 四、讨论与分析 1.Winsock初始化的作用是什么? 答:使用winsock初始化可加载winsock编程的动态链接库。

微机8255并行接口实验实验六

深圳大学实验报告课程名称:微型计算机技术 实验项目名称:8255并行接口实验 学院,专业:计算机科学与技术 指导教师:骆剑平 报告人:学号:班级:计科2班 同组人:无 实验时间:2014年6月11日 实验报告提交时间:2014年6月16日 教务处制

实验目的与要求: 实验目的: 1. 学习并掌握8255 的工作方式及其应用; 2. 掌握8255 典型应用电路的接法。 实验设备 PC机一台,TD-PITE 实验装置一套。 实验方法、步骤: 实验内容: 1. 基本输入输出实验。编写程序,使8255 的A口为输入,B口为输出,完成拨动开关到数据灯的数据传输。要求只要开关拨动,数据灯的显示就发生相应改变。 2. 流水灯显示实验。编写程序,使8255 的A口和B口均为输出,数据灯D7~D0由左向右,每次仅亮一个灯,循环显示,D15~D8与D7~D0 正相反,由右向左,每次仅点亮一个灯,循环显示。 实验原理 并行接口是以数据的字节为单位与I/O 设备或被控制对象之间传递信息。CPU和接口之间的数据传送总是并行的,即可以同时传递8 位、16 位或32 位等。8255可编程外围接口芯片是Intel公司生产的通用并行I/O 接口芯片,它具有A、B、C三个并行接口,用+5V单电源供电,能在以下三种方式下工作:方式0--基本输入/输出方式、方式1--选通输入/输出方式、方式2--双向选通工作方式。8255 的内部结构及引脚如图2-6-1 所示,8255工作方式控制字和C口按位置位/复位控制字格式如图2-6-2所示。

实验步骤: 1. 基本输入输出实验 本实验使8255 端口A工作在方式0 并作为输入口,端口B工作在方式0 并作为输出口。用一组开关信号接入端口A,端口B 输出线接至一组数据灯上,然后通过对8255 芯片编程来 实现输入输出功能。具体实验步骤如下述: (1)实验接线图如图2-6-3所示,按图连接实验线路图; (2)编写实验程序,经编译、连接无误后装入系统; (3)运行程序,改变拨动开关,同时观察LED 显示,验证程序功能。

c++网络编程实例

第1章Visual C++网络编程概述 Visual C++(后面简写为VC)网络编程是指用户使用MFC类库(微软基础类库)在VC编译器中编写程序,以实现网络应用。用户通过VC编程实现的网络软件可以在网络中不同的计算机之间互传文件、图像等信息。本章将向用户介绍基于Windows操作系统的网络编程基础知识,其开发环境是VC。在VC编译器中,使用Windows Socket进行网络程序开发是网络编程中非常重要的一部分。 1.1 网络基础知识 如果用户要进行VC网络编程,则必须首先了解计算机网络通信的基本框架和工作原理。在两台或多台计算机之间进行网络通信时,其通信的双方还必须遵循相同的通信原则和数据格式。本节将向用户介绍OSI七层网络模型、TCP/IP协议以及C/S编程模型。 1.1.1 OSI七层网络模型 OSI网络模型是一个开放式系统互联的参考模型。通过这个参考模型,用户可以非常直观地了解网络通信的基本过程和原理。OSI参考模型如图1.1所示。 图1.1 OSI七层网络模型

·3· 用户从OSI 网络模型可以很直观地看到,网络数据从发送方到达接收方的过程中,数据的流向以及经过的通信层和相应的通信协议。事实上在网络通信的发送端,其通信数据每到一个通信层,都会被该层协议在数据中添加一个包头数据。而在接收方恰好相反,数据通过每一层时都会被该层协议剥去相应的包头数据。用户也可以这样理解,即网络模型中的各层都是对等通信。在OSI 七层网络模型中,各个网络层都具有各自的功能,如表1.1所示。 表1.1 各网络层的功能 注意:在表1.1中列出了OSI 七层网络模型中各层的基本功能概述。用户根据这些基本 的功能概述会对该网络模型有一个比较全面的认识。 1.1.2 TCP/IP 协议 TCP/IP 协议实际上是一个协议簇,其包括了很多协议。 例如,FTP (文本传输协议)、SMTP (邮件传输协议)等应 用层协议。TCP/IP 协议的网络模型只有4层,包括数据链路 层、网络层、数据传输层和应用层,如图1.2所示。 在TCP/IP 网络编程模型中,各层的功能如表1.2所示。 表1.2 TCP/IP 网络协议各层功能 在数据传输层中,包括了TCP 和UDP 协议。其中,TCP 协议是基于面向连接的可靠的通信协议。其具有重发机制,即当数据被破坏或者丢失时,发送方将重发该数据。而UDP 协议是基于用户数据报协议,属于不可靠连接通信的协议。例如,当用户使用UDP 协议发送一条消息时,并不知道该消息是否已经到达接收方,或者在传输过程中数据已经丢失。但是在即时通信中,UDP 协议在对一些对时间要求较高的网络数据传输方面有着重要的 作用。 图1.2 TCP/IP 网络协议模型

实验五vga图显示控制

实验五 VGA图像显示控制 一实验目的 1.进一步掌握VGA显示控制的设计原理。 2.了解图像的存储和读取方法。 3.进一步掌握4×4键盘或PS/2键盘接口电路设计方法。 4.掌握状态机设计复杂控制电路的基本方法。 二硬件需求 1.EDA/SOPC实验箱一台。 三实验原理 VGA图像显示控制利用实验三中学习的《VGA显示控制模块》显示存储于ROM中的图像数据。 要显示的图像是四块64*64像素大小的彩色图片,通过键盘控制可以选择不同的图片显示。图像可以在屏幕上移动(水平和垂直方向每帧分别移动“H_Step”点和“V_Step”点),通过键盘改变“H_Step”和“V_Step”的值即可改变其移动速度和方向。图像碰到屏幕边沿会反弹回去。如图5.1所示 H_Step V_Step 图5.1 VGA图像显示控制示意图 实验中要用到4×4键盘、VGA显示控制、ROM等模块,在《实验三常用模块电路的设计》中已经讲述,可以直接使用已做好的模块(可能需要修改部分代码)。键盘也可以使用PS/2接口键盘,这样可以输入更多的字符。 四实验内容 1、图5.2是整个设计的顶层电路。

图5.2 VGA图像显示控制顶层电路图 2、实验三中学习的几个模块 ①“Read_Keyboard”模块与实验三中的4×4键盘模块一致; ②四个ROM模块使用宏功能模块实现,并设置其内存初始化文件分别为“FBB.mif”、“dog.mif”、“cat.mif”、“flower.mif”,如图5.3所示。当然也可以用其他图片(大小为64*64)使用“BmpToMif”软件生成对应的“mif”文件,如图5.4所示。

网络编程实验报告

实验一TCP Socket API程序设计 一、预备知识 1.网络编程基本概念 网络上的计算机间的通讯,实质上是网络中不同主机上的程序之间的通讯。在互联网中使用IP地址来标识不同的主机,在网络协议中使用端口号来标识主机上不同进程,即使用(IP地址,端口号)二元组。 套接字(Socket)用于描述IP地址和端口,是一个通信链的句柄,通信时一个网络程序将要传输的一段信息写入它所在主机的Socket中,该Socket通过与网络接口卡相连的传输介质将这段信息发送到另一台主机的Socket中,以供其他程序使用。 图1-1 TCP通信流程 2.TCP通信流程 TCP程序是面向连接的,程序运行后,服务器一直处于监听状态,客户端与

服务器通信之前必须首先发起连接请求,由服务器接收请求并在双方之间建立连接后才可以互相通信。 二、实验目的 1.了解Winsock API编程原理; 2.掌握TCP Socket程序的编写; 3.了解C/S模式的特点; 4.学会解决实验中遇到的问题。 三、实验任务 使用Winsock API相关类实现TCP Socket通信程序,并能成功运行。 四、实验环境及工具 1. Windows2000/XP/7 2. Visual C++开发平台 3. Visual Studio2010 五、实验内容和步骤 参照《Visual C++网络编程教程》书中81页,TCP Socket API程序设计。 连接: void CChatClientDlg::OnConnect() { WSADATA wsd; //WSADATA结构 WSAStartup(MAKEWORD(2,2),&wsd); //加载协议,使用Winsock 2.2版 m_client = socket(AF_INET,SOCK_STREAM,0); //创建流式套接字 //服务器地址 sockaddr_in serveraddr; UpdateData(); if(ServerIP.IsBlank()) { AfxMessageBox("请指定服务器IP!"); return; } if(sPort.IsEmpty()) { AfxMessageBox("请指定端口!"); return; }

实验二 8255A并行接口实验

实验二 8255A并行接口实验(一) 一实验目的 1、掌握通过8255A并行口传输数据控制LED发光二极管的亮灭;进一 步熟悉软件编程环境。 二实验设备 1、微机系统一套; 2、TPC-3型微机接口实验系统一台; 3、导线若干。 三实验内容 1、基础部分:用8255A的A端口控制8个LED发光二极管的亮和灭(端口 输出为1则亮,输出为0则灭)。其中L0―L2为东西方向,L5―L7为南北 方向、L3-L4不用,PA口与相应的发光二极管驱动信号输入端相连,输入端 为1时发光二极管亮。接线如图4-5所示。 图4-5 编制程序,通过8255A控制发光二极管,以模拟交通灯的管理。 2.提高部分:利用开关K0,K1的控制,以模拟几种交通灯的管理,具体要求 为: K0K1灯控制 00正常运行 01南北路口绿灯亮、东西路口红灯亮 10东西路口绿灯亮、南北路口红灯亮 3.如果模拟车流量大小来来决定红绿灯交通时间,请问你有什么解决办法。如果 能解决请加以解释并编程调试。

四、编程提示: 1.要完成本实验,首先必须了解交通灯的亮灭规律。设有一个十字路口,南北、东西方向初始态为四个路口的红灯全亮。之后,南北路口的绿灯亮,东西 路口的红灯亮,南北路口方向通车。延迟一段时间后,南北路口的绿灯熄灭, 而南北路口的黄灯开始闪烁。闪烁8次后,南北路口的红灯亮,同时东西路口 的绿灯亮,东西路口方向开始通车。延迟一段时间后,东西路口的绿灯熄灭, 而黄灯开始闪烁。闪烁苦干次后,再切换到南北路口方向。之后,重复上述过 程。 2.程序中应设定好8255A的工作模式,使三个端口均工作于方式0,并处于输出态 3.8255A的A端口地址为:288H B端口地址为:289H C端口地址为:28AH 控制口地址为:28BH 五、实验要求: 1.做好实验预习和准备工作,并写出预习报告(要求写出实验的流程图及程序),熟练掌握8255A编程原理及编程方法。 2.实验操作的最低要求是要做出实验内容的基础部分,然后根据实际操作能力争取做出实验内容的提高部分及回答实验内容的第三部分问题。 3.写出实验报告,内容为: 1)实验目的; 2)实验设备; 3)实验中遇到的问题及解决问题的分析思路与办法,问题定位及问题的性质; 4)对本实验的建议及有何创新。 ;这是自动生成的代码模板 STACKS SEGMENT STACK ;堆栈段 DW 128 DUP(?) ;注意这里只有128个字节 STACKS ENDS DATAS SEGMENT ;数据段 ;请在这里定义您的数据 DATAS ENDS CODES SEGMENT ;代码段 ASSUME CS:CODES,DS:DATAS START: MOV AX,DATAS ;初始化 MOV DS,AX

VC++网络编程之实例篇

一个简单的论坛灌水工具 我在https://www.sodocs.net/doc/ab702352.html,/index.php?prog=topic::flat&tid=219030里面回复了这样一个贴: 标题是:Re:啥时候下雪啊 回复内容是:下啊下啊 经过截取后,得到这样的数据包: POST /index.php?prog=topic::reply&tid=219030 HTTP/1.1..Accept: image/gif, image/x-xbitmap, image/jpeg, image/pjpeg, */*..Referer: https://www.sodocs.net/doc/ab702352.html,/index.php? prog=topic::flat&tid=219030..Accept-Language: zh-cn..Content-Type: application/x-www-form- urlencoded..Accept-Encoding: gzip, https://www.sodocs.net/doc/ab702352.html,er-Agent: Mozilla/4.0 (compatible; MSIE 6.0; Windows NT 5.1)..Host: https://www.sodocs.net/doc/ab702352.html,..Content-Length: 509..Connection: Keep-Alive..Cache- Control: no-cache..Cookie: CEFS=56a4967e3f0923cc0b9e361d2599290f.... title=Re%3A%C9%B6%CA%B1%BA%F2%CF%C2%D1%A9%B0% A1&cetag=checked&autoParseURL=checked&smiles=checked&showsign=checked&domai ns=https://www.sodocs.net/doc/ab702352.html, &q=Google+Site+Search&sitesearch=https://www.sodocs.net/doc/ab702352.html,&client=pub- 9549696168596987&forid=1&channel=5833732144&ie=GB2312&oe=GB2312&cof=GALT%3A %23008000%3BGL% 3A1%3BDIV%3A%23336699%3BVLC%3A663399%3BAH%3Acenter%3BBGC%3AFFFFFF%3BLBGC%3A 336699%3BALC% 3A0000FF%3BLC%3A0000FF%3BT%3A000000%3BGFNT%3A0000FF%3BGIMP%3A0000FF%3BFORID %3A1%3B&hl=zh- CN&content=%CF%C2%B0%A1%CF%C2%B0%A1&parentid=0

VGA显示控制

基于FPGA 的VGA显示控制 摘要 VGA(Video Graphics Array)即视频图形阵列,是IBM公司1987年推出的一种传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛应用。 本次课程设计是基于FPGA和主芯片为 EP4CE30F23C8N的ALTER公司的开发板Cyclone IV来实现的。数字图像信息在VGA接口显示器正确、完整地显示,涉及到时序的构建和数字图像信息的模拟化两方面,提出一种能够广泛应用的VGA显示接口方案,详细阐述了数字图像数据DA转化并输出到VGA接口显示器显示的方法,其中包括接口的硬件设计、视频DA转换器的使用方法、通过FPGA构造VGA时序信号的方法等等。方案可以应用于各种仪器,数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等。 课设主要用到的芯片是ADV7123,它是一款高速、高精度数模转换芯片。拥有三路十位D/A转换器,能够将代表颜色的数据锁存到数据寄存器中,然后通过D/A 转换器转换成模拟信号输出,得到我们要的色彩。

VGA显示的硬件设计和原理 1.1 FPGA主芯片 课程设计所用开发板的主芯片是EP4CE30F23C8N——Cyclone IV,其由Altera公司开发,值得注意的是该开发板所支持的QUARTUS II的版本较高,并且11.0的版本较12.0的版本编译好的程序更好下载。 图-1 1.2 ADV7123 实现VGA的控制显示主要用到的芯片就是ADV7123,ADV7123由完全独立的三个I0位高速D/A转换器组成,RGB(红绿蓝)视频数据分别从R9~R0、G9~G0、B9~B0输入,在时钟CLOCK的上升沿锁存到数据寄存器中,然后经告诉D/A转换器转换成模拟信号。三个独立的视频D/A转换器都是电流型输出,可以接成差分输出,也可以接成单端输出。DE2-115上按单端输出,在模拟输出端用75欧姆电阻接地,以满足工业标准。低电平有效的BLANK信号为复合消隐信号,当BLANK为低电平时,模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略。BLANK和SYNC都是在CLOCK 的上升沿被锁存的。 图-2是ADV7123的功能原理图:

8255并行口实验实验报告

8255并行口实验实验报告 作者: 一、实验目的 掌握8255A的编程原理。 二、实验设备 CPU挂箱、8086CPU模块。 三、实验内容 8255A的A口作为输入口,与逻辑电平开关相连。8255A的B口作为输出口,与发光二极管相连。编写程序,使得逻辑电平开关的变化在发光二极管上显示出来。 四、实验原理介绍 本实验用到两部分电路:开关量输入输出电路和8255可编程并口电路。 五、实验步骤 1、实验接线 CS0?CS8255; PA0~PA7?平推开关的输出K1~K8; PB0~PB7?发光二极管的输入LED1~LED8。 2、编程并全速或单步运行。 3、全速运行时拨动开关,观察发光二极管的变化。当开关某位置于L 时,对应的发光二极管点亮,置于H时熄灭。 六、实验提示 实验也是如此。实验中,8255A工作于基本8255A是比较常用的一种并行接口芯片,其特点在许多教科书中均有介绍。8255A有三个8位的输入输出端口,通常将A端口作为输入用,B端口作为输出用,C端口作为辅助控制用,本输入输出方式(方式0)。 七、实验结果 程序全速运行后,逻辑电平开关的状态改变应能在LED上显示出来。例如:K2置于L位置,则对应的LED2应该点亮。 八、程序框图(实验程序名:t8255.asm)

开始 设置8255工作方式 读A口 输出至B口 结束 九、程序源代码清单: assume cs:code code segment public org 100h start: mov dx,04a6h ;控制寄存器地址 mov ax,90h ;设 置为A口输入,B口输出 out dx,ax mov al,0feh start1:mov dx,04a2h 芯片的 入口地址 out dx,al mov bl,al mov dx ,04a0h in al,dx test ax,01h jz strat2 mov al ,bl rol al,1 流水灯循环左移 mov bl,al mov cx,3000h 设置cx为灯闪烁时间对应的循环次数 add: loop add jmp start1 无条件跳转至start1 strat2:mov al,bl mov dx,04a2h out dx,al ror al,1 流水灯循环左移 mov bl, al mov cx,3000h add1: loop add jmp start 无条件跳转至start code ends end start 十、实验总结 通过该实验,掌握了8255A的编程原理,学会了用汇编语言来编写程序控制8255A进行流水灯的操作实验。

数电实验-vga图像显示控制

数字电路综合实验 报告 学校:北京邮电大学 学院:信息与通信工程学院 专业:通信工程 班级:2008211115 学号:08210460 班内序号:30 姓名:唐秋月 2011年1月5日

VGA图像显示控制器 一、摘要和关键词 摘要:VGA显示屏显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。通过控制扫描计数器不同值时对RGB三原色信号的控制,来完成显示设计。 关键词:行列扫描行列同步RGB三原色控制 二、设计任务要求 实验目的 1. 熟练掌握VHDL 语言和QuartusII 软件的使用; 2. 理解状态机的工作原理和设计方法; 3. 掌握利用EDA 工具进行自顶向下的电子系统设计方法; 4. 熟悉VGA 接口协议规范。 实验要求: 设计一个VGA 图像显示控制器,达到如下功能: 显示模式为640×480×60HZ 模式; 用拨码开关控制R、G、B(每个2 位),使显示器可以显示64种纯色; 在显示器上显示横向彩条信号(至少6 种颜色); 在显示器上显示纵向彩条信号(至少8 种颜色); 在显示器上显示自行设定的图形、图像等。 选做:自拟其它功能。 三、实验原理 1、显示控制原理 常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。VGA显示控制器控制CRT显示图象的过程如图1所示

实验十三 8255A 并行接口实验

实验十三8255A 并行接口实验 一、实验目的 1、学习并掌握8255A的各种工作方式及其应用。 2、学习在接口实验单元上构造实验电路。 3、掌握8255A工作于中断方式的应用。 二、实验设备 1、EAT598实验教学系统一台。 2、连接线若干。 三、实验内容 8225A可编程并行接口芯片 8255A可编程外围接口芯片是Intel公司生产的通用可编程并行I/O接口芯片,它具有A、B、C三个8位并行接口,用+5V单电源供电,有三种工作方式: 方式0——基本输入/出方式 方式1——选通输入/出方式 方式2——双向选通工作方式 c82590 equ 200h c82591 equ 201h d8255a equ 210h d8255b equ 211h c8255 equ 213h stack segment stack dw 64 dup(?) stack ends code segment assume cs:code,ss:stack start: cli mov dx,c8255 mov al,86h out dx,al mov al,05h push ds mov ax,0000h ;修改中断向量表内容 mov ds,ax mov ax,offset ir0 mov si,0020h mov [si],ax

mov ax,8100h ;程序的加载段地址为8100h mov si,0022h mov [si],ax pop ds mov al,13h mov dx,c82590 out dx,al nop nop mov al,8 mov dx,c82591 out dx,al nop nop mov al,3 out dx,al nop nop mov al,0 out dx,al nop nop again: sti hlt jmp again ir0: mov dx,d8255b in al,dx mov dx,d8255a out dx,al iret code ends end start 四、报告要求 1、总结8255A可编程并行接口芯片的编程方法 (1)将DIP8开关SA9拨向ON系统状态,8255A的片选信号CS8255接译码器的输出210H,地址为210H~213H; (2)端口B输入线PB0~PB7接一组开关K0~K7; (3)端口A输出线PA0~PA7接至一组发光二极管L0~L7。. 编写程序,使8255A端口A工作在方式0并作为输出口,端口B工作于方式1并作为输入口,则端口C的PC2成为选通信号输入端 STB,PC0成为中断请求信号输出端INTRb。 B 当B口数据就绪后,通过发 STB信号来请求CPU读取端口B数据并送端口A输出显示。 B

基于FPGA的VGA图像显示与控制

基于FPGA的VGA图像显示与控制 课程要求:采用verilog语言,基于FPGA的VGA图像显示,即能够在显示器上实现动态彩色图像的显示。 VGA显示接口的理论分析:硬件采用CycloneII系列的EP2C20Q240C8N,它含有240个引脚。对于VGA的显示器遵循800*600@75模式,其中800是指每行中显示的像素的个数,而600是指屏幕每一列所包含的像素的个数。 VGA工业标准规定了具体地,在扫描过程中的时序图如下: 行扫描时序图 场扫描时序图 每场信号对应625个行周期,其中600行为图像显示行,每场有场同步信号,该脉冲宽度为3个行周期的负脉冲;每行显示行包括1056个点时钟,其中800点为有效显示区,每行有一个行同步信号的负脉冲,该脉冲宽度为80个点时钟。这样我们可以知道,行频为625*75=46857Hz。需要的点时钟的频率为:625*1056*75=49.5MHz约为50MHz。由上图可知,实际上在真正的实现过程中,每一行扫描所花的时间实际上比显示一行的像素所花的时间多了1056-800=256个像素点。同理,每一场的扫描时间多了625-600=25个行时间。 设计思路: 我们采用BmpToMif工具把BMP格式的图像转换为.mif文件。利用QuartusII7.2自带的MegaWizard Plug-In Manager产生一个ROM存储器,并用其来初始时.mif 文件。即将图像文件写入到存储器里面。然后利用编程来控制图像的显示。 设计步骤: 1、工程创建:创建一个Project取名字为vga,在创建工程的向导中选着CycloneII 系列的EP2C20Q240C8。 2、代码书写:新建一个Verilog HDL File编写程序代码如下: `timescale 1ns/1ps module tupian (clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b,addr); input clk,rst_n;

算法程序设计实验报告

程序设计》课程设计 姓名:王 学号:20100034 班级:软件工程00 班 指导教师:王会青 成绩: 2010年 6 月 实验一.构造可以使n 个城市连接的最小生成树 专业:__软件工程___ 班级:__软件姓名:_王___ 学号:_20100034 完成日期:_2010/6/26 ________ 一、【问题描述】给定一个地区的n 个城市间的距离网,用Prim 算法或Kruskal 算法建立最小生成树,并计算得到的最小生成树的代价。 1 城市间的道路网采用邻接矩阵表示,邻接矩阵的存储结构定义采用课本中给出的定义,若两个城市之间不存在道

路,则将相应边的权值设为自己定义的无穷大值。 2 显示出城市间道路网的邻接矩阵。 3 最小生成树中包括的边及其权值,并显示得到的最小生成树的总代价。 4 输入城市数、道路数→输入城市名→输入道路信息→执行Kruskal 算法→执行Prim 算法→输出最小生成树 二、【问题分析】 1. 抽象数据类型结构体数组的定义: #ifnd ef ADJACENCYMATRIXED// 防止该头文件被重复引用 #define ADJACENCYMATRIXED // 而引起的数据重复定义 #define INFINITY 32767 // 最大值∞ #define MAX_VERTEX_NUM 20 // 最大顶点个数 typedef int VRType; // 权值,即边的值 typedef char InfoType; // 附加信息的类型,后面使用时会定义成一个指针 typedef char VertexType[MAX_VERTEX_NUM]; // 顶点类型 typedef enum {DG=1, DN, UDG, UDN} GraphKind; //{ 有向图,有向网,无向图,无向网} typedef struct ArcCell { VRType adj; //VRType 是顶点关系类型。对无权图,用1 或0 表示相邻否;对带权图,则为权值类型。 InfoType*info; // 该弧关系信息的指针

8255并行接口实验

8255并行接口实验 4.5.1 实验目的 1. 学习并掌握8255的工作方式及其应用。 2. 掌握8255典型应用电路的接法。 3. 掌握程序固化及脱机运行程序的方法。 4.5.2 实验设备 PC 机一台,TD-PITE 实验装置或TD-PITC 实验装置一套。 4.5.3 实验内容 1. 基本输入输出实验。编写程序,使8255的A 口为输入,B 口为输出,完成拨动开关到数据灯的数据传输。要求只要开关拨动,数据灯的显示就发生相应改变。 2. 流水灯显示实验。编写程序,使8255的A 口和B 口均为输出,数据灯D7~D0由左向右,每次仅亮一个灯,循环显示,D15~D8与D7~D0正相反,由右向左,每次仅点亮一个灯,循环显示。 4.5.4 实验原理 I/O I/O I/O I/O PA7-PA0 PC7-PC4 PC3-PC0 PB7-PB0 图4.31 8255内部结构及外部引脚图 并行接口是以数据的字节为单位与I/O 设备或被控制对象之间传递信息。CPU 和接口之间的数据传送总是并行的,即可以同时传递8位、16位或32位等。8255可编程外围接口芯片是Intel 公司生产的通用并行I/O 接口芯片,它具有A 、B 、C 三个并行接口,用+5V 单电源供电,能在以下三种方式下工作:方式0--基本输入/输出方式、方式1--选通输入/输出方式、方式2--双向选通工作方式。8255的内部结构及引脚如图4.31所示,8255工作方式控制字和C 口按位置位/复位控制字格式如图4.32所示。

位(a )工作方式控制字 (b )C 口按位置位/复位控制字 1 图4.32 8255控制字格式 8255实验单元电路图如图4.33所示: 图4.33 8255实验单元电路图 4.5.5 实验步骤 1. 基本输入输出实验 本实验使8255端口A 工作在方式0并作为输入口,端口B 工作在方式0并作为输出口。用一组开关信号接入端口A ,端口B 输出线接至一组数据灯上,然后通过对8255芯片编程来实现输入输出功能。具体实验步骤如下述: (1)实验接线图如图4.34所示,按图连接实验线路图。 (2)编写实验程序,经编译、连接无误后装入系统。 (3)运行程序,改变拨动开关,同时观察LED 显示,验证程序功能。 (4)点击“调试”下拉菜单中的“固化程序”项,将程序固化到系统存储器中。 (5)将短路跳线JDBG 的短路块短接到RUN 端,然后按复位按键,观察程序是否正常运行;关闭实验箱电源,稍等后再次打开电源,看固化的程序是否运行,验证程序功能。 (6)实验完毕后,请将短路跳线JDBG 的短路块短接到DBG 端。

socket网络编程小例子

服务器端程序: #include

网络编程实验报告

网络编程技术实验报告 一实验目的: 网络编程技术是计算机科学与技术专业、网络工程专业、软件工程专业的一门专业基础课程。本课程以Java技术为主讲授,Java语言是当前最流行的网络编程语言。本课程是一门实用性和综合运用性都很强的课程,实践教学环节是教学过程中必不可少的重要内容。通过实验,让学生熟悉JDK中的主要内容,掌握用JDK调试和运行程序的方法,掌握网络编程的基本思想和开发方法、面向对象编程的思想,JA V A中的基本方法和技术,能够熟练使用JA V A设计、编写程序,特别是基于TCP/IP的Socket 编程,并能运用这些知识方法完成C/S和B/S结构程序的设计工作。通过实验,提高学生使用Java语言程序设计开发的能力,提高应用面向对象技术分析和解决实际问题的能力,并在此基础上强化学生的实践意识、提高其分析问题、解决问题的能力以及动手能力和创新能力。 二实验要求 要求学生熟悉JDK中的主要内容,掌握用JDK调试和运行程序的方法,掌握网络编程的基本思想和开发方法、面向对象编程的思想,JAVA中的基本方法和技术,能够熟练使用JAVA设计、编写程序,特别是基于TCP/IP的Socket编程,并能运用这些知识方法完成C/S和B/S结构程序的设计工作。要注意培养学生良好的编程习惯,自始至终贯彻课程中所介绍的程序设计风格。为保证尽量在统一安排的上机时间内完成程序设计任务,学生应事先做问题分析,并做静态检查。学生应记录实验中所遇到的问题,并写出详细的实验报告。课前准备上机程序,上机认真调试,课后撰写实验报告,实验报告包括实验目的、实验内容、源程序、实验结果及分析。

. 实验一java基本语法 实验目的: 了解Java的数据类型,掌握各种变量的声明方式,理解运算符的优先级,掌握Java基本数据类型、运算符与表达式,掌握顺序结构、选择结构和循环结构语法的程序设计方法。 实验要求: 1、编写一个声明Java不同数据类型变量的程序。 2、编写使用不同选择结构的程序。 3、编写使用不同循环结构结构的程序。 实验内容: 1、编写一个声明Java不同数据类型变量的程序。 public class DataTypes { public static void main(String args[]) { byte b=127; short s=32767; int i=2147483647; long l=9223372036l;//为什么long表示的数比Int还小? char c='c'; float f=1.23F; double d=0.9E-3; boolean bool=true; System.out.println(" b="+b); System.out.println(" s="+s); System.out.println(" i="+i); System.out.println(" l="+l); System.out.println(" c="+c); System.out.println(" f="+f); System.out.println(" d="+d); System.out.println(" bool="+bool); }