MPS笔试

1.What’s the difference of synchronous and asynchronous circuit? 同步电路和异步电路的区别是什么?

同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化斗鱼所加的时钟脉冲信号同步。

异步电路:电路中没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态与时钟同步,而其他的触发器的状态变化不与时钟脉冲同步。

2.How to synchronize the asynchronous signal? 异步信号如何进行同步?

对于一位的异步信号可以使用“一位同步器进行同步”(使用两级触发器),而对于多位的异步信号,可以采用如下方法:

1:可以采用保持寄存器加握手信号的方法(多数据,控制,地址);

2:特殊的具体应用电路结构,根据应用的不同而不同;

3:异步FIFO。(最常用的缓存单元是DPRAM)

3.What’s the setup and hold time? 建立时间和保持时间的概念

建立时间:触发器在时钟上升沿到来之间,其数据输入端的数据保持稳定的最小时间

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据保持稳定的最小时间

4.What’s the difference of the LATCH and DFF? 描述LATCH和DFF的概念和区别?

LATCH:电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

DFF:也叫双稳态门,又称双稳态触发器(能在0和1两种状态下维持稳定)。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发。

区别:

1)锁存器电平触发会把输入端的毛刺带入输出;触发器由于边沿作用可以有效抑制输入端干扰。

2)锁存器没有时钟信号,而触发器有时钟触发信号。

3)锁存器是异步的,输入信号改变后,输出信号也随改变。触发器是一个同步版锁存器。触发器泛指一类电路结构,它可以由触发信号(如:时钟、置位、复位等)改变输出状态,并保持这个状态直到下一个或另一个触发信号来到时。触发信号可以用电平或边沿操作,锁存器是触发器的一种应用类型。

4)dff是边沿触发的,而latch是电平触发的。锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

5.The clock cycle is T, the clock to register output delay is T co, setup and hold time of register are T setup and T hold, what’s

the T delay constrain? 时钟周期为T,时钟到寄存器输出延时T co,寄存器建立时间T setup,寄存器保持时间T hold。

描述逻辑延时T delay的建立和保持时间要求?

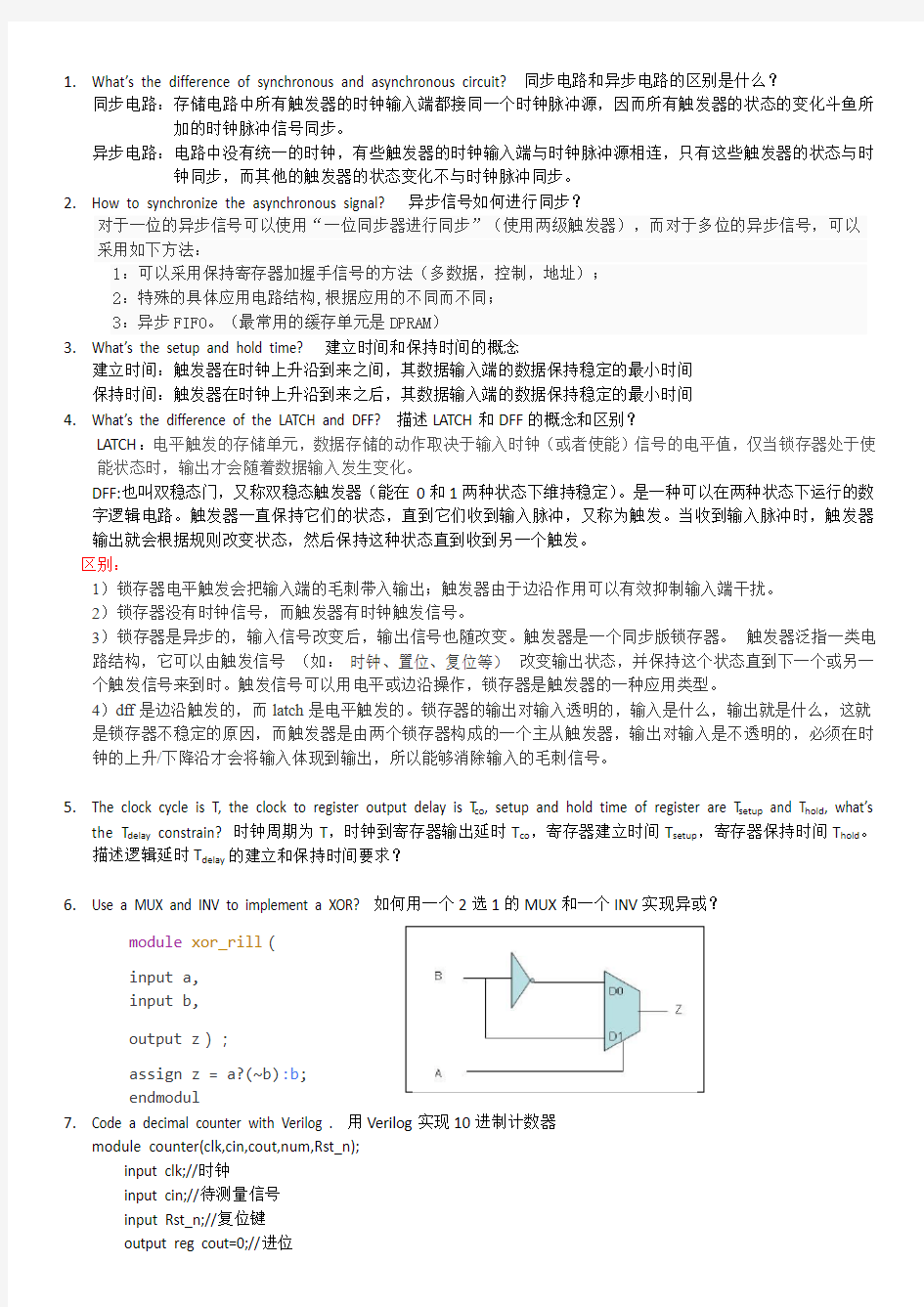

https://www.sodocs.net/doc/b211317823.html,e a MUX and INV to implement a XOR? 如何用一个2选1的MUX和一个INV实现异或?

module xor_rill(

input a,

input b,

output z);

assign z = a?(~b):b;

endmodul

7.Code a decimal counter with Verilog .

用Verilog实现10进制计数器

module counter(clk,cin,cout,num,Rst_n);

input clk;//时钟

input cin;//待测量信号

input Rst_n;//复位键

output reg cout=0;//进位

output reg [3:0] num=0;//输出要显示数字,BCD码

always@(posedge cin or posedge clk or negedge Rst_n)

if(!Rst_n) num=0;

else if(clk) num=0;//一个周期内,有半个周期clk==0,故用0.5hz,周期2s,半周期1s

else if(num==9)begin

num<=0;cout<=1;

end

else begin

num<=num+1;cout<=0;

end

endmodule

8.Code the divider by 3 with Verilog (50%duty cycle). 用Verilog设计一个3分频器,要求50%占空比

Module div_3(clk,rst_n,clk_o);

Input clk,rst_n;

Output reg clk_o;

Reg[1:0] cnt;

Parameter cnt_num=2;

Always @(posedge clk or negedge rst_n)

If(rst_n==1’b0)begin

Cnt<=0;clk_o<=0;end

Else if(cnt==cnt_num)begin

Cnt<=0;clk_o<=~clk_o;end

Else begin

Cnt<=cnt+1;clk_o<=clk_o;end

endmodule

9.Draw the state machine transmission diagram of the array detection 10010, code with Verilog and build the testbench

and testcase to get 100% fsm coverage. 画出可以检测10010序列的状态图,并用Verilog实现,搭建测试平台并写出可以达到100%状态机覆盖率的testcase

10.Describe the digital P&R flow. 简述数字后端P&R流程

11.What’s IR-drop, in while area will be easy to have IR-drop problem? 什么是IR-drop,在哪些地方容易出IR-drop问题

IR压降是指出现在集成电路中电源和地网络上电压下降或升高的一种现象

IR压降可能是局部或全局性的。当相邻位置一定数量的逻辑门单元同时有逻辑翻转动作时,就引起局部IR压降现象,而电源网格某一特定部分的电阻值特别高时,例如R14远远超出预计时,也会导致局部IR压降;当芯片某一区域内的逻辑动作导致其它区域的IR压降时,称之为全局现象。

IR压降问题的表现常常类似一些时序甚至可能是信号的完整性问题。如果芯片的全局IR压降过高,则逻辑门就有功能故障,使芯片彻底失效,尽管逻辑仿真显示设计是正确的。而局部IR压降比较敏感,它只在一些特定的条件下才可能发生,例如所有的总线数据同步进行翻转,因此芯片会间歇性的表现出一些功能故障。而IR 压降比较普遍的影响就是降低了芯片的速度。试验表明,逻辑门单元上5%的IR压降将使正常的门速度降低15%。

12.What are gate-level simulations? You have a device that can be programmed via an I2C interface. What type of tests

do you recommend to run for gate level only? 如果你有一个设备通过I2C接口配置,有哪些针对门级仿真的测试用例?

13.There is an X present in my gate level simulation due to a timing violation. How do you identify the source of it and the

type of violation? 如果在后仿中波形中出现了X,如何去定位,且可能是什么问题?

14.What are the different sources of power consumption? Describe different techniques used to reduce power

15.What are various techniques to resolve routing congestion? 如何解决routing congestion问题?

16.Describe the ECO flow (including pre-mask ECO and post-mask ECO). 描述ECO流程,包括pre-mask ECO 和

post-mask ECO

ECO有两种,pre-mask ECO和post-mask ECO,它的分界线就是base layer tape out之前和之后。

pre-mask ECO的流程是

1)后端写出网表,给前端

2)前端修改这个网表 (一般不再做综合),可以使用任何标准单元(只要不是dont_use),交给后端

3)后端读入ECO网表,和ECO之前的place和route

4)ECO place&route,STA, DRC/LVS

post-mask ECO流程,假设你不想动base layer

1)后端写出网表,给前端

2)前端修改这个网表 (一般不再做综合),只能使用spare cell或者象gate array一样的ECO cell

3)后端读入ECO网表,和ECO之前的place和route

4)如果使用spare cell,不用ECO place;如果用ECO cell,要将ECO cell放在以前带gate array功能的fill cell的位置上,再按照指定的layer做ECOroute