EDA设计电子琴设计

九江学院

电子工程学院课程设计报告

课程名称:VHDL语言与EDA

设计题目:简易电子琴

专业:应用电子

班级: B0922 学生姓名: ******

学号: ****** 起止日期: 2011年11月7日~11月11日

指导教师:高老师

简易电子琴

设计要求

1)设计一个简易电子琴;

2)利用实验箱的脉冲源产生1,2,3,。。。共7个或14个音阶信号;

3)用指示灯显示节拍;

4)*能产生颤音效果。

1、方案论证与对比

1.1方案一

采用数字逻辑电路制作,用IC 拼凑焊接实现,这种电路很直观,简单方便。但应用数字逻辑电路制作的话,使用的器件较多,连接复杂,体积大,功耗大。电路中焊点和线路较多会,使成品的稳定度和精度大大降低。

1.2方案二

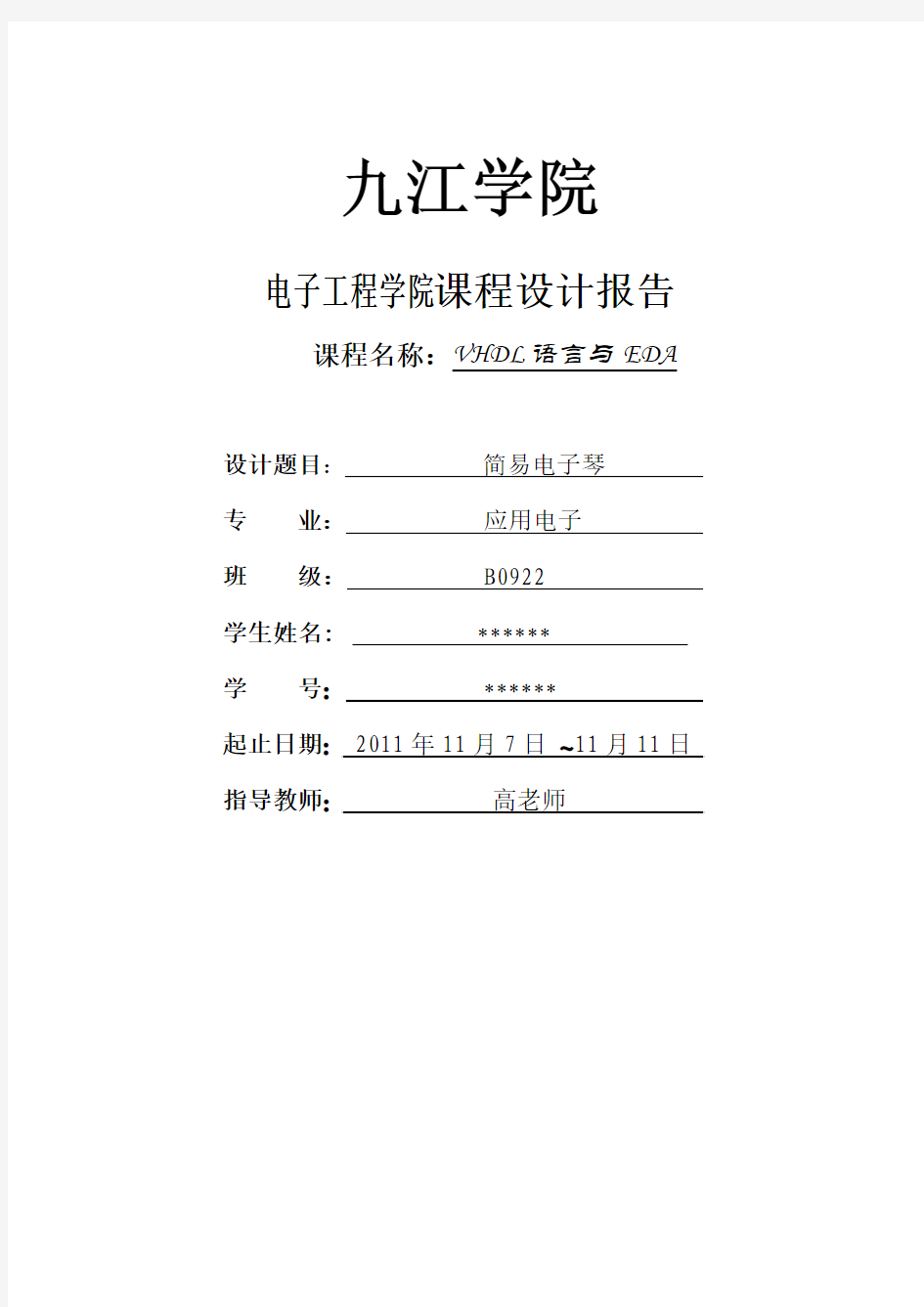

采用现场可编程逻辑器件(FPGA)制作,利用EDA软件中的VHDL硬件描述语言编程进行控制,然后烧制实现。采用FPGA来设计的原理图如图1.1所示。它由控制输入电路、FPGA、显示电路和扬声器电路组成。

图1.1 采用FPGA设计的电子琴原理方框图

控制输入电路主要是为用户设计的,起到一个输入控制的作用。FPGA是现场可编程逻辑器件,也是本设计方案的核心内容,它是实现电子琴运作的主要控制模块。由设计者把编好 VHDL程序烧制到现场可编程逻辑器件FPGA中,然后通过控制输入电路把乐谱输入到FPGA,产生不同的频率驱动扬声器,发出不同的乐谱。同时也把发出的乐谱符号通过显示器输出。

1.3方案三

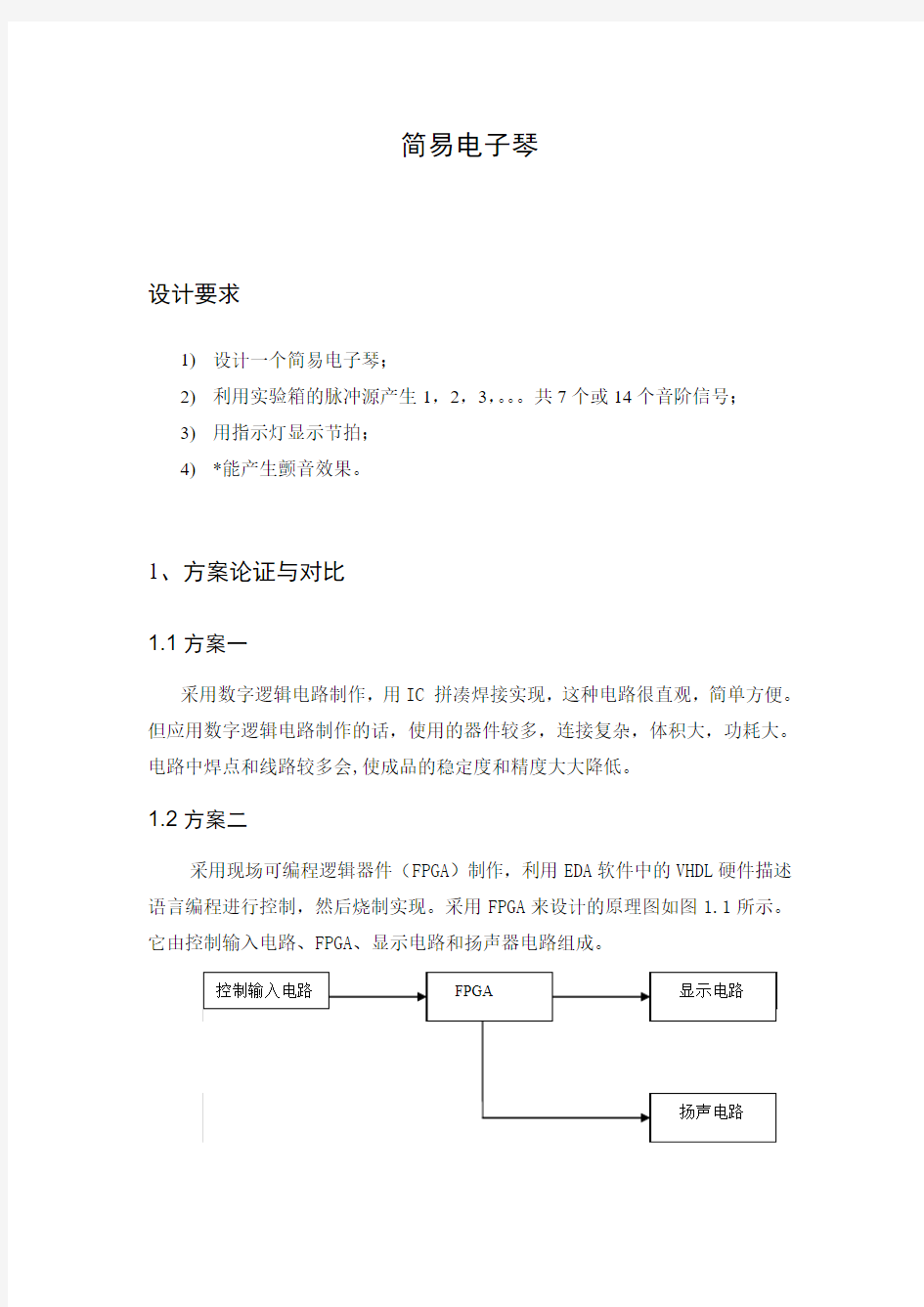

单片机现在已经达到很成熟的阶段了,它的应用也十分广泛。采用单片机来实现电子琴,它的原理方框图与用FPGA来实现的原理方框图类似,如图1.2所示。

图1.2 采用单片机实现电子琴的原理方框图

对于电子琴的设计,三个方案均可以实现,但是第一个方案中采用的是数字逻辑电路来制作,该电路硬件所需的器材多,体积庞大,比较复杂,而且精度和稳定度都不是很高。第二个方案采用的是现场可编程逻辑器件来实现, 它的优点是所有电路集成在一块芯片上,此方案所需的外围电路简单,这样它的体积就减少了,同时还提高了系统的稳定度。还可以用Modelsim XE 5.3d软件进行仿真和调试等。设计人员可以充分利用VHDL硬件描述语言方便的编程,提高开发效率,缩短研发周期,降低研发成本;而且易于进行功能的扩展,实现方法灵活,调试方便,修改容易。方案三也有它的优点,但同时也存在缺点。它对设计者的要求比较高,设计者对软硬件必须十分熟悉。和方案二来比它的实验仿真没有方案二简单直观,调试也有一定的难度。在外界环境相同的条件下,方案三设计出来的产品精度和稳定度要比方案二稍微差一些。因此,电子琴的设计我们选择方案二来实现。

2、各功能块电路及工作原理

2.1、实体部分

定义模块的输入输出引脚,包括按键、时钟输入引脚和扬声器输出。

entity speakera is

port( clk : in std_logic; --时钟输入

index:in std_logic_vector( 6 downto 0); -- 按键输入

spks: out std_logic); --扬声器输出

end;

2.2、节拍显示

将每个按键与一个led相串联,当按键按下时指示灯亮,按键松开时指示灯灭,来显示节拍。

图2.1 按键电路

2.3、频率选择模块

根据按键输入选择不同频率。

search : process (index)

begin

case index is

when "0000001" => tone <= "01100000101"; -- 1

when "0000010" => tone <= "01110010000"; --2

when "0000100" => tone <= "10000001100"; --3

when "0001000" => tone <= "10000101101"; --4

when "0010000" => tone <= "10010001010"; --5

when "0100000" => tone <= "10011011100"; --6

when "1000000" => tone <= "10100100010"; --7

when others => tone <= "11111111111";

end case;

end process;

2.4、分频模块

首先将输入的12M时钟信号12分频,得到时钟周期为1us的信号。

divdeclk :process(clk)

variable count4 :std_logic_vector( 3 downto 0);

begin

preclk <= '0';

if count4 > 11 then preclk <= '1'; count4 :="0000";

elsif clk'event and clk='1' then count4 := count4 + 1;

end if;

end process;

再根据输入的tone对应的音符计数得到相应的分频,并赋值给fullspks。

genspks : process(preclk,tone)

variable count11 : std_logic_vector( 10 downto 0);

begin

if preclk'event and preclk = '1' then

if count11 =16#7ff# then count11 := tone;fullspks <= '1';

else count11 := count11 + 1;fullspks <= '0';

end if;

end if;

end process;

2.5、扬声器输出模块

根据分频模块获得的fullspks信号,对输出进行取反,从而得到所需

要的调输出。

dealyspks : process( fullspks)

variable count2 : std_logic;

begin

if fullspks'event and fullspks = '1' then count2 := not count2;

if count2 = '1' then spks <= '1';

else spks <= '0';

end if;

end if;

end process;

end;

3、总结

VHDL的设计关键是电路逻辑设计,而一个程序的关键是总体设计。对于硬件设计接触不多的我们清楚这一点也许不无好处。

通过这个程序设计让我学会一种新的语言,对数字系统结构也有了更进一步的了解和认识,对我以后的学习有很大的帮助。希望其他人在看再做类似设计时有所借鉴。

设计的工作此课程设计从构思到最后完成的这一个周内,周围的很多同学和朋友给予了我善意的帮助,还有老师对我的不厌其烦的指导,使我对此类课程设计的设计流程以及脊髓有了很深的了解,通过你们的帮助,我把从计算机组成原理这门课上学到的理论第一次用到了实际设计上。在此,我深深的表示感谢。通过这次课程的设计,各方面都有了很大的提高,我对数据库软件EDA技术、VHDL、等系列知识都有了一定的了解。使用EDA 技术开发页面的能力也有了很大提高,比以前了解的更加的全面!