半导体工艺流程 总文档(1-10)

第一章概述

从20世纪后半叶开始电子技术的发展速度是令人膛目结舌的,许多传统由机械技术支持的产品逐步改由电子技术来支持,例如数字CD播放机取代了磁带播放机,汽车发动机也由电子点火系统控制,电子计算机已深入到社会的各方面。所有这些电子产品都离不开半导体器件,目前微电子技术已进入甚大规模集成电路和系统集成时代,微电子技术已经成了整个信息时代的标志和基础。

1.1半导体产业的发展

半导体制造技术很复杂,要求许多特殊工艺步骤、材料、设备以及供应产业。半导体产业发展的基础是真空管电子学、无线电通信、固体物理等理论。放大电子信号的三极真空管是由Lee De Forest于1906年发明的,三极管由三个部件构成,在一个抽空气体的玻璃容器中分别封入两个电极和一个栅极。为了使部件不被烧毁,同时还要保证电子能够在电极间传输,必须采用真空。真空管被用于开发第一台电子计算机(ENIAC),ENIAC重达50吨、占地3000平方英尺、需要19000只真空管,并且使用相当于160个灯塔的电量.ENIAC除了体积大之外,它的主要缺点是伴随着真空管出现的问题。真空管体积大、不可靠以及耗电量大。由于会烧毁,真空管寿命有限。为了迎合迅速发展的电子市场的需求来生产体积小、可靠的电子产品,真空管显然不是优选技术。1947年贝尔实验室的威廉2肖克利(William Shockley)\约翰2巴丁(John Bardeen)\和沃尔特2布拉顿(Walter Brattain)发明了固态晶体管。晶体管的名字取自“跨导”和“变阻器”两词,提供了与真空管同样的电功能,但具有固态的显著优点:尺寸小、无真空、可靠、重量轻、最小的发热及低功耗。这一发现发动了以固体材料和技术为基础的现代半导体产业。

1.2集成电路制造

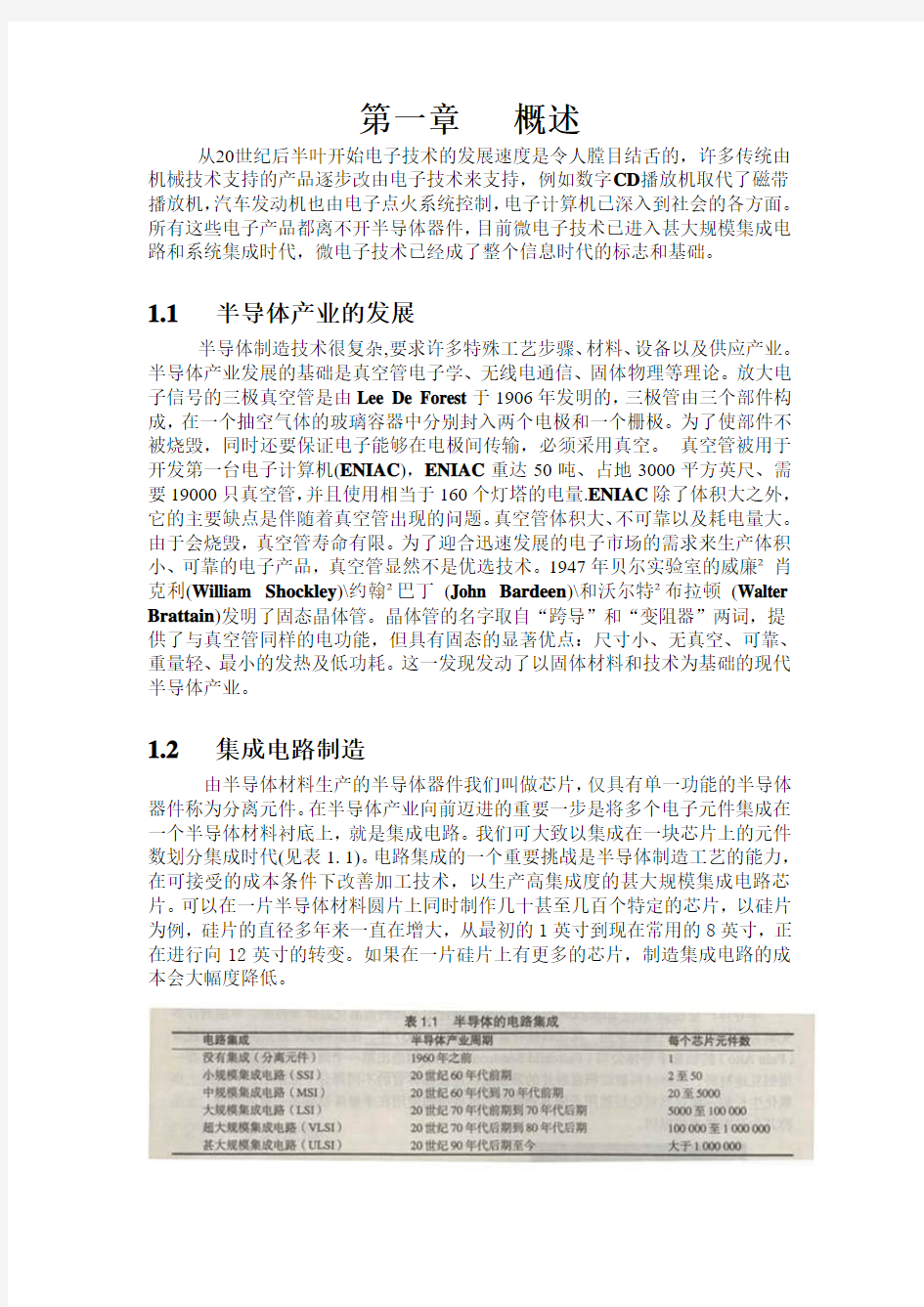

由半导体材料生产的半导体器件我们叫做芯片,仅具有单一功能的半导体器件称为分离元件。在半导体产业向前迈进的重要一步是将多个电子元件集成在一个半导体材料衬底上,就是集成电路。我们可大致以集成在一块芯片上的元件数划分集成时代(见表1.1)。电路集成的一个重要挑战是半导体制造工艺的能力,在可接受的成本条件下改善加工技术,以生产高集成度的甚大规模集成电路芯片。可以在一片半导体材料圆片上同时制作几十甚至几百个特定的芯片,以硅片为例,硅片的直径多年来一直在增大,从最初的1英寸到现在常用的8英寸,正在进行向12英寸的转变。如果在一片硅片上有更多的芯片,制造集成电路的成本会大幅度降低。

半导体器件的制作仅发生在接近硅片表面的几微米,在工艺加工过程中,硅片厚度提供硅片足够的强度。一旦器件在硅片上制作完毕,硅片上的金属线路层将作为器件和芯片外边的各种电信号之间的连接。

集成电路的制造步骤涉及五个制造阶段:

●硅片制备: 在第一阶段,将硅从沙中提炼并纯化,经过特殊工艺产生适当直径的硅锭,然后将硅锭切割成用于制造芯片的薄硅片。

●芯片制造: 裸露的硅片经过各种清洗、成膜、光刻、刻蚀和掺杂步骤,加工完的硅片具有永久刻蚀在硅片上的一整套集成电路。

●硅片测试/拣选: 每个芯片要进行探测和电学测试,拣选出可接受和不可接受的芯片,并为有缺陷的芯片做标记。

●装配与封装: 将制作好集成电路的硅片分割成单个芯片,好的芯片被压焊后密封在塑料或陶瓷壳内。

●终测: 为确保芯片的功能,要对每一个被封装的集成电路进行测试,以满足制造商的电学和环境的特性参数要求。

芯片技术的发展有三个主要趋势:

1.提高芯片性能判断芯片性能的一种通用方法是速度。器件做的越小,在芯片上放置得越紧密,芯片的速度就会提高。还有使用材料,通过芯片表面的电路和器件来提高电信号的传输。芯片性能的另一重要方面是在器件工作过程中的功耗。

摩尔定律 1964年,戈登2摩尔,半导体产业先驱者和英特尔公司的创始人,预言在一块芯片上的晶体管数大约每隔一年翻一翻,后来在1975年被修正为预计每18个月翻一翻。(图1.1)

2.提高芯片可靠性主要提高芯片寿命

3. 降低芯片成本减小特征尺寸\增加硅片直径

1.3可选择的半导体材料

根据流经材料电流的不同可分为三类材料: 导体;绝缘体;半导体。导体是电子容易以电流方式流过的材料,绝缘体是对电流通过具有很高阻值的材料,半导体这种材料很特殊,因为它既能充当导体也能充当绝缘体。半导体材料具有

较小的禁带宽度,其值介于绝缘体和导体之间。这个禁带宽度允许电子在获得能量时从价带跃迁到导带。这种行为在半导体被加热时发生,因而其导电性随温度增加而提高(对导体而言则正相反)。广泛用于半导体产业的各族元素特性概括于表1.2。

1.4 在半导体制造业中的职业

半导体制造业中的职业途径分成三个主要方面:技师、工程师和管理人员。

硅片制造技师: 负责操作硅片制造设备,从事一些设备维护以其工艺和设备的基本故障查询。

设备技师: 负责查询故障并维护先进设备系统,以保证在硅片制造过程中设备能正确运行。

设备工程师: 专门从事确定设备设计参数和优化硅片生产的设备性能。

工艺技师: 通过查询与工艺相关的问题支持生产设备和工艺工程组。

工艺工程师: 负责分析制造工艺和设备的性能以确定优化参数设置。

现场服务代表: 安装制造设备,进行设备维护、诊断及修理以确保设备有效的生产。

实验室技师: 从事工艺开发的工作,建立新工艺并进行试验。

成品率/失效分析技师: 从事与缺陷分析相关的工作,例如准备待分析的材料并操作分析设备以确定在硅片制造过程中引起问题的根源。

成品率提高工程师: 负责收集并分析成品率及测试数据以提高硅片制造性能。

设施技师: 负责支持设施设备以及硅片制造厂要求的设施,包括化学材料管理和净化间设施。

设施工程师: 负责为硅片制造厂的化学材料、净化空气及常用设备的基础设施提供工程设计支持。

主管/经理: 负责将技术技能和人事管理技能结合在一起以达到公司的组织目标。

第二章硅和硅片制备

硅是用来制造芯片的主要半导体材料,也是半导体产业中最重要的材料。锗是第一个用做半导体的材料,它很快被硅取代了,这主要有四个原因:1)硅的丰裕度:硅是地球上第二丰富的元素,占到地壳成分的25%,经合理加工,硅能够提纯到半导体制造所需的足够高的纯度而消耗更低的成本。

2)更高的熔化温度允许更宽的工艺容限:硅1412℃的熔点远高于锗937℃的熔点,使得硅可以承受高温工艺。

3)更宽的工作温度范围:用硅制造的半导体元件可以用于比锗更宽的温度范围。

4)氧化硅的自然生成:硅表面有自然生长氧化硅(SiO2)的能力。SiO2是一种高质量、稳定的电绝缘材料,而且能充当优质的化学阻挡层以保护硅不受外部沾污。

现在,全世界芯片的85%以上都是由硅来制造的。

2.1半导体级硅

用来做芯片的高纯硅被称为半导体级硅(semiconductor-grade silicon), 或者SGS,有时也被称做电子级硅。从天然硅中获得生产半导体器件所需纯度的SGS要分几步。现介绍一种得到SGS的主要方法:

第一步,在还原气体环境中,通过加热含碳的硅石(SiO2),一种纯沙,来生产冶金级硅。

SiC(固体)+SiO2(固体)→Si(液体)+SiO(气体)+CO(气体)

在反应式右边所得到的冶金级硅的纯度有98%。由于冶金级硅的沾污程度相当高,所以它对半导体制造没有任何用处。

第二步,将冶金级硅压碎并通过化学反应生成含硅的三氯硅烷气体。

Si(固体)+3HCl(气体)→SiHCl3(气体)+H2(气体)+加热

第三步,含硅的三氯硅烷气体经过再一次化学过程并用氢气还原制备出纯度为99.9999999%的半导体级硅。

2SiHCl3(气体)+2H2(气体)→2Si(固体)+6HCl(气体)

这种生产纯SGS的工艺称为西门子工艺。(图2.1)半导体级硅具有半导体制造要求的超高纯度,它包含少于百万分之(ppm)二的碳元素和少于十亿分之(ppb)一的Ⅲ、Ⅴ族元素(主要的掺杂元素)。然而用西门子工艺生产的硅没

有按照希望的晶体顺序排列原子,所以也不能用在半导体制造中。

2.2晶体结构

不仅半导体级硅的超高纯度对制造半导体器件非常关键,而且它也要有近乎完美的晶体结构。只有这样才能避免对器件特性非常有害的电学和机械缺陷。

单晶就是一种固体材料,在许多的原子长程范围内原子都在三维空间中保持有序且重复的结构。

非晶材料是指非晶固体材料,它们没有重复的结构,并且在原子级结构上体现的是杂乱的结构。非晶硅对半导体器件所需的硅片来讲是没有任何用处的,这是因为器件的许多电学和机械性质都与它的原子级结构有关,这就要求重复性的结构使得芯片与芯片之间的性能有重复性。

在晶体材料中,对于长程有序的原子模式最基本的实体就是晶胞。晶胞在三维结构中是最简单的由原子组成的重复单元,它给出了晶体结构。图2.2表示了由晶胞组成的三维结构。因为晶体结构在三维方向上是等同的,晶胞有一个框架结构,像一个立方体。在自然界有7种可能存在的晶体结构。对于硅晶体来说,它的晶胞是面心立方结构,如图2.3。

如果晶胞不是有规律地排列,那么这种材料就叫做多晶材料。如果从提纯工艺中得到的半导体级硅是多晶结构,就叫做多晶硅。如果晶胞在三维方向上整齐地重复排列,那这样的结构就叫单晶。半导体芯片加工需要纯净的单晶硅结构,这是因为晶胞重复的单晶结构能够提供制作工艺和器件特性所要求的电学和机械性质。

晶胞在晶体中的方向称为晶向。晶向非常重要,因为它决定了在硅片中晶体结构的物理排列是怎样的。不同晶向的硅片的化学、电学和机械性质都不一样,这会影响工艺条件和最终的器件性能。半导体制造中硅片常用的晶向是<100>、<111>、<110>。

2.3单晶硅生长

晶体生长是把半导体级硅的多晶硅块转换成一块大的单晶硅。生长后的单晶硅称为硅锭。在生产用于硅片制备的单晶硅锭最普遍的技术是Czochralski法,也称CZ法。另外还有区熔法。

2.3.1 CZ法

CZ法生长单晶硅把熔化了的半导体级硅液体变为有正确晶向并且被掺杂成n型或p型的固体硅锭。85%以上的单晶硅是采用CZ法生长出来的。CZ拉单晶炉见图2.4。

坩锅里的硅被拉单晶炉加热,使用电阻加热或射频(RF)加热线圈。电阻加热用于制备大直径的硅锭。当硅被加热时,它变成液体,叫做熔体。一个完美的具有所需要晶向的籽晶硅接触到直拉装置并开始生长新的晶体结构。籽晶放在熔体表面并在旋转过程中缓慢地拉起,它的旋转方向与坩锅的旋转方向相反。随着籽晶在直拉过程中离开熔体,熔体上的液体会因为表面张力而提高。籽晶上的界面散发热量并向下朝着熔体的方向凝固。随着籽晶旋转着从熔体里拉出,与籽晶有同样晶向的单晶就生长出来了。不同的硅锭生长结果依赖于籽晶和坩锅各自的旋转方向及速度。

2.3.2 区熔法

区熔法生长单晶硅锭是把掺杂好的多晶硅棒铸在一个模型里。一个籽晶固定

到一端然后放进生长炉中。用射频线圈加热籽晶与硅棒的接触区域。加热多晶硅棒是区熔法最主要的部分,因为在熔融的晶棒的单晶界面再次凝固之前只有30分钟的时间。晶体生长中的加热过程沿着晶棒的轴向移动。区熔法示意如图2.5。

区熔法硅片直径要比直拉法小,由于不用坩锅,区熔法生长的硅纯度高且含氧量低。

2.3.3追求更大直径硅锭的原因

硅锭直径从20世纪50年代初期的不到25mm增加到现在的300mm,硅片直径的历史发展趋势如图解2.6所示。更大直径的硅锭对硅锭生长中正确的晶体生长和保持良好的工艺控制提出了挑战。随着制备硅锭复杂度的增加,为什么还要继续增加硅片的直径呢?是因为增加硅片直径给硅片制备带来的成本利润。更大直径硅片有着更大的表面积来做芯片,这样就会在一个硅片上生产更多的芯片。这带来三大好处: 1)每块芯片的加工和处理时间减少了,导致设备生产效率提高;2)硅片边缘的芯片少了,转化为更高的生产成品率;3)由于在同一工艺过程中有更多的芯片,设备的重复利用率提高了。

2.4 硅中的晶体缺陷

为了很好地实现先进IC功能,半导体要求有近乎完美的晶体结构。晶体缺陷就是在重复排列的晶胞结构中出现的任何中断。

缺陷密度:在工艺过程中,由于各种原因在每平方厘米硅片上产生的缺陷数目。

研究硅晶体缺陷是非常重要的,因为它对半导体的电学特性有破坏作用。这些问题包括二氧化硅介质击穿和漏电流等。随着器件尺寸的缩小以及有源栅区面积的增加,更多的晶体管集成在一块芯片上,缺陷出现在芯片敏感区域的可能性就会增加。这样的缺陷对器件的成品率有负面影响。

晶体缺陷会产生于晶体生长和后面硅锭和硅片的各项工艺中。一些缺陷是因为表面损伤而造成的,例如由于机械操作造成的裂痕的表面缺陷。在硅中主要存在三种普遍的缺陷形式:

1.点缺陷:原子层面的局部缺陷。点缺陷存在于晶格的特定位置。图2.7显示了三种点缺陷。最基本的一种缺陷是空位。这种缺陷当一个原子从其格点位置移动到晶体表面时出现。另一种点缺陷是间隙原子,它存在于晶体结构的空隙中。当一原子离开其格点位置并且产生了一个空位时,就会产生间隙原子-空位对,或叫Frenkel缺陷。

随着器件技术变得越来越复杂,半导体硅中的点缺陷也越来越重要。在晶体生长中影响点缺陷产生的因素是生长速率和晶体熔体界面间的温度梯度。如果晶体冷却速率得到控制,就会有效减少缺陷的产生。半导体制造中的热处理也能导致点缺陷的产生。

另一种点缺陷是由于化学元素杂质引入到格点里所产生的(只要是氧和碳)。在制备过程中杂质的引入可能是有目的的,也可能是无意的。他们能占用原有原子的位置,成为替位杂质,或者在间隙中成为间隙杂质。

2. 位错:错位的晶胞。见图 2.8。打个比方,就象整齐排列的一推砖有一层沿一个方向发生了错位。位错可以在晶体生长和硅片制备过程中的任意阶段产生。然而发生在晶体生长之后的位错通常由作用在硅片上的机械应力所造成,例如不均匀的受冷或受热以及超过硅片承受范围的应力。一些情况下,位错是由器件制作过程中硅片表面的热氧化所引入的。

3.层错:晶体结构的缺陷。层错与晶体结构有关,经常发生在晶体生长过程中。滑移就是一种层错,它沿着一个或更多的平面发生滑移(见图2.9)。

另一种层错是孪生平面,就是在一个平面上,晶体沿着两个不同的方向生长(见图2.10)。这种孪生平面是因为在生长过程中的热影响或机械振动而产生的。在每一边生长的晶体都可能很完美。无论是滑移还是孪生平面都是半导体制造中不能接受的。

2.5硅片制备

硅是硬而脆的材料,晶体生长后的圆柱形的单晶硅锭要经过一系列的处理过程,最后形成硅片,才能达到半导体制造的严格要求。这些硅片制备步骤包括机械加工、化学处理、表面抛光和质量测量。硅片制备的基本流程如图2.11所示。

由于芯片设计和制造要求的不断提高,硅片的制备工艺必须能提供符合更严格规范要求的硅片。这些要求包括硅片的几何尺寸(直径、平整度和翘曲度)、表面完美性(粗糙度和光的散射性)和洁净度(颗粒的源)。这些规范会带来诸如自动材料传送中的尺寸控制或者达到IC生产中关键工艺步骤所要求的表面状况等问题。

一.整型处理整型处理包括在切片之前对单晶硅锭做的所有准备步骤。

1)去掉两端两端通常叫籽晶端和非籽晶端。当两端被切掉后,可用四探针来检查电阻以确定整个硅锭达到合适的杂质均匀度。

2)径向研磨由于在晶体生长中直径和圆度的控制不可能很精确,所以硅锭都要长得稍大一点以进行径向研磨。对半导体制造中流水线的硅片自动传送来讲,精确的直径控制是非常关键的。

3)硅片定位边或定位槽在硅锭上做一个定位边来标明晶体结构和硅片的晶向。主定位边标明了晶体结构的晶向,如图2.12所示。还有一个次定位边标明硅片的晶向和导电类型。六吋以下的硅片都是如此定位的。八吋及以上的硅片已采用定位槽,具有定位槽的硅片在硅片背面靠近边缘的区域有激光刻上的关于硅片的信息。如图2.13所示。

二.切片将整型处理后的硅锭切成一片片的硅片。对200mm及以下硅片来讲,切片是用带有金刚石切割边缘的内圆切割机来完成的。对300mm的硅片要由线

切割机来进行。线切割比内圆切割产生更多的硅片,但内圆切割能产生平整的切面。

三.磨片和倒角切片完成后,进行双面的机械磨片以去除切片时留下的损伤,达到硅片两面高度的平行及平坦。在硅片制备过程的许多步骤中,平整度是关键

的参数。硅片边缘倒角可使硅片边缘获得平滑的半径周线。在硅片边缘的裂痕和

小裂缝会在硅片上产生机械应力并会产生位错,尤其是在硅片制备的高温过程中。平滑的边缘半径能将这些影响降到最小。

四.刻蚀硅片整型使硅片表面和边缘损伤及沾污,损伤的深度一般有几微米深,硅片刻蚀是一个利用化学刻蚀选择性去除表面物质的过程。硅片经过湿法化学刻

蚀工艺消除硅片表面损伤和沾污。

五.抛光制备硅片的最后一步是化学机械平坦化(CMP),也叫抛光。它的目

标是高平整度的光滑表面,以满足半导体器件制备的需要。

2.6外延层

在某些情况下,需要硅片有非常纯的与衬底有相同晶体结构(单晶)的硅

表面,还要保持对杂质类型和浓度的控制。这要通过在硅表面淀积一个外延层来

达到。在硅外延中,硅基片作为籽晶在硅片上面生长一薄层硅。新的外延层会复

制硅片的晶体结构。由于衬底硅片是单晶,外延层也是单晶。而且,外延层可以

是n型也可以是p型,这并不依赖于原始硅片的掺杂类型。外延层通常是没有

沾污的。

硅外延发展的起因是为了提高双极器件和集成电路的性能。外延可以在重掺杂的衬底上生长一层轻掺杂的外延层。这在优化pn结的击穿电压的同时降低了集电极电阻,在适中的电流强度下提高了器件速度。

2.7硅中杂质

在实际集成电路制造中所需要的绝大多数半导体材料,都人为地掺入一定数量的某种原子(杂质),以便控制导电类型和导电能力.这种人为掺入杂质的半导体,就是通常所说的杂质半导体,掺入的杂质主要是ⅢA族元素(受主元素)和ⅤA族元

素(施主元素)。这些杂质在硅晶体中一般是替代硅原子而占椐晶格位置,并能在适当的温度下施放电子或空穴,控制和改变晶体的导电能力和导电类型(n型或p 型)。

如果在硅中同时存在浅施主和浅受主两种杂质,这时它的导电类型要由杂质浓度高的那种杂质决定,它首先要补偿掉不同类型的杂质,剩余部分才对导电能力有贡献。

杂质在硅中并不能无限制的掺入,在一定的温度和平衡态下,它有一个溶解到硅中的最大浓度,这就是杂质在硅晶体中的溶解度,也称固溶度。固溶度是随着温度而变化的。

2.8 质量测量

一.物理尺寸为了达到芯片生产中器件制造的要求以及适合硅片制造厂自动传送设备的要求,硅片必须规定物理尺寸。在硅片的制备中,尺寸控制和检查包括许多测量,例如直径、厚度、晶向位置和尺寸、定位边(或定位槽)和硅片形变。二.平整度平整度是硅片最主要的参数之一,主要因为光刻工艺对局部位置的平整度是非常敏感的。硅片平整度是指在通过硅片的直线上的厚度变化。它是通过硅片的上表面和一个规定参考面的距离得到的。平整度可以规定为硅片上一个特定点周围的局部平整度,也可以规定为整体平整度。

三.微粗糙度微粗糙度是实际表面同规定平面的小数值范围的偏差。它测量了硅片表面最高点和最低点的高度差别,它的单位是纳米。对芯片制造来讲,表面微粗糙度的控制非常重要,这是因为在器件制造中,它对硅片上非常薄的介质层的击穿有着负面影响。

四.氧含量控制硅锭中的氧含量水平和均匀性是非常重要的,而且随着更大的直径尺寸,难度也越来越大。少量的氧能起到俘获中心的作用,它能束缚硅中的沾污物(主要是金属离子)。然而,硅锭中过量的氧会影响硅的机械和电学特性。目前硅片中的氧含量被控制在24到33ppm。

五.晶体缺陷为了使前面讨论的各种晶体缺陷减到最少,必须对硅加以控制。目前要求每平方厘米的晶体缺陷少于1000个。

六.颗粒硅片表面颗粒的数量应该加以控制,使在芯片制造中的成品率损失降到最低。典型的硅片洁净度规范是在200mm的硅片表面每平方厘米少于0.13个颗粒。测量到的颗粒尺寸要大于或等于0.08微米。

七.体电阻率硅锭的体电阻率依赖于在晶体生长前掺杂到硅熔体中的杂质浓度。理想的要求是在整个体硅中得到均匀的电阻率。实际上由于晶体生长过程中半径方向存在温度梯度,使硅锭沿半径方向的掺杂浓度不同。

第三章半导体制造中的化学品半导体制造业使用大量的化学品来制造硅圆片。另外化学品也被用于清洗硅

圆片和处理在制造工艺中使用的工具。在硅圆片制造中使用的化学材料被称为工

艺用化学品,它们有不同种类的化学形态并且要严格控制纯度。为了理解工艺化

学品,我们先复习一下基础化学里面的一些概念。

3.1物质形态

宇宙中的所有物质都存在三种基本形态:固态、液态或气态。另外还有第

四种形态:等离子体。

固体有其自己固定的形状,不会随着容器的形状而改变。液体随着容器的形状而改变自己的形状。液体会填充容器的相当于液体体积大小的区域,并会形成表面。气体也随着容器的形状而改变自己的形状,但气体会充满整个容器,不会形成表面。气体微粒小且能够自由移动。一些气体像氢气和氧气,是活性气体,很容易与其他气体或元素反应形成稳定的化合物。而另外一些气体像氦气和氩气,是惰性气体。很难形成化合物。由于惰性气体不与其他化学材料反应,所以被广泛用于半导体制造业中。当有高能电离的分子或原子的聚集体存在时就会出现等离子体。这种形态与前三种物质形态有相当大的不同。举例来说,恒星、荧光灯和霓虹灯都是等离子体。将一定的气体曝露在高能电场中,就能诱发等离子态。我们在随后的章节中将会看到等离子体被广泛用于半导体制造业中。

3.2材料的属性

材料属性有两类,化学属性和物理属性。材料的物理属性是指那些通过物质本身而不需要与其他物质相互作用反映出来的性质。物理属性有:熔点、沸点、电阻率和密度等。材料的化学属性是指那些通过与其他物质相互作用或相互转变而反映出来的性质。化学属性有:可燃性、反应性和腐蚀性。

3.2.1半导体制造中的化学属性

在制造硅集成电路芯片中有许多不同种类的化学品和化学材料。化学品的一些属性对于理解新的半导体工艺材料的存在有很重要的意义,这些属性有:温度、密度、压强和真空、表面张力、冷凝、热膨胀、蒸气压、应力、升华和凝华。一.温度温度是比较一个物质相对于另外一个物质是冷还是热的量度标准,因此它也是物质分子或原子平均动能或热能的量度标准。不同温度的物体之间传递的能量叫热。硅圆片制造中大量需要处理在高温下的情况,比如需要加热来影响化学反应或者对硅单晶结构退火使原子重新排列。

二.密度物质的密度被定义为它的质量(或重量)除以它的体积。硅的密度是2.3。

三.气体的压强和真空气体充满容器的体积并且施加相同的压强于容器的器壁上,压强为施加在表面单位面积上的压力。压强是在半导体制造中被广泛使用的属性。如果容器内的气体压强小于14.7psi,则存在真空。真空通过抽出密闭容器中的气体分子来获得低于大气压的压强。在半导体制造中,一些制造工艺在大气压下进行,一些需要很高的压强而另外一些需要在真空环境中进行。

四.表面张力当一滴液体在一个平面上,液滴存在着一个接触表面积(见图3.1)液滴的表面张力是增加接触表面积所需的能量。随着表面积的增加,液体分子必须打破分子间的引力,从液体内部运动到液体的表面,因此需要能量。表面张力的概念用在半导体制造中来衡量液体均匀涂在硅圆片表面的粘附能力。

五.冷凝和汽化气体变成液体的过程被称做冷凝,从液体变成气体的相反过程叫汽化。

六.热膨胀当一个物体被加热时,由于原子的振动加剧,它的体积就会发生膨胀。衡量材料热膨胀大小的参数是热膨胀系数(CTE)。非晶材料的热膨胀是各向同性的,而所有晶体材料,比如单晶硅,热膨胀是各向异性的。

七.蒸气压蒸气压是在密闭容器中气体分子施加的压力,这时汽化和冷凝的速率处于动态平衡。

八.应力当一个物体受到外力的作用时就会产生应力。在硅圆片中有多种原因可以导致应力的产生。硅片表面的物理损伤;位错、多余的空隙和杂质产生的应力;外界材料生长都可以产生应力。如果两个热膨胀系数(CTE)相差很大的物体结合在一起,然后加热,由于两种材料以不同的速率膨胀导致它们彼此推拉,因而产生应力。由于CTE不匹配产生的应力会使硅片弯曲。在半导体制造工艺中由于微芯片采用多层不同的CTE材料的平面工艺,所以非常关心这种应力。九.升华和凝华固体通过升华过程能够直接变成气体,气体直接变成固体的过程叫凝华。

3.3工艺用化学品

半导体制造业是与化学密切相关的工艺过程,其中使用了多种超高纯度的工艺用化学品。化学品在半导体制造业中的主要用途有:

●用湿法化学溶液和超纯净的水清洗或准备硅片表面。

●用高能离子对硅片进行掺杂得到p型和n型硅材料。

●淀积不同的金属导体层以及导体层之间必要的介质层。

●生长薄的二氧化硅层作为MOS器件主要的栅极介质材料。

●用等离子体增强刻蚀或湿法试剂有选择地去除材料并在薄膜上形成所需要的图形。

一.酸

在半导体制造过程中使用了多种酸。表3.1列出了一些常用的酸及其在硅片加工中的特定用途。

二.碱

表3.2列出了在半导体制造过程中通常会使用的碱性物质。

三.溶剂

表3.3列出了硅片厂常用的溶剂。

去离子水是在半导体制造过程中广泛使用的溶剂,在它里面没有任何导电的离子。去离子水的pH值为7,既不是酸性也不是碱性,是中性的。它能够溶解其他物质,包括许多离子化合物和共价化合物。

四.化学品的输送

在半导体工业中使用的化学品有很多是有毒性并且危险的化学品安全、高纯度和不间断地从存储罐中输送到工艺工具是至关重要的。对于液态化学品来说,这种输送过程是通过批量化学材料配送(BCD)系统完成的。

BCD系统是由化学品源(如一个存储罐)、化学品输送模块和管道系统所组成的(见图3.2)。BCD系统的存储罐常常建造在主要生产线的地下,输送模块用来过滤、混合和输送化学品,然后通过管道系统将化学药输送到独立的工艺线。现代的BCD系统是一个集成了计算机和网络化的系统,它能够对化学品的输送进行实时监控。

怎样来存储和输送工艺用化学品取决于这些因素:化学品的兼容性、减少化学品的沾污和安全性。在半导体制造过程中对化学品纯度的要求是超高纯净(UHP),对杂质的控制是要低于十亿分之一(ppb)到万亿分之一(ppt)的范围之内。

并不是所有的化学品都这样来输送的,一些化学品并不适合由BCD系统来输送,它们或者是使用的数量很少或者是在使用前存放的时间长度有限。为了使这些化学品能够在工艺站点存储和使用,将用特别的包装系统便于它们定点输

送。

五.气体

半导体制造过程中大概使用了50余种不同种类的气体。由于不断有新的材料被引入到半导体制造过程中,所以气体的种类和数量是不断发生变化的。气体通常被分成两类:通用气体和特种气体。

所有气体都要求有极高的纯度,通用气体要控制在7个9以上的纯度(99.99999%), 特种气体则要控制在4个9以上的纯度(99.99%)。气体中的杂质微粒要控制在0.1μm之内,其他需要控制的沾污是氧、水分和痕量杂质,例如金属。许多工艺气体都具有毒性、腐蚀性、活性和自燃(暴露在空气中燃烧)。因此,在硅片厂气体是通过气体配送系统(BGD)以安全、清洁和精确的方式输送到不同工艺站点的。见图3.3。

表3.4和表3.5分别列出了在半导体制造过程中用到的一些通用气体和特种气体以及它们的用途。

第四章IC制造中的沾污控制一个硅片表面具有多个芯片,每个芯片有差不多数以百万计的器件和互连线路,它们对沾污都非常敏感。为使芯片上的器件功能正常,避免硅片制造中的沾污是绝对必要的。

为了控制制造过程中不能接受的沾污,半导体产业开发了净化间。净化间本质上是一个净化过的空间,它以超净空气把芯片制造与外界的沾污环境隔离开来,包括化学品、人员和常规的工作环境。

4.1沾污的类型

沾污是指半导体制造过程中引入半导体硅片的任何危害芯片成品率及电学性能的不希望有的物质。沾污经常导致有缺陷的芯片,致命缺陷是导致硅片上的芯片无法通过电学测试的原因。据估计80%的芯片电学失效是由沾污带来的缺陷引起的。

净化间沾污分为五类:颗粒、金属杂质、有机物沾污、自然氧化层、静电释放。

一.颗粒

颗粒是能粘附在硅片表面的小物体。在半导体制造过程中,颗粒能引起电路开路或短路。它们能在相邻导体间引起短路。颗粒还可以是后续各节讨论的其他类型沾污的来源。

半导体制造中,可以接受的颗粒尺寸的粗略法则是它必须小于最小器件特征尺寸的一半。大于这个尺寸的颗粒会引起致命的缺陷。例如0.18微米的特征尺寸不能接触0.09微米以上尺寸的颗粒。为了有个感性认识,人类头发的直径约为90微米,0.09微米的尺寸则比人类头发尺寸小1000倍之多。

硅片表面的颗粒密度代表了特定面积内的颗粒数。更高的颗粒密度产生致命缺陷的机会也更大。颗粒检测已经广泛采用激光束扫描硅片表面和检测颗粒散射的光强及位置来进行。

二.金属杂质

危害半导体工艺的典型金属杂质是碱金属,即周期表中的ⅠA族元素,因为它们容易失去一个价电子成为阳离子,与非金属的阴离子反应形成离子化合物。金属在所有用于硅片加工的材料中都要严格控制。表4.1列出了一些典型的金属杂质元素。

金属来自于化学溶液或者半导体制造中的各种工序。另一种金属沾污的来源是化学品同传输管道和容器的反应。金属可以通过两种途径淀积在硅片表面上。第一种途径,金属通过金属离子与位于硅片表面的氢离子的电荷交换而被束缚在硅表面。这些典型的金属杂质很难消除。第二种途径,当表面氧化时金属杂质分布于氧化层内。在氧化层中的金属杂质只有通过去除硅片表面的氧化层来去除。

金属离子在半导体材料中是高度活动性的,被称为可动离子沾污(MIC)。当MIC引入到硅片中时,在整个硅片中移动,严重损害器件电学性能和长期可靠性。未经处理过的化学品中的钠是典型的、最为普遍的MIC之一,人充当了它的运送者。人体以液态形式包含了高浓度的钠(例如唾液、眼泪、汗液等)。钠沾污在硅片加工中被严格控制。

金属杂质导致了半导体制造中器件成品率的减少,引起氧化物-多晶硅栅结构中的结构性缺陷、pn结上泄漏电流的增加以及少数载流子寿命的减少。MIC 沾污能迁移到栅结构中的氧化硅界面,改变开启晶体管所需的阈值电压。由于它们的性质活泼,金属离子可以在电学测试和运输很久以后沿着器件移动,引起器件在使用期间失效。

三. 有机物沾污

有机物沾污是指那些包含碳的物质,几乎总是同碳自身及氢结合在一起,有时也和其他元素结合在一起。有机物沾污的一些来源包括细菌、润滑剂、蒸气、清洁剂、溶剂和潮气等。在特定工艺条件下,微量有机物沾污能降低栅氧化层材料的致密性。工艺过程中有机材料给半导体表面带来的另一个问题是表面的清洗不彻底,这种情况使得诸如金属杂质之类的沾污在清洗之后仍完整保留在硅片表面。

四. 自然氧化层

如果曝露于室温下的空气或含溶解氧的去离子水中,硅片的表面将会被氧化。这一薄氧化层称为自然氧化层。

自然氧化层将妨碍其它工艺步骤,如硅片上单晶薄膜的生长和超薄栅氧化层的生长。自然氧化层也包含了某些金属杂质,它们可以向硅中转移并形成电学缺陷。在金属导体的接触区如果有自然氧化层存在,将增加接触电阻,减少甚至可能阻止电流流过。

五. 静电释放

静电释放(ESD)也是一种形式的污染,因为它是静电和从一个物体向另

一个物体未经控制的转移,可能损坏芯片。ESD产生于两种不同静电势的材料接触或摩擦。带过剩负电荷的原子被相邻的带正电荷的原子吸引,这种由吸引产生的电流泄放电压可以高达几万伏。

半导体制造中特别容易产生静电释放,因为硅片加工保持在较低的湿度中,典型条件为40%±10%相对湿度,这种条件容易使静电荷生成。尽管ESD发生时转移的静电总量通常很小(纳库仑级别),然而放电的能量积累在硅片上很小的一个区域内。发生在几个纳秒内的ESD能产生超过1A的峰值电流,简直可以蒸发金属导体连线和穿透氧化层。放电也可以成为栅氧化层击穿的诱因。ESD 带来的另一个重大问题是,一旦硅片表面有了电荷积累,它产生的电场就能吸引带电颗粒或极化并吸引中性颗粒到硅片表面。随着器件关键尺寸的缩小,ESD 对更小颗粒的吸引变得重要起来,能产生致命缺陷。

4.2 沾污的源与控制

半导体器件制造厂房存在7种沾污源:空气、人、厂房、水、工艺用化学品、工艺气体和生产设备。

一.空气

净化间最基本的概念是硅片工厂空气中的颗粒控制。我们通常所呼吸的空气是不能用于半导体制造的,因为它包含了太多的漂浮沾污。这些微小的浮质在空气中漂浮并停留很长时间,淀积在硅片表面引起沾污并带来致命缺陷。

净化级别标定了净化间的空气质量级别,它是由净化室空气中的颗粒尺寸和密度表征的。这一数字描绘了要怎样控制颗粒以减少颗粒沾污。表4.2展示了不同净化间净化级别每立方英尺可以接受的颗粒数和颗粒尺寸。

近来已经开始使用0.1级,这时颗粒尺寸缩小到0.02~0.03μm。最新的净化空气标准对每立方米空气中的超细颗粒数也做了规定,称为“U”描述符。U描述符把直径小于0.1μm的颗粒规定为超细颗粒。在没有特别说明具体颗粒尺寸的情况下,U描述符把洁净度定义为U(x),其中x是每立方米空气中可容许的超细颗粒的最大数。

二.人

人是颗粒的产生者。人员持续不断地进出净化间,是净化间沾污的最大来源。颗粒来自于头发和头发用品、衣物纤维屑、皮屑等。一个人平均每分钟释放一千万个尺寸等于或大于0.3μm的颗粒。通常的人类活动,如谈话、咳嗽、打喷嚏,对半导体都是有害的。

为实现净化间内的超净环境,人员必须穿上超净服。超净服由兜帽、连衣裤工作服、靴子和手套组成,完全包裹住了身体。超净服的作用有:1)对身体产生的颗粒和浮质的总体抑制;2)超净服系统颗粒零释放;3)对ESD的零静电积累;4)无化学和生物残余物的释放。

对于要进入净化间的人员必须遵循净化间操作规程。主要有:经过风淋和鞋清洁器才能进入净化间;只把必需物品带入净化间;缓慢移动;始终确保所有的头部和面部头发被包裹起来;始终都保持超净服闭合。

三.厂房

为使半导体制造在一个超洁净的环境中进行,有必要采用系统方法来控制净化间区域的输入和输出。在净化间布局、气流流动模式、空气过滤系统、温度和湿度的设定、静电释放等方面都要进行完美的设计,同时尽可能减少通过设备、器具、人员、净化间供给引入的颗粒和持续监控净化间的颗粒,定期反馈信息及维护清洁。

四.水

为了制造半导体,需要大量的高质量、超纯去离子水(DJ)。我们平时使用的来自于自来水厂的生活用水含有大量的沾污而不能用于硅片生产。经过处理之后,DJ中不允许有的沾污是:溶解离子、有机材料、颗粒、细菌、硅土和溶解氧。同时在25℃下,DJ的电阻率要达到18MΩ-cm。一个水净化系统见图4.1。

五.工艺用化学品

无论是液态化学品还是气体化学品,都必须不含沾污。然而,处理和传送系统有可能引入杂质,所以在靠近使用现场安置过滤器。一个优秀的过滤器应该不对所需的流量产生显著的压力衰减,不引入二次沾污并与化学品相容。过滤效率是指停留在过滤器中特定尺寸以上的颗粒的百分比。对于ULSI工艺中使用的液体过滤器,对于0.2微米以上颗粒的典型效率为99.9999999%。

六.生产设备

用来制造半导体硅片的生产设备是硅片工厂中最大的颗粒来源。在硅片制造过程中,硅片从片架重复地转入设备中,经过多台装置的操作,卸下返回到片架中,又被送交下一工作台。为了制造一个硅片,这一序列重复达450次或更多的次数,把硅片曝露在不同设备的许许多多机械和化学加工过程中。这就需要特殊的设计考虑以避免沾污。有用输送带系统和升降机来传送硅片、用封闭洁净的片架装硅片、建立一个微环境来加工硅片等等。

4.3 硅片湿法清洗

硅片表面在经受工艺之前必须是洁净的。一旦硅片表面被沾污,沾污物必须通过清洗而排除。硅片清洗的目标是去除所有表面沾污:颗粒、有机物、金属和自然氧化层。每一工步骤都是硅片上器件潜在的沾污源。对于整个ULSI制造工艺,单个硅片表面要湿法清洗大约上百次。

占统治地位的硅片表面清洗方法是湿化学法,工业标准湿法清洗工艺称为RCA清洗工艺。用在湿法清洗中的典型化学品以及它们去除的沾污列于表4.3。

从表中可以看到,颗粒和有机物通过SC-1去除,金属通过SC-2去除,而自然氧化层通过DHF去除。在湿法清洗时还可加入一些辅助方法以增强清洗效果,例如兆声清洗,喷雾清洗,刷洗器等等。

现在已经研究出几种可以取代RCA清洗的清洗技术,像等离子体干法清洗、使用螯合剂、臭氧、低温喷雾清洗等,但在工业生产上还未大量应用。

第五章测量学和缺陷检查

(放在工艺结束后讲)

测量学是关于确定尺寸、数量和容积的测量的科学。测量学指的是在工艺流程中为了确定硅片的物理和电学特性的技术与过程。用于制造中的测量学使用测试设备和传感器来收集并分析关于硅片参数和缺陷的数据。对硅片性能的精确评估必须贯穿于制造工艺,以验证产品满足规范要求。要达到这一点,在硅片制造的每一工艺步骤都有严格的质量测量,为使芯片通过电学测试并满足使用中的可靠性规范,质量测量定义了每一步需要的要求。

5.1集成电路测量学

集成电路测量学是测量制造工艺的性能以确保达到质量规范标准的一种必要的方法。为了完成这种测量,需要样片、测量设备和分析数据的方法。

数据是在监控片(又称样片)上收集,为表征工艺的特性,样片包含在工艺流程中。而使用实际生产硅片模拟更接近在工艺流程中发生的情况,可以提供更好的信息。

用于性能测量的测量设备有不同的类型,分为与工艺分离的独立测试设备和与工艺设备集成在一起的测量设备。独立的测试设备进行测量学测试时,不依附于工艺,但通常对硅片有破坏性或沾污。集成的测量仪器具有传感器,这些传感器允许测试工具作为工艺的一部分起作用并发送实时数据。

成品率是一个硅片工厂生产高质量管芯能力的重要标志。为了查出不同缺陷怎样影响硅片的成品率,缺陷分析应该能区分出随机因素和非随机因素,并能与

半导体工艺流程

1清洗 集成电路芯片生产的清洗包括硅片的清洗和工器具的清洗。由 于半导体生产污染要求非常严格,清洗工艺需要消耗大量的高纯水; 且为进行特殊过滤和纯化广泛使用化学试剂和有机溶剂。 在硅片的加工工艺中,硅片先按各自的要求放入各种药液槽进行表面化学处理,再送入清洗槽,将其表面粘附的药液清洗干净后进入下一道工序。常用的清洗方式是将硅片沉浸在液体槽内或使用液体喷雾清洗,同时为有更好的清洗效果,通常使用超声波激励和擦片措施,一般在有机溶剂清洗后立即米用无机酸将其氧化去除,最后用超纯水进行清洗,如图1-6所示。 图1-6硅片清洗工艺示意图 工具的清洗基本米用硅片清洗同样的方法。 2、热氧化 热氧化是在800~1250C高温的氧气氛围和惰性携带气体(N2)下使硅片表面的硅氧化生成二氧化硅膜的过程,产生的二氧化硅用以作为扩散、离子注入的阻挡层,或介质隔离层。典型的热氧化化学反应为: Si + O2 T SiO2

3、扩散 扩散是在硅表面掺入纯杂质原子的过程。通常是使用乙硼烷(B2H6)作为N —源和磷烷(PH3)作为P+源。工艺生产过程中通常 分为沉积源和驱赶两步,典型的化学反应为: 2PH3 —2P+3H2 4、离子注入 离子注入也是一种给硅片掺杂的过程。它的基本原理是把掺杂物质(原子)离子化后,在数千到数百万伏特电压的电场下得到加速,以较高的能量注入到硅片表面或其它薄膜中。经高温退火后,注入离子活化,起施主或受主的作用。 5、光刻 光刻包括涂胶、曝光、显影等过程。涂胶是通过硅片高速旋转在硅片表面均匀涂上光刻胶的过程;曝光是使用光刻机,并透过光掩膜版对涂胶的硅片进行光照,使部分光刻胶得到光照,另外,部分光刻胶得不到光照,从而改变光刻胶性质;显影是对曝光后的光刻胶进行去除,由于光照后的光刻胶 和未被光照的光刻胶将分别溶于显影液和不溶于显影液,这样就使光刻胶上 形成了沟槽。 6、湿法腐蚀和等离子刻蚀 通过光刻显影后,光刻胶下面的材料要被选择性地去除,使用的方法就

【半导体研磨 精】半导体晶圆的生产工艺流程介绍

?从大的方面来讲,晶圆生产包括晶棒制造和晶片制造两大步骤,它又可细分为以下几道主要工序(其中晶棒制造只包括下面的第一道工序,其余的全部属晶片制造,所以有时又统称它们为晶柱切片后处理工序): 晶棒成长--> 晶棒裁切与检测--> 外径研磨--> 切片--> 圆边--> 表层研磨--> 蚀刻--> 去疵--> 抛光--> 清洗--> 检验--> 包装 1 晶棒成长工序:它又可细分为: 1)融化(Melt Down) 将块状的高纯度复晶硅置于石英坩锅内,加热到其熔点1420°C以上,使其完全融化。 2)颈部成长(Neck Growth) 待硅融浆的温度稳定之后,将〈1.0.0〉方向的晶种慢慢插入其中,接着将晶种慢慢往上提升,使其直径缩小到一定尺寸(一般约6mm左右),维持此直径并拉长 100-200mm,以消除晶种内的晶粒排列取向差异。 3)晶冠成长(Crown Growth) 颈部成长完成后,慢慢降低提升速度和温度,使颈部直径逐渐加大到所需尺寸(如 5、6、8、12吋等)。 4)晶体成长(Body Growth) 不断调整提升速度和融炼温度,维持固定的晶棒直径,只到晶棒长度达到预定值。 5)尾部成长(Tail Growth) 1

当晶棒长度达到预定值后再逐渐加快提升速度并提高融炼温度,使晶棒直径逐渐变小,以避免因热应力造成排差和滑移等现象产生,最终使晶棒与液面完全分离。到此即得到一根完整的晶棒。 2 晶棒裁切与检测(Cutting & Inspection) 将长成的晶棒去掉直径偏小的头、尾部分,并对尺寸进行检测,以决定下步加工的工艺参数。 3 外径研磨(Su rf ace Grinding & Shaping) 由于在晶棒成长过程中,其外径尺寸和圆度均有一定偏差,其外园柱面也凹凸不平,所以必须对外径进行修整、研磨,使其尺寸、形状误差均小于允许偏差。 4 切片(Wire Saw Sl ic ing) 由于硅的硬度非常大,所以在本工序里,采用环状、其内径边缘镶嵌有钻石颗粒的薄片锯片将晶棒切割成一片片薄片。 5 圆边(Edge Profiling) 由于刚切下来的晶片外边缘很锋利,硅单晶又是脆性材料,为避免边角崩裂影响晶片强度、破坏晶片表面光洁和对后工序带来污染颗粒,必须用专用的电脑控制设备自动修整晶片边缘形状和外径尺寸。 ? 6 研磨(Lapping) 研磨的目的在于去掉切割时在晶片表面产生的锯痕和破损,使晶片表面达到所要求的光洁度。 7 蚀刻(Etching) 1

_半导体_大规模集成电路工艺流程_张琦汇总

引言 随着半导体器件封装的小型化、片状化、薄型化和焊球阵列化,对半导体封装技术要求越来越高。由于封装材料复杂性的不断增加,半导体封装技术也越来越复杂,封装和工艺流程也越来越复杂。 1.(半导体大规模集成电路封装工艺简介 所谓封装就是指安装半导体集成电路芯片用的外壳,通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件连接,它起着安装、固定、密封,保护芯片及增强电热性能等方面的作用。 1.1 以焊接技术为基础的互连工艺以焊接技术为基础的互连工艺普遍采用叠层型三维封装结构,即把多个裸芯片 (半导体大规模集成电路工艺流程 张琦1 韩团军2 1.陕西理工学院机械工程学院; 2.陕西理工学院电信系 或多芯片模块(MCM沿Z 轴层层叠装、互连,组成三维封装结构。叠层型三维封装的优点是工艺相对简单,成本相对较低,关键是解决各层间的垂直互连问题。根

据集成功率模块的特殊性,主要利用焊接工艺将焊料凸点、金属柱等焊接在芯片的电极引出端,并与任一基板或芯片互连。目前的技术方案包括焊料凸点互连(Solder Ball Interconnect和金属柱互连平行板结构(Metal Posts Interconnected Parallel Plate Structures--MPIPPS等。 1.2以沉积金属膜为基础的互连工艺多采用埋置型三维封装结构,即在各类基板或介质中埋置裸芯片,顶层再贴装表贴元件及芯片来实现三维封装结构。其特点是蒸镀或溅射的金属膜不仅与芯片的电极相连,而且可以构成电路图形,并连至其他电路。其最大优点是能大大减少焊点,缩短引线间距,进而减小寄生参数。另外,这种互连工艺采用的埋置型三维封装结构能够增大芯片的有效散热面积,热量耗散可以沿模块的各个方向流动,有利于进一步提高集成模块的功率密度,以沉积金属膜为基础的互连工艺有薄膜覆盖技术和嵌入式封装等。 2.(半导体大规模集成电路封装工艺流程 2.1 (半导体大规模集成电路封装前道工程 TAPE MOUNT →SAWING →DIE ATTACH →WIRE BOND T A P E M O U N T 工程是半导体ASSEMBLY 工程中的第一道工序,其目的在于将要加工的WAFER 固定,便于自动化加工。过程实质是用T AP E 从背面将WAFER 固定在RING 上。 现在所用的TAPE 成卷筒状,一面有黏性,通常使用的TAPE 为蓝色,具有弹性,呈半透明状。通常使用的TAPE 缺点 是随时间的增加黏性逐渐增大,一般在2~3天内加工完毕对产品没有影响。TAPE MOUNT 完成后要求在TAPE 与WAFER 间粘贴平整,如果背面存在气泡,在SAWING 时切割好的DIE 会脱离TAPE 翘起,将切割好的BLADE 损坏,同时也损坏了DIE 。因此T/M 后应检查背面的粘合情况,如有少数气泡,可用指甲背面轻轻将气泡压平,若压不平,可用刀片将TAPE 划破一点,放出气泡中的空气,然后压平。气泡面积不能大于DIE 面积的1/4。

半导体的生产工艺流程

半导体的生产工艺流程 微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术 (silicon-basedmicromachining),原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程,以免沦于夏虫语冰的窘态。 一、洁净室 一般的机械加工是不需要洁净室(cleanroom)的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果。为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。洁净室的洁净等级,有一公认的标准,以class10为例,意谓在单位立方英呎的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。所以class后头数字越小,洁净度越佳,当然其造价也越昂贵。为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下: 1、内部要保持大于一大气压的环境,以确保粉尘只出不进。所以需要大型 鼓风机,将经滤网的空气源源不绝地打入洁净室中。 2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统 中。换言之,鼓风机加压多久,冷气空调也开多久。 3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆 放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。 4、所有建材均以不易产生静电吸附的材质为主。 5、所有人事物进出,都必须经过空气吹浴(airshower)的程序,将表面粉尘 先行去除。 6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人 员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触(在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。)当然,化妆是在禁绝之内,铅笔等也禁止使用。 7、除了空气外,水的使用也只能限用去离子水(DIwater,de-ionizedwater)。 一则防止水中粉粒污染晶圆,二则防止水中重金属离子,如钾、钠离子污染金氧半(MOS)晶体管结构之带电载子信道(carrierchannel),影响半导体组件的工作特性。去离子水以电阻率(resistivity)来定义好坏,一般要求至 17.5MΩ-cm以上才算合格;为此需动用多重离子交换树脂、RO逆渗透、与 UV紫外线杀菌等重重关卡,才能放行使用。由于去离子水是最佳的溶剂与清洁剂,其在半导体工业之使用量极为惊人! 8、洁净室所有用得到的气源,包括吹干晶圆及机台空压所需要的,都得使 用氮气(98%),吹干晶圆的氮气甚至要求99.8%以上的高纯氮!以上八点说明是最基本的要求,另还有污水处理、废气排放的环保问题,再再需要大笔

半导体制造工艺流程

半导体制造工艺流程 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(FrontEnd)制程 晶圆处理制程(WaferFabrication;简称WaferFab)、 晶圆针测制程(WaferProbe); 後段(BackEnd) 构装(Packaging)、 测试制程(InitialTestandFinalTest) 一、晶圆处理制程 晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随著产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接著进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 二、晶圆针测制程 经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒 三、IC构装制程 IC構裝製程(Packaging):利用塑膠或陶瓷包裝晶粒與配線以成積體電路目的:是為了製造出所生產的電路的保護層,避免電路受到機械性刮傷或是高溫破壞。 半导体制造工艺分类 半导体制造工艺分类 一双极型IC的基本制造工艺: A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离)ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离 I2L(饱和型) 半导体制造工艺分类 二MOSIC的基本制造工艺: 根据栅工艺分类 A铝栅工艺 B硅栅工艺

晶圆封装测试工序和半导体制造工艺流程0001

盛年不重来,一日难再晨。及时宜自勉,岁月不待人 盛年不重来,一日难再晨。及时宜自勉,岁月不待人 A.晶圆封装测试工序 一、IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electro n Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dime nsioi n Measureme nt) 对蚀刻后的图案作精确的尺寸检测。 二、IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic )及塑胶(plastic )两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割( die saw)、黏晶(die mount / die bond)、焊线(wire bon d)、圭寸胶(mold )、剪切/ 成形(trim / form )、印字(mark )、电镀(plating )及检验(inspection )等。 (1) 晶片切割(die saw ) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die )切割分离。举例来说:以 0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之 晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mou nt / die bo nd ) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线 架则经由传输设备送至弹匣( magazi ne )内,以送至下一制程进行焊线。 ⑶焊线(wire bond ) IC构装制程(Packaging )则是利用塑胶或陶瓷包装晶粒与配线以成集成电路( Integrated Circuit ;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械

半导体工艺流程

1、清洗 集成电路芯片生产的清洗包括硅片的清洗和工器具的清洗。由于半导体生产污染要求非常严格,清洗工艺需要消耗大量的高纯水;且为进行特殊过滤和纯化广泛使用化学试剂和有机溶剂。 在硅片的加工工艺中,硅片先按各自的要求放入各种药液槽进行表面化学处理,再送入清洗槽,将其表面粘附的药液清洗干净后进入下一道工序。常用的清洗方式是将硅片沉浸在液体槽内或使用液体喷雾清洗,同时为有更好的清洗效果,通常使用超声波激励和擦片措施,一般在有机溶剂清洗后立即采用无机酸将其氧化去除,最后用超纯水进行清洗,如图1 —6所示。 图1—6硅片清洗工艺示意图 工具的清洗基本米用硅片清洗同样的方法。 2、热氧化 热氧化是在800~1250C高温的氧气氛围和惰性携带气体(N2)下使硅片表面的硅氧化生成二氧化硅膜的过程,产生的二氧化硅用以作 为扩散、离子注入的阻挡层,或介质隔离层。典型的热氧化化学反应为:

Si + O2f SiO2 3、扩散 扩散是在硅表面掺入纯杂质原子的过程。通常是使用乙硼烷(B2H6)作为N —源和磷烷(PH3)作为P+源。工艺生产过程中通常 分为沉积源和驱赶两步,典型的化学反应为: 2PH3 f 2P + 3H2 4、离子注入 离子注入也是一种给硅片掺杂的过程。它的基本原理是把掺杂物质(原子)离子化后,在数千到数百万伏特电压的电场下得到加速,以较高的能量注入到硅片表面或其它薄膜中。经高温退火后,注入离子活化,起施主或受主的作用。 5、光刻 光刻包括涂胶、曝光、显影等过程。涂胶是通过硅片高速旋转在硅片表面均匀涂上光刻胶的过程;曝光是使用光刻机,并透过光掩膜版对涂胶的硅片进行光照,使部分光刻胶得到光照,另外,部分光刻胶得不到光照,从而改变光刻胶性质;显影是对曝光后的光刻胶进行去除,由于光照后的光刻胶和未被光照的光刻胶将分别溶于显影液和不溶于显影液,这样就使光刻胶上 形成了沟槽。 光刻胶 基片------------ ?涂胶后基片 1 1 1 1 ~ 显影后基片V------------- 曝光后基片 6、湿法腐蚀和等离子刻蚀

半导体工艺流程

集成电路芯片生产的清洗包括硅片的清洗和工器具的清洗。由于半导体生产污染要求非常严格,清洗工艺需要消耗大量的高纯水;且为进行特殊过滤和纯化广泛使用化学试剂和有机溶剂。 在硅片的加工工艺中,硅片先按各自的要求放入各种药液槽进行表面化学处理,再送入清洗槽,将其表面粘附的药液清洗干净后进入下一道工序。常用的清洗方式是将硅片沉浸在液体槽内或使用液体喷雾清洗,同时为有更好的清洗效果,通常使用超声波激励和擦片措施,一般在有机溶剂清洗后立即采用无机酸将其氧化去除,最后用超纯水进行清洗,如图1-6所示。 图1-6硅片清洗工艺示意图 工具的清洗基本采用硅片清洗同样的方法。 2、热氧化 热氧化是在800~1250℃高温的氧气氛围和惰性携带气体(N2)下使硅片表面的硅氧化生成二氧化硅膜的过程,产生的二氧化硅用以作为扩散、离子注入的阻挡层,或介质隔离层。典型的热氧化化学反应为: Si + O2→SiO2

扩散是在硅表面掺入纯杂质原子的过程。通常是使用乙硼烷(B 2H 6)作为N -源和磷烷(PH 3)作为P +源。工艺生产过程中通常分为沉积源和驱赶两步,典型的化学反应为: 2PH 3 → 2P + 3H 2 4、离子注入 离子注入也是一种给硅片掺杂的过程。它的基本原理是把掺杂物质(原子)离子化后,在数千到数百万伏特电压的电场下得到加速,以较高的能量注入到硅片表面或其它薄膜中。经高温退火后,注入离子活化,起施主或受主的作用。 5、光刻 光刻包括涂胶、曝光、显影等过程。涂胶是通过硅片高速旋转在硅片表面均匀涂上光刻胶的过程;曝光是使用光刻机,并透过光掩膜版对涂胶的硅片进行光照,使部分光刻胶得到光照,另外,部分光刻胶得不到光照,从而改变光刻胶性质;显影是对曝光后的光刻胶进行去除,由于光照后的光刻胶和未被光照的光刻胶将分别溶于显影液和不溶于显影液,这样就使光刻胶上形成了沟槽。 6、湿法腐蚀和等离子刻蚀 通过光刻显影后,光刻胶下面的材料要被选择性地去除,使用的基片 涂胶后基片 光刻胶 阻挡层

半导体的生产工艺流程(精)

半导体的生产工艺流程 微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon- based micromachining,原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程,以免沦于夏虫语冰的窘态。 一、洁净室 一般的机械加工是不需要洁净室(clean room的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果。 为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。洁净室的洁净等级,有一公认的标准,以class 10为例,意谓在单位立方英呎的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。所以class后头数字越小,洁净度越佳,当然其造价也越昂贵(参见图2-1。 为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下: 1、内部要保持大于一大气压的环境,以确保粉尘只出不进。所以需要大型鼓风机,将经滤网的空气源源不绝地打入洁净室中。 2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统中。换言之,鼓风机加压多久,冷气空调也开多久。 3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。 4、所有建材均以不易产生静电吸附的材质为主。 5、所有人事物进出,都必须经过空气吹浴 (air shower 的程序,将表面粉尘先行去除。

6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触 (在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。当然,化妆是在禁绝之内,铅笔等也禁止使用。 7、除了空气外,水的使用也只能限用去离子水 (DI water, de-ionized water。一则防止水中粉粒污染晶圆,二则防止水中重金属离子,如钾、钠离子污染金氧半(MOS 晶体管结构之带电载子信道 (carrier channel,影响半导体组件的工作特性。去离子水以电阻 率 (resistivity 来定义好坏,一般要求至17.5MΩ-cm以上才算合格;为此需动用多重离子交换树脂、RO逆渗透、与UV紫外线杀菌等重重关卡,才能放行使用。由于去离子水是最佳的溶剂与清洁剂,其在半导体工业之使用量极为惊人! 8、洁净室所有用得到的气源,包括吹干晶圆及机台空压所需要的,都得使用氮气(98%,吹干晶圆的氮气甚至要求99.8%以上的高纯氮!以上八点说明是最基本的要求,另还有污水处理、废气排放的环保问题,再再需要大笔大笔的建造与维护费用! 二、晶圆制作 硅晶圆 (silicon wafer 是一切集成电路芯片的制作母材。既然说到晶体,显然是经过纯炼与结晶的程序。目前晶体化的制程,大多是采「柴可拉斯基」(Czycrasky 拉晶法 (CZ法。拉晶时,将特定晶向 (orientation 的晶种 (seed,浸入过饱和的纯硅熔汤 (Melt 中,并同时旋转拉出,硅原子便依照晶种晶向,乖乖地一层层成长上去,而得出所谓的晶棒 (ingot。晶棒的阻值如果太低,代表其中导电杂质 (impurity dopant 太多,还需经过FZ 法 (floating-zone 的再结晶 (re-crystallization,将杂质逐出,提高纯度与阻值。 辅拉出的晶棒,外缘像椰子树干般,外径不甚一致,需予以机械加工修边,然后以X 光绕射法,定出主切面 (primary flat 的所在,磨出该平面;再以内刃环锯,削下一片片的硅晶圆。最后经过粗磨 (lapping、化学蚀平 (chemical etching 与拋光 (polishing 等程序,得出具表面粗糙度在0.3微米以下拋光面之晶圆。(至于晶圆厚度,与其外径有

(工艺流程)2020年半导体硅片生产工艺流程及工艺注意要点

硅片生产工艺流程及注意要点 简介 硅片的准备过程从硅单晶棒开始,到清洁的抛光片结束,以能够在绝好的环境中使用。期间,从一单晶硅棒到加工成数片能满足特殊要求的硅片要经过很多流程和清洗步骤。除了有许多工艺步骤之外,整个过程几乎都要在无尘的环境中进行。硅片的加工从一相对较脏的环境开始,最终在10级净空房内完成。 工艺过程综述 硅片加工过程包括许多步骤。所有的步骤概括为三个主要种类:能修正物理性能如尺寸、形状、平整度、或一些体材料的性能;能减少不期望的表面损伤的数量;或能消除表面沾污和颗粒。硅片加工的主要的步骤如表1.1的典型流程所示。工艺步骤的顺序是很重要的,因为这些步骤的决定能使硅片受到尽可能少的损伤并且可以减少硅片的沾污。在以下的章节中,每一步骤都会得到详细介绍。 表1.1 硅片加工过程步骤 1.切片 2.激光标识 3.倒角 4.磨片 5.腐蚀 6.背损伤 7.边缘镜面抛光 8.预热清洗 9.抵抗稳定——退火 10.背封 11.粘片 12.抛光 13.检查前清洗 14.外观检查

15.金属清洗 16.擦片 17.激光检查 18.包装/货运 切片(class 500k) 硅片加工的介绍中,从单晶硅棒开始的第一个步骤就是切片。这一步骤的关键是如何在将单晶硅棒加工成硅片时尽可能地降低损耗,也就是要求将单晶棒尽可能多地加工成有用的硅片。为了尽量得到最好的硅片,硅片要求有最小量的翘曲和最少量的刀缝损耗。切片过程定义了平整度可以基本上适合器件的制备。 切片过程中有两种主要方式——内圆切割和线切割。这两种形式的切割方式被应用的原因是它们能将材料损失减少到最小,对硅片的损伤也最小,并且允许硅片的翘曲也是最小。 切片是一个相对较脏的过程,可以描述为一个研磨的过程,这一过程会产生大量的颗粒和大量的很浅表面损伤。 硅片切割完成后,所粘的碳板和用来粘碳板的粘结剂必须从硅片上清除。在这清除和清洗过程中,很重要的一点就是保持硅片的顺序,因为这时它们还没有被标识区分。 激光标识(Class 500k) 在晶棒被切割成一片片硅片之后,硅片会被用激光刻上标识。一台高功率的激光打印机用来在硅片表面刻上标识。硅片按从晶棒切割下的相同顺序进行编码,因而能知道硅片的正确位置。这一编码应是统一的,用来识别硅片并知道它的来源。编码能表明该硅片从哪一单晶棒的什么位置切割下来的。保持这样的追溯是很重要的,因为单晶的整体特性会随着晶棒的一头到另一头而变化。编号需刻的足够深,从而到最终硅片抛光完毕后仍能保持。在硅片上刻下编码后,即使硅片有遗漏,也能追溯到原来位置,而且如果趋向明了,那么就可以采取正确的措施。激光标识可以在硅片的正面也可在背面,尽管正面通常会被用到。

半导体制造工艺流程简介

半导体制造工艺流程简介 半导体制造工艺 1 NPN高频小功率晶体管制造的工艺流程为: 外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。 PNP小功率晶体管制造的工艺流程为: 外延片——编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻——QC检查——前处理——基区CSD涂覆——CSD预淀积——后处理——QC 检查(R?)——前处理——基区氧化扩散——QC检查(tox、R?)——二次光刻——QC 检查——单结测试——前处理——POCl3预淀积——后处理(P液)——QC检查——前处理——发射区氧化——QC检查(tox)——前处理——发射区再扩散(R?)——前处理——铝下CVD——QC检查(tox、R?)——前处理——HCl氧化——前处理——氢气处 理——三次光刻——QC检查——追扩散——双结测试——前处理——铝蒸发——QC检查(tAl)——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——QC检查(ts)——五次光刻——QC检查——大片测试——中测——中测检查(——

半导体产业简述

半导体产业概况 一、半导体产业分析 集成电路产业是现代电子信息产业的基础和核心。随着全球信息化、网络化和知识经济的迅速发展,集成电路产业在国民经济中的地位越来越重要,它以其无穷的变革、创新和极强的渗透力,推动着信息产业的快速发展。每1-2 元集成电路产值能带动10 元左右电子信息产业产值,进而带动100 元左右的GDP 增长。 (一)2011年世界半导体产业发展情况 2011年世界半导体产业继2010年四季度高涨发展的势头,继续向前惯性前进,总的处于平稳增长的态势。但与同期相比,仍有明显的下滑痕迹:一是往年一季度是传统的淡季,在受日本大地震后,越加显得清淡了一些。二是在旺季的二季度,由于受到日本大地震影响,一些产品供应受阻,如BT树脂龙头三菱暂停供货,IC基板景硕二季度缺货,硅晶圆的原材料短缺,打乱供应链。三是日本的半导体大厂尔必达、瑞萨、东芝等公司到台湾晶圆代工厂寻找支援,另有德仪和飞思卡尔也向台积电和联电寻求协助。四是2011年增速落底,二季度实际营运变数多,有些在二季度库存水位进一步降低,带动第三季度业绩明显回升。 (二)2011年世界半导体产业投资情况 因2010年世界半导体产业颇丰,在2011年大部分大型芯片制造商纷纷增加资金投入提振: ●韩国海力士公司在无锡的四期工程投资20亿美元,使12英寸生产线技术从44nm提升至30nm,并全力提升至20nm级,与韩国本土的企业水平相当;●韩国海力士计划投资5.7亿美元,扩大和提升现有工厂研发; ●应用材料计划投资93亿美元,比2010年增加79%; ●应用材料以49亿美元,并购Varian公司; ●中国台湾日月光计划投资9亿美元,解决铜制程客户数和订单暴增; ●中国台湾台积电2011年开始生产12英寸28nm晶圆,月均投产5000片; ●中国台湾台积电计划投资100亿美元,开发450mm晶圆,实施20nm技术; ●中国台湾联电公司以0.87亿美元,收购苏州和舰30%的股权;

半导体制造工艺流程

半导体制造工艺流程集团文件发布号:(9816-UATWW-MWUB-WUNN-INNUL-DQQTY-

半导体制造工艺流程 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(FrontEnd)制程 晶圆处理制程(WaferFabrication;简称WaferFab)、 晶圆针测制程(WaferProbe); 後段(BackEnd) 构装(Packaging)、 测试制程(InitialTestandFinalTest) 一、晶圆处理制程 晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随着产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接着进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 二、晶圆针测制程

经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒 三、IC构装制程 IC构装制程(Packaging):利用塑胶或陶瓷包装晶粒与配线以成积体电路 目的:是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。 半导体制造工艺分类 半导体制造工艺分类 一双极型IC的基本制造工艺: A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离) ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离 I2L(饱和型) 半导体制造工艺分类 二MOSIC的基本制造工艺:

半导体集成电路工艺流程

集成电路制造工艺流程 晶体的生长 晶体切片成wafer 晶圆制作 功能设计à模块设计à电路设计à版图设计à制作光罩 工艺流程 1) 表面清洗 晶圆表面附着一层大约 2um 的 Al2O3 和甘油混合液保护之 , 在制作前必须进行化学刻蚀和表面清洗。 2) 初次氧化 有热氧化法生成 SiO2 缓冲层,用来减小后续中 Si3N4 对晶圆的应力 氧化技术 干法氧化Si( 固 ) + O2 = SiO2( 固 ) 湿法氧化Si( 固 ) +2H2O =SiO2( 固 ) + 2H2 干法氧化通常用来形成,栅极二氧化硅膜,要求薄,界面能级和固定电荷密度低的薄膜。干法氧化成膜速度慢于湿法。湿法氧化通常用来形成作为器件隔离用的比较厚的二氧化硅膜。当 SiO2 膜较薄时,膜厚与时间成正比。 SiO2 膜变厚时,膜厚与时间的平方根成正比。因而,要形成较厚的 SiO2 膜,需要较长的氧化时间。 SiO2 膜形成的速度取决于经扩散穿过 SiO2 膜到达硅表面的 O2 及 OH 基等氧化剂的数量的多少。湿法氧化时,因在于 OH 基在 SiO2 膜中的扩散系数比 O2 的大。氧化反应, Si 表面向深层移动,距离为 SiO2 膜厚的 0.44 倍。因此,不同厚度的 SiO2 膜,去除后的 Si 表面的深度也不同。 SiO2 膜为透明,通过光干涉来估计膜的厚度。这种干涉色的周期约为 200nm ,如果预告知道是几次干涉,就能正确估计。对其他的透明薄膜,如知道其折射率,也可用公式计算出 (d SiO2) / (d ox) = (n ox) / (n SiO2) 。 SiO2 膜很薄时,看不到干涉色,但可利用 Si 的疏水性和 SiO2 的亲水性来判断 SiO2 膜是否存在。也可用干涉膜计或椭圆仪等测出。 SiO2 和 Si 界面能级密度和固定电荷密度可由 MOS 二极管的电容特性求得。 (100) 面的 Si 的界面能级密度最低,约为 10E+10 -- 10E+11/cm – 2 .e V -1 数量级。 (100) 面时,氧化膜中固定电荷较多,固定电荷密度的大小成为左右阈值的主要因素。 3) CVD(Chemical Vapor deposition) 法沉积一层 Si3N4(Hot CVD 或 LPCVD) 。

半导体制造工艺流程

半导体制造工艺流程 半导体相关知识 本征材料:纯硅9-10个 250000Ω.cm3 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(Front End)制程 晶圆处理制程(Wafer Fabrication;简称Wafer Fab)、 晶圆针测制程(Wafer Probe); 后段(Back End) 构装(Packaging)、 测试制程(Initial Test and Final Test) 晶圆边缘检测系统 一、晶圆处理制程 晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件,为各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,有时可达数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随著产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之后,接著进行氧化(Oxidation)及沉积,最后进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 晶圆与晶片的区别 制造半导体前,必须将硅转换为晶圆片。这要从硅锭的生长开始。单晶硅是原子以三维空间模式周期形成的固体,这种模式贯穿整个材料。多晶硅是很多具有不同晶向的小单晶体单独形成的,不能用来做半导体电路。多晶硅必须融化成单晶体,才能加工成半导体应用中使用的晶圆片。晶片由晶圆切割成,直径和晶圆相同,厚度为300μm 由于硅很硬,要用金刚石锯来准确切割晶圆片,以得到比要求尺寸要厚一些的晶片。激光锯也有助于减少对晶圆片的损伤、厚度不均、弯曲以及翘曲缺陷。 切割晶圆片后,开始进入研磨工艺。研磨晶圆片以减少正面和背面的锯痕和表面损伤。同时打薄晶圆片并帮助释放切割过程中积累的硬力。研磨后,进入刻蚀和清洗工艺,使用氢氧化钠、乙酸和硝酸的混合物以减轻磨片过程中产生的损伤和裂纹。关键的倒角工艺是要将晶圆片的边缘磨圆,彻底消除将来电路制作过程中破损的可能性。倒角后,要按照最终用户的要求,经常需要对边缘进行抛光,提高整体清洁度以进一步减少破损。

晶圆封装测试工序和半导体制造工艺流程_百度文库(精)

晶圆封装测试工序和半导体制造工艺流程.txt-两个人同时犯了错,站出来承担的那一方叫宽容,另一方欠下的债,早晚都要还。-不爱就不爱,别他妈的说我们合不来。A.晶圆封装测试工序 一、 IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement 对蚀刻后的图案作精确的尺寸检测。 二、 IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。 (4 封胶(mold)

半导体制造工艺流程

半导体制造工艺流程 Document number:NOCG-YUNOO-BUYTT-UU986-1986UT

半导体制造工艺流程 半导体相关知识 本征材料:纯硅9-10个 250000Ω.cm3 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(FrontEnd)制程 晶圆处理制程(WaferFabrication;简称WaferFab)、 晶圆针测制程(WaferProbe); 后段(BackEnd) 构装(Packaging)、 测试制程(InitialTestandFinalTest) 晶圆边缘检测系统 一、晶圆处理制程 晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件,为各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,有时可达数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随着产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之后,接着进行氧化(Oxidation)及沉积,最后进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 晶圆与晶片的区别 制造半导体前,必须将硅转换为晶圆片。这要从硅锭的生长开始。单晶硅是原子以三维空间模式周期形成的固体,这种模式贯穿整个材料。多晶硅是很多具有不同晶向的小单晶体单独形成的,不能用来做半导体电路。多晶硅必须融化成单晶体,才能加工成半导体应用中使用的晶圆片。晶片由晶圆切割成,直径和晶圆相同,厚度为300μm 由于硅很硬,要用金刚石锯来准确切割晶圆片,以得到比要求尺寸要厚一些的晶片。激光锯也有助于减少对晶圆片的损伤、厚度不均、弯曲以及翘曲缺陷。 切割晶圆片后,开始进入研磨工艺。研磨晶圆片以减少正面和背面的锯痕和表面损伤。同时打薄晶圆片并帮助释放切割过程中积累的硬力。研磨后,进入刻蚀和清洗工艺,使用氢氧化钠、乙酸和硝酸的混合物以减轻磨片过程中产生的损伤和裂纹。关键的倒角工艺是要将晶圆片的边缘磨圆,彻底消除将来电路制作过程中破损的可能性。倒角后,要按照最终用户的要求,经常需要对边缘进行抛光,提高整体清洁度以进一步减少破损。

半导体制造工艺流程

半导体制造工艺流程 This model paper was revised by the Standardization Office on December 10, 2020

半导体制造工艺流程 半导体相关知识 本征材料:纯硅 9-10个 250000Ω.cm3 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入 III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(Front End)制程 晶圆处理制程(Wafer Fabrication;简称 Wafer Fab)、晶圆针测制程(Wafer Probe); 后段(Back End) 构装(Packaging)、 测试制程(Initial Test and Final Test) 晶圆边缘检测系统 一、晶圆处理制程

晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件,为各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,有时可达数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随着产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之后,接着进行氧化(Oxidation)及沉积,最后进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 晶圆与晶片的区别 制造半导体前,必须将硅转换为晶圆片。这要从硅锭的生长开始。单晶硅是原子以三维空间模式周期形成的固体,这种模式贯穿整个材料。多晶硅是很多具有不同晶向的小单晶体单独形成的,不能用来做半导体电路。多晶硅必须融化成单晶体,才能加工成半导体应用中使用的晶圆片。晶片由晶圆切割成,直径和晶圆相同,厚度为300μm 由于硅很硬,要用金刚石锯来准确切割晶圆片,以得到比要求尺寸要厚一些的晶片。激光锯也有助于减少对晶圆片的损伤、厚度不均、弯曲以及翘曲缺陷。 切割晶圆片后,开始进入研磨工艺。研磨晶圆片以减少正面和背面的锯痕和表面损伤。同时打薄晶圆片并帮助释放切割过程中积累的硬力。研磨后,进入刻蚀和清洗工艺,使用氢氧化钠、乙酸和硝酸的混合物以减轻磨片过程中产生的损伤和裂纹。关键的倒角工艺是要将晶圆片的边缘磨圆,彻底消除将来电路制作过程中破损的可能性。倒角后,要按照最终用户的要求,经常需要对边缘进行抛光,提高整体清洁度以进一步减少破损。