82C51A微处理器

E2O0017-27-X2

MSM82C51A-2RS/GS/JS

UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER GENERAL DESCRIPTION

The MSM82C51A-2 is a USART (Universal Synchronous Asynchronous Receiver Transmitter) for serial data communication.

As a peripheral device of a microcomputer system, the MSM82C51A-2 receives parallel data from the CPU and transmits serial data after conversion. This device also receives serial data from the outside and transmits parallel data to the CPU after conversion.

The MSM82C51A-2 configures a fully static circuit using silicon gate CMOS technology. Therefore, it operates on extremely low power at 100 m A (max) of standby current by suspending all operations.

FEATURES

?Wide power supply voltage range from 3 V to 6 V

?Wide temperature range from –40°C to 85°C

?Synchronous communication upto 64 Kbaud

?Asynchronous communication upto 38.4 Kbaud

?Transmitting/receiving operations under double buffered configuration.

?Error detection (parity, overrun and framing)

?28-pin Plastic DIP (DIP28-P-600-2.54): (Product name: MSM82C51A-2RS)

?28-pin Plastic QFJ (QFJ28-P-S450-1.27): (Product name: MSM82C51A-2JS)

?32-pin Plastic SSOP(SSOP32-P-430-1.00-K): (Product name: MSM82C51A-2GS-K)

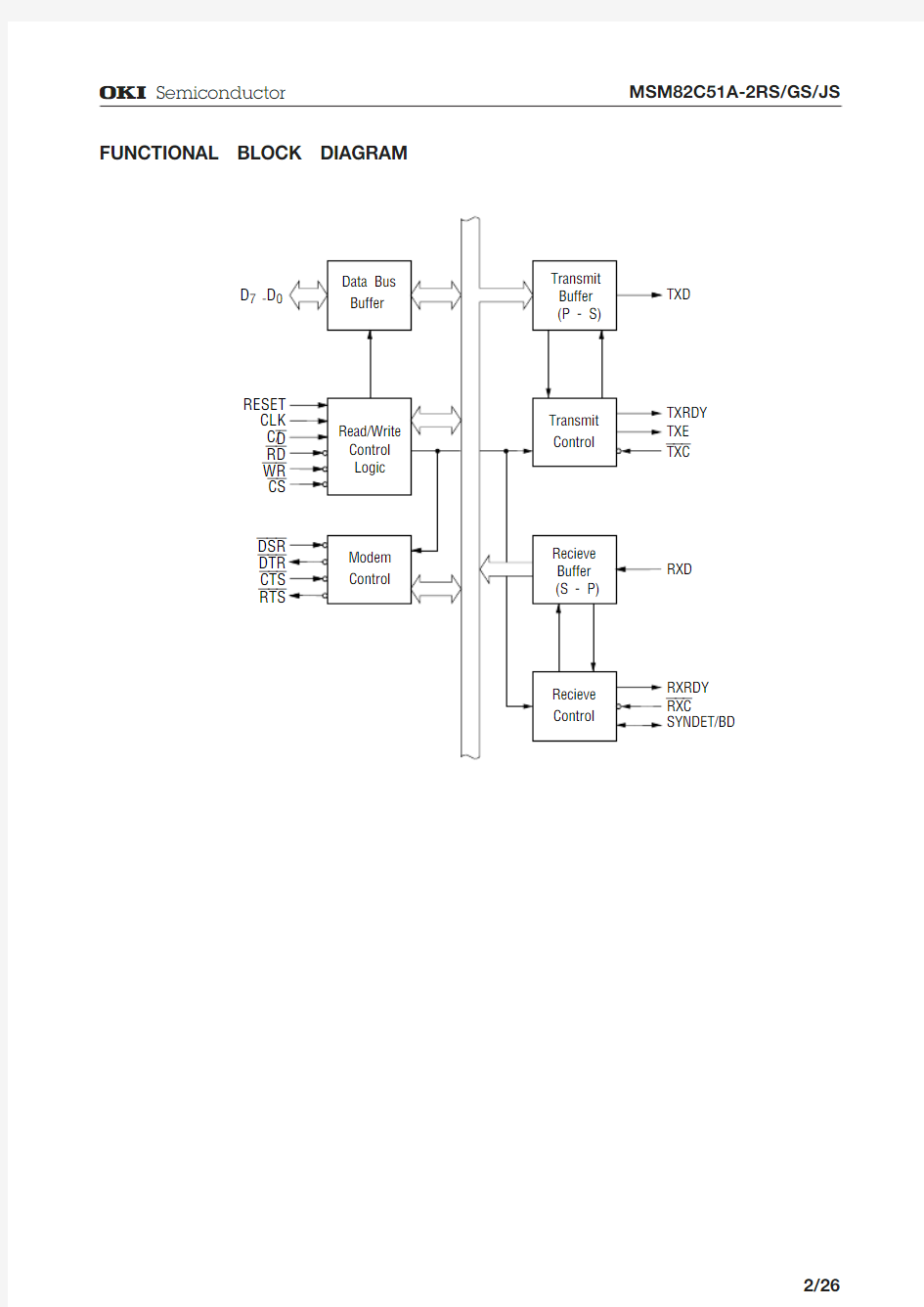

FUNCTIONAL BLOCK DIAGRAM

TXD

D 7 - D 0

C/TXRDY TXE TXC

RXD

RXRDY RXC

SYNDET/BD

PIN CONFIGURATION (TOP VIEW)

28 pin Plastic DIP

D 1D 0V CC RXC NC DTR RTS DSR RESET CLK TXD TXEMPTY NC CTS SYNDET/BD TXRDY

D 4D 5D 6D 7TXC

WR CS

FUNCTION

Outline

The MSM82C51A-2's functional configuration is programed by software.

Operation between the MSM82C51A-2 and a CPU is executed by program control. Table 1shows the operation between a CPU and the device.

000Data Bus 3-State 1Data Bus 3-State CS ¥11¥C/D Status ? CPU Control Word ¨ CPU 110¥0

Data ¨ CPU

0Data ? CPU 0

00

1WR 10

1¥1

0RD Table 1 Operation between MSM82C51A and CPU It is necessary to execute a function-setting sequence after resetting the MSM82C51A-2. Fig. 1shows the function-setting sequence.

If the function was set, the device is ready to receive a command, thus enabling the transfer of data by setting a necessary command, reading a status and reading/writing data.

Fig. 1 Function-setting Sequence (Mode Instruction Sequence)

Control Words

There are two types of control word.

1. Mode instruction (setting of function)

2. Command (setting of operation)

1)Mode Instruction

Mode instruction is used for setting the function of the MSM82C51A-2. Mode instruction will be in “wait for write” at either internal reset or external reset. That is, the writing of a control word after resetting will be recognized as a “mode instruction.”

Items set by mode instruction are as follows:

?Synchronous/asynchronous mode

?Stop bit length (asynchronous mode)

?Character length

?Parity bit

?Baud rate factor (asynchronous mode)

?Internal/external synchronization (synchronous mode)

?Number of synchronous characters (Synchronous mode)

The bit configuration of mode instruction is shown in Figures 2 and 3. In the case of synchronous mode, it is necessary to write one-or two byte sync characters.

If sync characters were written, a function will be set because the writing of sync characters constitutes part of mode instruction.

Fig. 2 Bit Configuration of Mode Instruction (Asynchronous)

Fig. 3 Bit Configuration of Mode Instruction (Synchronous)

2)Command

Command is used for setting the operation of the MSM82C51A-2.

It is possible to write a command whenever necessary after writing a mode instruction and sync characters.

Items to be set by command are as follows:

?Transmit Enable/Disable

?Receive Enable/Disable

?DTR, RTS Output of data.

?Resetting of error flag.

?Sending to break characters

?Internal resetting

?Hunt mode (synchronous mode)

The bit configuration of a command is shown in Fig. 4.

Note: Seach mode for synchronous

charactors in synchronous mode.

Fig. 4 Bit Configuration of Command

Status Word

It is possible to see the internal status of MSM82C51A-2 by reading a status word.

The bit configuration of status word is shown in Fig. 5.

Fig. 5 Bit Configuration of Status Word

Standby Status

It is possible to put the MSM82C51A-2 in “standby status”

When the following conditions have been satisfied the MSM82C51A-2 is in “standby status.”

(1)CS terminal is fixed at Vcc level.

(2)Input pins other CS , D0 to D7, RD, WR and C/D are fixed at Vcc or GND level (including

SYNDET in external synchronous mode).

Note:When all output currents are 0, ICCS specification is applied.

Pin Description

D0 to D7 (l/O terminal)

This is bidirectional data bus which receive control words and transmits data from the CPU and sends status words and received data to CPU.

RESET (Input terminal)

A “High” on this input forces the MSM82C51A-2 into “reset status.”

The device waits for the writing of “mode instruction.”

The min. reset width is six clock inputs during the operating status of CLK.

CLK (Input terminal)

CLK signal is used to generate internal device timing.

CLK signal is independent of RXC or TXC.

However, the frequency of CLK must be greater than 30 times the RXC and TXC at Synchronous mode and Asynchronous “x1” mode, and must be greater than 5 times at Asynchronous “x16”and “x64” mode.

WR (Input terminal)

This is the “active low” input terminal which receives a signal for writing transmit data and control words from the CPU into the MSM82C51A-2.

RD (Input terminal)

This is the “active low” input terminal which receives a signal for reading receive data and status words from the MSM82C51A-2.

C/D (Input terminal)

This is an input terminal which receives a signal for selecting data or command words and status words when the MSM82C51A-2 is accessed by the CPU.

If C/D = low, data will be accessed.

If C/D = high, command word or status word will be accessed.

CS (Input terminal)

This is the “active low” input terminal which selects the MSM82C51A-2 at low level when the CPU accesses.

Note:The device won’t be in “standby status”; only setting CS = High.

Refer to “Explanation of Standby Status.”

TXD (output terminal)

This is an output terminal for transmitting data from which serial-converted data is sent out. The device is in “mark status” (high level) after resetting or during a status when transmit is disabled. It is also possible to set the device in “break status” (low level) by a command.

TXRDY (output terminal)

This is an output terminal which indicates that the MSM82C51A-2 is ready to accept a transmitted data character. But the terminal is always at low level if CTS = high or the device was set in “TX disable status” by a command.

Note:TXRDY status word indicates that transmit data character is receivable, regardless

of CTS or command.

If the CPU writes a data character, TXRDY will be reset by the leading edge or WR signal.

TXEMPTY (Output terminal)

This is an output terminal which indicates that the MSM82C51A-2 has transmitted all the characters and had no data character.

In “synchronous mode,” the terminal is at high level, if transmit data characters are no longer remaining and sync characters are automatically transmitted. If the CPU writes a data character, TXEMPTY will be reset by the leading edge of WR signal.

Note :As the transmitter is disabled by setting CTS “High” or command, data written before disable will be sent out. Then TXD and TXEMPTY will be “High”.

Even if a data is written after disable, that data is not sent out and TXE will be “High”.After the transmitter is enabled, it sent out. (Refer to Timing Chart of Transmitter Control and Flag Timing)

TXC (Input terminal)

This is a clock input signal which determines the transfer speed of transmitted data.

In “synchronous mode,” the baud rate will be the same as the frequency of TXC.

In “asynchronous mode”, it is possible to select the baud rate factor by mode instruction.

It can be 1, 1/16 or 1/64 the TXC.

The falling edge of TXC sifts the serial data out of the MSM82C51A-2.

RXD (input terminal)

This is a terminal which receives serial data.

RXRDY (Output terminal)

This is a terminal which indicates that the MSM82C51A-2 contains a character that is ready to READ.

If the CPU reads a data character, RXRDY will be reset by the leading edge of RD signal. Unless the CPU reads a data character before the next one is received completely, the preceding data will be lost. In such a case, an overrun error flag status word will be set.

RXC (Input terminal)

This is a clock input signal which determines the transfer speed of received data.

In “synchronous mode,” the baud rate is the same as the frequency of RXC.

In “asynchronous mode,” it is possible to select the baud rate factor by mode instruction.

It can be 1, 1/16, 1/64 the RXC.

SYNDET/BD (Input or output terminal)

This is a terminal whose function changes according to mode.

In “internal synchronous mode.” this terminal is at high level, if sync characters are received and synchronized. If a status word is read, the terminal will be reset.

In “external synchronous mode, “this is an input terminal.

A “High” on this input forces the MSM82C51A-2 to start receiving data characters.

In “asynchronous mode,” this is an output terminal which generates “high level”output upon the detection of a “break” character if receiver data contains a “low-level” space between the stop bits of two continuous characters. The terminal will be reset, if RXD is at high level. After Reset is active, the terminal will be output at low level.

DSR (Input terminal)

This is an input port for MODEM interface. The input status of the terminal can be recognized by the CPU reading status words.

DTR (Output terminal)

This is an output port for MODEM interface. It is possible to set the status of DTR by a command. CTS (Input terminal)

This is an input terminal for MODEM interface which is used for controlling a transmit circuit. The terminal controls data transmission if the device is set in “TX Enable” status by a command. Data is transmitable if the terminal is at low level.

RTS (Output terminal)

This is an output port for MODEM interface. It is possible to set the status RTS by a command.

ABSOLUTE MAXIMUM RATING

–55 to +150

MSM82C51A-2RS Power Supply Voltage V CC –0.5 to +7V Input Voltage V IN –0.5 to V CC +0.5V Output Voltage V OUT –0.5 to V CC +0.5V Storage Temperature T STG °C

Power Dissipation

P D

0.7

W

Parameter Unit Symbol With respect to GND

—Ta = 25°C

Conditions Rating

MSM82C51A-2GS MSM82C51A-2JS

0.9

0.9

OPERATING RANGE

Range Power Supply Voltage V CC 3 - 6V Operating Temperature

T op

–40 to 85

°C

Parameter

Unit Symbol RECOMMENDED OPERATING CONDITIONS

DC CHARACTERISTICS

Typ.Max."L" Output Voltage V OL —0.45V "H" Output Voltage V OH ——V Parameter Unit Symbol Min.—3.7I OL = 2.5 mA I OH = –2.5 mA Measurement Conditions Input Leak Current I LI —10m A Output Leak Current I LO —10m A –10–100 £ V IN £ V CC 0 £ V OUT £ V CC

Operating Supply Current —5mA —Asynchronous X64 during Transmitting/Receiving

Standby Supply Current

—

100

m A

—

I CCO I CCS

All Input voltage shall be fixed at V CC or GND level.

(V CC = 4.5 to 5.5 V Ta = –40°C to +85°C)

Typ.Power Supply Voltage V CC 5V T op +25"L" Input Voltage V IL —"H" Input Voltage

V IH

—

Min.4.5–40–0.32.2

Max.5.5+85+0.8V CC +0.3

Parameter

Unit Symbol °C V V

Operating Temperature

AC CHARACTERISTICS

CPU Bus Interface Part

Max.Address Stable before RD t AR —ns Parameter

Unit Symbol Min.20Note 2Remarks Address Hold Time for RD t RA —ns RD Pulse Width t RR —ns 20130Note 2—Data Delay from RD t RD 100ns ——RD to Data Float

t DF 75ns 10—Recovery Time between RD t RVR —t CY Address Stable before WR t AW —ns 620Note 5Note 2Address Hold Time for WR t WA —ns 20Note 2WR Pulse Width t WW —ns 100—Data Set-up Time for WR t DW —ns Data Hold Time for WR t WD —ns 1000——Recovery Time between WR t RVW —t CY 6Note 4RESET Pulse Width

t RESW

—

t CY

6

—

(V CC = 4.5 to 5.5 V, Ta = –40 to 85°C)

Serial Interface Part

Notes: 1.AC characteristics are measured at 150 pF capacity load as an output load based on 0.8 V at low level and 2.2 V at high level for output and 1.5 V for input.

2.Addresses are CS and C/D.

3.f TX or f RX£ 1/(30 Tcy)1¥ Baud

f TX or f RX£ 1/(5 Tcy)16¥, 64¥ Baud

4.This recovery time is mode Initialization only. Recovery time between command writes for

Asynchronous Mode is 8 t CY and for Synchronous Mode is 18 t CY.

Write Data is allowed only when TXRDY = 1.

5.This recovery time is Status read only.

Read Data is allowed only when RXRDY = 1.

6.Status update can have a maximum delay of 28 clock periods from event affecting the status.

TIMING CHART

Sytem Clock Input

Receiver Clock and Data

Transmitter Clock and Data

TXC (1 ¥ MODE)TXC (16 ¥ MODE)

TXD

RXC (1 ¥ Mode)

RXC (16 ¥ Mode)

RXD

INT Sampling

Pulse

Read Control or Input Port Cycle (CPU ¨ USART)

Write Control or Output Port Cycle (CPU ? USART)

Read Data Cycle (CPU ¨ USART)

RD

DATA OUT (D. B.)

RXRDY

CS

C/D Write Data Cycle (CPU ? USART)

WR

DATA IN (D. B.)

TXRDY CS

C/D

DSR . CTS

DATA OUT

(D. B.)

RD C/D CS

DTR . RTS

DATA IN (D. B.)

WR

C/D CS

Transmitter Control and Flag Timing (ASYNC Mode)

S T A R T B I T

S T O P B I T

CTS TXEMPTY TXRDY (STATUS BIT)

TXRDY (PIN)C/D WR TXD

Note: The wave-form chart is based on the case of 7-bit data length + parity bit + 2 stop bit.

Transmitter Control and Flag Timing (SYNC Mode)

Receiver Control and Flag Timing (ASYNC Mode)

D a t a B i t S t a r t B i t S t o p B i t P a r i t y B i t

BREAK DETECT FRAMING ERROR

(Status Bit)OVERRUN ERROR

(Status Bit)

RXRDY

C/D WR RD RXDATA

Note: The wave-form chart is based on the case of 7 data bit length + parity bit + 2 stop bit.

CTS TXEMPTY TXRDY (StatusBit)TXRDY (Pin)

C/D WR TXD

Note: The wave-form chart is based on the case of 5 data bit length + parity bit and 2 synchronous charactors.

Receiver Control and Flag Timing (SYNC Mode)

SYNDET (Pin) (Note 1)SYNDET (SB)OVERRUN ERROR (SB)RXRDY (PIN)

C/D WR RD

RXD RXC

Set SYNDET

Set SYNDET (Status bit)

Note:1. Internal Synchronization is based on the case of 5 data bit length + parity bit and 2 synchronous charactor.

2. External Synchronization is based on the case of 5 data bit length + parity bit.

Note: 1.Half-bit processing for the start bit

When the MSM82C51A-2 is used in the asynchronous mode, some problems are caused in the processing for the start bit whose length is smaller than the 1-data bit length. (See Fig. 1.)

2.Parity flag after a break signal is received (See Fig. 2.)

When the MSM82C51A-2 is used in the asynchrous mode, a parity flag may be set when the next normal data is read after a break signal is received.

A parity flag is set when the rising edge of the break signal (end of the break signal)is changed between the final data bit and the parity bit, through a RXRDY signal may not be outputted.

If this occurs, the parity flag is left set when the next normal dats is received, and the received data seems to be a parity error.

Smaller than 7-Receiver Clock Length ¥16Start bit Length

Mode Operation

The short start bit is ignored. (Normal)Smaller than 31-Receiver Clock Length ¥648-Receiver Clock Length ¥16The short start bit is ignored. (Normal)

Data cannot be received correctly due to a malfunction.32-Receiver Clock Length ¥64Data cannot be received correctly due to a malfunction.9 to 16-Receiver Clock Length ¥16The bit is regarded as a start bit. (normal)33 to 64-Receiver Clock Length

¥64

The bit is regarded as a start bit. (normal)

Half-bit Processing Timing Chart for the Start bit (Fig. 1)

ST D 0D 1D 2D 3D 4D 5D 6D 7P SP

ST D 0D 1D 2D 3D 4D 5D 6D 7P SP

RXD RXRDY

ST

ST D 0D 1D 2D 3D 4D 5D 6D 7P SP

RXD

RXRDY

A RXRDY signal is outputted during data reception due to a malfunction.

ST

ST D 0D 1D 2D 3D 4D 5D 6D 7P SP

RXD

RXRDY

ST:SP:P:

D 0 - D 7:Start bit Stop bit Parity bit Data bits

ST

ST D 0D 1D 2D 3D 4D 5D 6D 7P SP RXD

RXRDY

Normal Operation The Start bit Is Shorter Than a 1/2 Data bit The Start bit Is a 1/2 Data bit (A problem of MSM82C51A-2)The Start bit Is Longer Than a 1/2 Data bit

Break Signal Reception Timing and Parity Flag (Fig. 2)

ST D 0

D 7P SP ST D 0

D 7P SP ST D 0D 1D 2D 3D 4D 5D 6D 7P BIT POS.

RXD RXRDY

≠

A parity flag is set, but, no RXRDYsignal is outputted.

SP

ST D 0

D 7P SP ST D 0

D 7P SP ST D 0D 1D 2D 3D 4D 5D 6D 7P BIT POS.

RXD RXRDY

≠

No parity flag is set. and no RXRDY signal is outputted.

ST D 0

D 7P SP ST D 0

D 7P SP ST D 0D 1D 2D 3D 4D 5D 6D 7P BIT POS.

RXD RXRDY

≠

A parity flag is set. and a RXRDY signal is outputted.

SP

Normal Operation Bug Timing Normal Operation SP

微处理器发展史

微处理器发展史 CPU发展史 CPU也称为微处理器,微处理器的历史可追溯到1971年,当时INTEL公司推出了世界上第一台微处理器4004。 它是用于计算器的4位微处理器,含有2300个晶体管。从此以后,INTEL便与微处理器结下了不解之缘。 下面以INTEL公司的80X86系列为例介绍一下微处理器的发展历程。 1978和1979年, INTEL公司先后推出了8086和8088芯片,它们都是16位微处理器, 内含29000个晶体管,时钟频率为4.77MHz,地址总线为20位, 可使用1MB内存。它们的内部数据总线都是16位,外部数据总线8088是8位,8086是16位。

1981年 8088芯片首次用于IBMPC机中,开创了全新的微机时代。最早的i8086/8088是采用双列直插(DIP)形式封装, 从i80286开始采用方形BGA扁平封装(焊接), 从i80386开始到Pentiumpro开始采用方形PGA(插脚),1982年, INTEL推出了80286芯片,该芯片含有13.4万个晶体管,时钟频率由最初的6MHz逐步提高到20MHz。 其内部和外部数据总线皆为16位,地址总线24位,可寻址16MB内存。80286有两种工作方式:实模式 和保护模式。 1985年 INTEL推出了80386芯片,它是80X86系列中的第一种32位微处理器,内含27.5万个晶体管, 时钟频率为12.5MHz,后提高到20MHz,25MHz,33MHz。

其内部和外部数据总线都是32位,地址总线也是32位,可寻址4GB内存。 它除具有实模式和保护模式外,还增加了一种叫虚拟86的工作方式,可以通过同时模拟多个8086 处理器来提供多任务能力。 除了标准的80386芯片(称为80386DX)外,出于不同的市场和应用考虑,INTEL又陆续推出了一些 其它类型的80386芯片: 80386SX、80386SL、80386DL等。 1988年 推出的80386SX是市场定位在80286和80386DX之间的一种芯片,其与80386DX的不同在于 外部数据总线和地址总线皆与80286相同,分别是16位和24位(即寻址能力为16MB)。 1990年 推出的80386SL和80386DL都是低功耗、节能型芯片,主要用于便携机和节能型台式机。

微处理器思考与习题

第1章思考与习题: 1、简述计算机系统的硬件构成和软件构成。 计算机的硬件结构由运算器、控制器、存储器、输入设备、输出设备及连接各部件的总线组成。 其中,运算器又称为算术/逻辑运算单元,完成数据的算术(加、减、乘、除)和逻辑(与、或、非、异)等运算以及移位等操作,它是一个采用二进制运算信息加工部件。 存储器是计算机的记忆部件,存储控制计算机操作的命令(指令)和被处理的信息数据,并对处理结果加以保存。存储器存储的信息有两类:一类是命令信息,指挥计算机系统工作,用来完成所设计的任务,这类信息被存放在存储器的代码区或程序区;另一类是数据是指被处理的对象或结果,这类信息被存放在数据区。一般将存储器分为两级:内存和外存,目前使用的内存是半导体存储器,外存采用硬盘、磁带、光盘等。平时程序保存在外存,执行时再将其调入内存中运行。狭义的存储器仅指内存储器。 控制器是整个系统的指挥部件,对运行的指令逐一分析,发出控制信号并执行其相应操作。 输入设备与输出设备,通称外围设备,是对信息形式的转换,如将语言文字、声音、机械动作等信息形式转换为计算机能识别的二进制格式信息,或将其反向转换。 总线是计算机各部件间传输信息的公共通道,各部件分时复用总线,满足数据、地址、指令和控制信息在各部件之间快速传送的需要。 微型计算机的软件由系统软件和应用软件构成。 系统软件包括操作系统、程序设计语言的编译程序和其他程序。 操作系统是常驻内存的软件系统,包括系统资源管理(CPU管理,存储器管理、I/O管理和驱动程序)、任务管理、文件管理和程序库。为使用者提供灵活方便操作功能,使资源得到最充分有效的利用。 各种程序设计语言的编译系统为用户开发应用软件提供有力支持,如汇编语言的汇编程序,各种高级语言的汇编程序、连接程序以及各种调试工具。 其他程序,如系统诊断程序、故障定位程序、系统配置程序等。 应用软件(或称用户软件)是为用户实现给定的任务而编写、选购或订购的程序,它只适合给定环境的指定用途,一般驻留在外部存储器中,只在运行时才调入内存储器。 2、冯·诺依曼体系结构的五个部件是什么?总线的作用是什么?

微处理器和微控制器区别与DSP芯片分类及特点简介

微处理器和微控制器区别与DSP芯片分类及特点简介 中央处理器是一块超大规模的集成电路,是一台计算机的运算核心和控制核心,它的功能主要是解释计算机指令以及处理计算机软件中的数据。 主要包括运算器和高速缓冲存储器及实现它们之间联系的数据、控制及状态的总线。它与内部存储器和输入/输出设备合称为电子计算机三大核心部件。 目前,嵌入式处理器的高端产品有:Advanced RISC Machines公司的ARM、Silicon Graphics 公司的MIPS、IBM和Motorola的Power PC 、Intel的X86和i960芯片、AMD的Am386EM、Hitachi的SH RISC芯片; 掌上电脑的处理器有六类处理器,分别是:英特尔的PXA系列处理器、MIPS处理器、StrongARM系列处理器、日立SH3处理器、摩托罗拉龙珠系列处理器和德州仪器OMAP 系列处理器。 微处理器和微控制器区别所在微处理器和微控制器的区别,这样的区别主要集中在硬件结构、应用领域和指令集特征三个方面: 其一,硬件结构。 微处理器是一个单芯片CPU,而微控制器则在一块集成电路芯片中集成了CPU和其他电路,构成了一个完整的微型计算机系统。 除了CPU,微控制器还包括RAM、ROM、一个串行接口、一个并行接口,计时器和中断调度电路。虽然片上RAM的容量比普通微型计算机系统还要小,但是这并未限制微控制器的使用。 在后面可以了解到,微控制器的应用范围非常广泛。其中,微控制器的一个重要的特征是内建的中断系统。作为面向控制的设备,微控制器经常要实时响应外界的激励。 其二,应用领域。 微处理器通常作为微型计算机系统中的CPU使用,其设计正是针对这样的应用,这也是微处理器的优势所在。 然而,微控制器通常用于面向控制的应用,系统设计追求小型化,尽可能减少元器件数量。

Intel微处理器发展史

Intel官方超高清大图:微处理器发展40周年 1971年11月15日,Intel 开发了全球第一款微处理器“Intel 4004”,时至今日即将整整40年。为了纪念这历史性的一刻,Intel 今天放出了大量珍贵的历史资料,尤其是历代17款处理器的超高清大图特写(外壳与内核),值得收藏,不容错过。 首先来看一段老祖宗4004与当今最快处理器Sandy Bridge Core i7 的有趣对比: 1、对比晶体管速度,4004就像是蜗牛,每小时前进5米,而现在就是肯尼亚选手帕特里克·马卡乌·穆斯约基今年9月25日在德国柏林创造的马拉松长跑记录:2小时3分38秒,平均时速20.6公里。从频率上对比,二者就分别是蜗牛和闪电博尔特。 2、如今一台笔记本每年的能耗价值约25欧元(¥220),而如果1971年来处理器功耗不变,如今的笔记本每年要在能耗上支出大约10万欧元(¥87万元),没几个人能用得起。 3、4004的内核包含2300个晶体管,Sandy Bridge 则是9.95亿个,就像一个小村落和整个中国的人口对比。如果每颗晶体管都是一粒米,9.95亿颗足够波兰波兹南、德国斯图加特、英国格拉斯哥或者任何56.7万左右人口的大城市的所有人都饱饱地吃上一顿。 4、Sandy Bridge 采用32纳米工艺制造,内核面积216平方毫米,而如果使用4004的10微米工艺,Sandy Bridge 的内核面积将是21平方米,或者说7×3米。感谢摩尔定律。 5、4004的频率为74KHz,Sandy Bridge 则可达4GHz 左右。如果汽车的速度也照此提升,那么今天从旧金山开到纽约,或者从葡萄牙里斯本开到俄罗斯莫斯科,都只需要1秒钟。 6、从4004到Sandy Bridge,晶体管的速度提升了5000倍,功耗只有当初的5000分之一,价格则降低到了50000分之一。 7、贝尔实验室1947年发明的晶体管有一个手掌那么大,而在22nm 三栅极工艺下,一个针头(直径约1.5毫米)的空间就能放下10多亿个晶体管。

国内的微处理器介绍

关键字: register:寄存器interface:接口analog:模拟semiconductor:微处理器combination:混合体capacitor :电容器diode:二极管comparator:比较器loop:循环 polarity:极性potential:电位pickup:传感器circuitry:电路图resistance:电阻leakage:泄露电阻filt:过滤器current:电流buffering:缓冲器impedance:阻抗offset:补偿diode:二极管 国内的微处理器: ADC08031/ADC08032/ADC08034/ADC08038 8位高速单任务处理的I/O A/D转换器有多种传输方式,提高电压,和跟踪/控制功能 综述: ADC08031/ADC08032/ADC08034/ADC08038是8位连续的近似A/D转换器,有一系列I/O和配置输入多大8种方式,一系列的I/O被装置以达成NSCMICROWIRE TM的标准。简单连接COPS TM流派控制的一系列数据转换标准,也能简单连接标准转移寄存器或微处理器。 ADC08034和ADC08038提供一个2.6V中断源参考材料,为装置提供保障的电压参考温。以ADC08031/ADC08034和ADC08038为特点,一个跟踪/控制功能允许在现实A/D转换中在正极输入多种模拟电压。模拟输入被装置成操作各种但极点的有区别的,或假定一有区别的代码的混合体。总之,输入模拟跨度最小1V才能被容纳。 用途: 1,使自动传感器数字化。 2,程序控制监督程序。 3,在噪音环境中有遥感功能。 4,检测仪器。 5,测试系统。 6,嵌入式特征。 特征: 1,单任务处理器的数据连接要求少量的I/O插口。 2,模拟输入跟踪控制功能。 3,2- ,4-或8位输入多种逻辑地址的传输方式。 4,0V~5V模拟输入范围提供单极5V电压。 5,没有零或满的尺度判断要求。 6,TTL/CMOS输入/输出兼容。 7,在集成电路片上2.6V中断源参考材料。 8,0.3标准宽度.14或20个插口插入插件。 9,20个插口的微型插件 码的规范:

微处理器选型

微处理器模块选型 在产品开发中, 作为核心芯片的微处理器, 其自身的功能、性能、可靠性被寄予厚望, 因为它的资源越丰富、自带功能越强大, 产品开发周期就越短, 项目成功率就越高。 微处理器选型的考虑因素 1.应用领域 一个产品的功能、性能一旦定制下来, 其所在的应用领域也随之确定。要考虑产品工作温度,湿度等条件。 2.自带资源 主频是多少? 有无内置的以太网M A C? 有多少个I / O 口? 自带哪些接口? 支持在线仿真吗? 是否支持OS, 能支持哪些OS? 是否有外部存储接口? 芯片。自带资源越接近产品的需求, 产品开发相对就越简单。 3.可扩展资源 硬件平台要支持O S、RAM 和ROM , 对资源的要求就比较高。有些芯片内置容量比较小,这就要求芯片可扩展存储器。 4.功耗 低功耗的产品即节能又节财, 甚至可以减少环境污染, 它有如此多的优点,因此低功耗也成了芯片选型时的一个重要指标。 5.封装 常见的微处理器芯片封装主要有QFP、BGA两大类型。如果产品对芯片体积要求不严格, 选型时最好选择QFP封装。 6.芯片的可延续性及技术的可继承性 目前, 产品更新换代的速度很快, 所以在选型时要考虑芯片的可升级性。应该考虑知名半导体公司,然后查询其相关产品, 再作出判断。 7.价格及供货保证 许多芯片目前处于试用阶段( sam pling ) , 其价格和供货就会处于不稳定状态, 所以选型时尽量选择有量产的芯片。 8.仿真器 已经有仿真器的时候, 在选型过程中要考虑它是否支持所选的芯片。 9.OS 及开发工具 对于已有OS 的人们, 在选型过程中要考虑所选的芯片是否支持该OS, 也可以反过来说, 即这种OS 是否支持该芯片。 10.技术支持 一个好的公司的技术支持能力相对比较有保证, 所以选芯片时最好选择知名的半导体公司。

微处理器的发展史

二、微处理器的发展历史 你知道神奇的计算机芯片是用什么材料制成的吗?Intel公司的创始人摩尔曾 有过这样一段精彩的解释:我们需要为芯片寻找一种基质,因此我们考察了地球的基质,它主要是沙粒,所以我们使用了沙粒(硅可由海沙滤取而得)。我们需要为芯片上的线路和开头寻找一种金属导体,我们考察了地球上的所有金属,发现铝是最丰富的,所以我们使用了铝。下面让我们循着Intel公司的发展历程,去探寻中央处理器的发展史。 1971年,Intel公司首先推出了世界上第一个4位微处理器芯片Intel 4004,它集成了2300个晶体管,同年,第一台使用了4004芯片的微型计算机诞生了。1972年Intel公司推出了8位微处理器芯片8008,之后的几年中,8位微型计算机得到了飞速的发展,并打开了一定的市场,其中最为著名的是苹果公司的A pple II。1978年Intel公司推出了16位微处理器芯片8086,主频为5~8MHz。随后又有80186、80188、80286等16位芯片出现。这一阶段在微型计算机市场大获成功的是IBM公司的IBM PC。1985年Intel公司推出32位微处理器80386,指令中增加了页式存储管理,加强了图形处理的能力。同一年,Microsoft (微软)公司推出了Windows 操作系统,这是微型计算机操作系统的一次革命性的进步。1989年Intel公司研制成功80486芯片。微型计算机市场日趋繁荣,出现了百家争鸣的局面。 1993年Intel公司公布了新一代的处理器80586,并给它起了个商品名Pentium (奔腾),简称P5,集成度为310万个器件/片,时钟频率为60~133MHz,1995年2月Intel公司推出了Pentium Pro芯片,简称P6,集成度为550万个器件/片,时钟频率为133MHz,1997年1月Intel公司推出了第一片带MMX技术的多功能奔腾处理器。MMX是Multi-Media Extensions(多媒体扩展)的缩写,是为加快多媒体操作运算而在CPU内部新增了57条指令。这57条指令是特别为音频信号、视频信号以及影像处理而设计的,从而使得本来由声卡、解压卡、显示卡等支持的部分工作,又可以回到高速的CPU中完成。1997年下半年起,各CPU制造商竞相将MMX技术纳入32位及64位微处理器中。1998年的PentiumII是带有MM X技术的P6级的微处理器,内含750万个晶体管,主频普遍在200MHz以上。19 99年2月Intel公司又推出了PentiumIII,其核心速度在 450MHz以上。Penti umIII是在PentiumII的基础上新增加了70条能够增强音频、视频和3D图形效果的SSE(Streaming SIMI Extensions,数据流单指令多数据扩展)指令集。200 0年Intel公司推出了Pentium IV微处理器,主频达到1GMHz以上。 纵观计算机的发展历史,微处理器性能的不断提高是计算机应用得以迅速发展的真正动力,它比历史上任何发明都进展得更为迅速。

微处理器系统结构与嵌入式系统设计(第二版)答案全

微处理器系统结构与嵌入式系统设计(第二版)答案全

一 1.2 以集成电路级别而言,计算机系统的三个主要组成部分是什么? 中央处理器、存储器芯片、总线接口芯片 1.3 阐述摩尔定律。 每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。 1.5 什么是SoC?什么是IP核,它有哪几种实现形式? SoC:系统级芯片、片上系统、系统芯片、系统集成芯片或系统芯片集等,从应用开发角度出发,其主要含义是指单芯片上集成微电子应用产品所需的所有功能系统。 IP核:满足特定的规范和要求,并且能够在设计中反复进行复用的功能模块。它有软核、硬核和固核三种实现形式。 1.8 什么是嵌入式系统?嵌入式系统的主要特点有哪些? 概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗的严格要求的专用计算机系统,即“嵌入到应用对象体系中的专用计算机系统”。 特点:1、嵌入式系统通常是面向特定应用的。 2、嵌入式系统式将先进的计算机技术、半导体技术和电子技术与各个行业的具体应用相结合的产物。 3、嵌入式系统的硬件和软件都必须高效率地设计,量体裁衣、去除冗余,力争在同样的硅片面积上实现更高的性能。

4、嵌入式处理器的应用软件是实现嵌入式系统功能的关键,对嵌入式处理器系统软件和应用软件的要求也和通用计算机有以下不同点。 ①软件要求固体化,大多数嵌入式系统的软件固化在只读存储器中; ②要求高质量、高可靠性的软件代码; ③许多应用中要求系统软件具有实时处理能力。 5、嵌入式系统和具体应用有机的结合在一起,它的升级换代也是和具体产品同步进行的,因此嵌入式系统产品一旦进入市场,就具有较长的生命周期。 6、嵌入式系统本身不具备自开发能力,设计完成以后用户通常也不能对其中的程序功能进行修改,必须有一套开发工具和环境才能进行开发。 二 2.2 完成下列逻辑运算 (1)101+1.01 = 110.01 (2)1010.001-10.1 = 111.101 (3)-1011.0110 1-1.1001 = -1100.1111 1 (4)10.1101-1.1001 = 1.01 (5)110011/11 = 10001 (6)(-101.01)/(-0.1) = 1010.1 2.3 完成下列逻辑运算 (1)1011 0101∨1111 0000 = 1111 0101 (2)1101 0001∧1010 1011 = 1000 0001 (3)1010 1011⊕0001 1100 = 1011 0111

微处理器系统结构与嵌入式系统设计(第二版)答案全

一 1.2 以集成电路级别而言,计算机系统的三个主要组成部分是什么? 中央处理器、存储器芯片、总线接口芯片 1.3 阐述摩尔定律。 每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。 1.5 什么是SoC?什么是IP核,它有哪几种实现形式? SoC:系统级芯片、片上系统、系统芯片、系统集成芯片或系统芯片集等,从应用开发角度出发,其主要含义是指单芯片上集成微电子应用产品所需的所有功能系统。 IP核:满足特定的规范和要求,并且能够在设计中反复进行复用的功能模块。它有软核、硬核和固核三种实现形式。 1.8 什么是嵌入式系统?嵌入式系统的主要特点有哪些? 概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗的严格要求的专用计算机系统,即“嵌入到应用对象体系中的专用计算机系统”。 特点:1、嵌入式系统通常是面向特定应用的。 2、嵌入式系统式将先进的计算机技术、半导体技术和电子技术与各个行业的具体应用相结合的产物。 3、嵌入式系统的硬件和软件都必须高效率地设计,量体裁衣、去除冗余,力争在同样的硅片面积上实现更高的性能。

4、嵌入式处理器的应用软件是实现嵌入式系统功能的关键,对嵌入式处理器系统软件和应用软件的要求也和通用计算机有以下不同点。 ①软件要求固体化,大多数嵌入式系统的软件固化在只读存储器中; ②要求高质量、高可靠性的软件代码; ③许多应用中要求系统软件具有实时处理能力。 5、嵌入式系统和具体应用有机的结合在一起,它的升级换代也是和具体产品同步进行的,因此嵌入式系统产品一旦进入市场,就具有较长的生命周期。 6、嵌入式系统本身不具备自开发能力,设计完成以后用户通常也不能对其中的程序功能进行修改,必须有一套开发工具和环境才能进行开发。 二 2.2 完成下列逻辑运算 (1)101+1.01 = 110.01 (2)1010.001-10.1 = 111.101 (3)-1011.0110 1-1.1001 = -1100.1111 1 (4)10.1101-1.1001 = 1.01 (5)110011/11 = 10001 (6)(-101.01)/(-0.1) = 1010.1 2.3 完成下列逻辑运算 (1)1011 0101∨1111 0000 = 1111 0101 (2)1101 0001∧1010 1011 = 1000 0001 (3)1010 1011⊕0001 1100 = 1011 0111 2.4 选择题

ARM微处理器概述

ARM微处理器概述 ARM微处理器概述 ARM公司简介 ARM于1990年11月在英国伦敦成立,前身为Acorn['eik?:n]计算机公司Advance RISC Machines [m?'?i:n] (ARM) 全球领先的16/32位嵌入式RISC微处理器解决方案供应商。 ARM公司是知识产权(IP Intellectual [,int?'lektju?l, -t?u?l] Property ['pr?p?ti])公司,本身不生产芯片,靠转让设计许可,由合作伙伴公司来生产各具特色的芯片。 目前,全世界有几十家著名的半导体公司都使用ARM公司的授权,其中包括摩托罗拉、IBM、Intel、SONY、NEC、LG、ATMEL等,从而保证了大量的开发工具和丰富的第三方资源,它们共同保证了基于ARM处理器核的设计可以很快投入市场。 ARM公司已成为移动通信、手持设备、多媒体数字消费嵌入式解决方案的RISC标准。 ARM微处理器的特点 采用RISC架构的ARM微处理器一般具有如下特点: ●体积小、低功耗、低成本、高性能; ●支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件; ●大量使用寄存器,指令执行速度更快; ●大多数数据操作都在寄存器中完成; ●寻址方式灵活简单,执行效率高; ●指令长度固定。 ARM体系结构 ARM体系结构的版本 ARM指令集体系结构,从最初开发至今已有了重大改进,而且将会不断完善和发展。为了精确表达每个ARM实现中所使用的指令集,到目前ARM体系结构共定义了7个版本,以版本号v1~v7表示。 1. 版本1(v1) 基本数据处理指令(不包括乘法)。 字节、字以及半字加载/存储指令。 分支(branch [brɑ:nt?, br?nt?])指令,包括用于子程序调用的分支与链接(branch-and-link)指令。 软件中断指令,用于进行操作系统调用。 26位地址总线。 使用此版本的处理器核:ARM1 2. 版本2(v2)

微处理器的主要组成部分

微处理器的主要组成部分 (资料来源:中国联保网) 微处理器由算术逻辑单元(ALU,Arithmetic Logical Unit);累加器和通用寄存器组;程序计数器(也叫指令指标器);时序和控制逻辑部件;数据与地址锁存器/缓冲器;内部总线组成。其中运算器和控制器是其主要组成部分. 算术逻辑单元 算术逻辑单元ALU主要完成算术运算(+,-、×、÷、比较)和各种逻辑运算(与、或、非、异或、移位)等操作。ALU是组合电路,本身无寄存操作数的功能,因而必须有保存操作数的两个寄存器:暂存器TMP和累加器AC,累加器既向ALU提供操作数,又接收ALU的运算结果。 寄存器阵列实际上相当于微处理器内部的RAM,它包括通用寄存器组和专用寄存器组两部分,通用寄存器(A,B,C,D)用来存放参加运算的数据、中间结果或地址。它们一般均可作为两个8位的寄存器来使用。处理器内部有了这些寄存器之后,就可避免频繁地访问存储器,可缩短指令长度和指令执行时间,提高机器的运行速度,也给编程带来方便。专用寄存器包括程序计数器PC、堆栈指示器SP和标志寄存器FR,它们的作用是固定的,用来存放地址或地址基值。其中: A)程序计数器PC用来存放下一条要执行的指令地址,因而它控制着程序的执行顺序。在顺序执行指令的条件下,每取出指令的一个字节,PC的内容自动加1。当程序发生转移时,就必须把新的指令地址(目标地址)装入PC,这通常由转移指令来实现。 B)堆栈指示器SP用来存放栈顶地址。堆栈是存储器中的一个特定区域。它按“后进先出”方式工作,当新的数据压入堆栈时,栈中原存信息不变,只改变栈顶位置,当数据从栈弹出时,弹出的是栈顶位置的数据,弹出后自动调正栈顶位置。也就是说,数据在进行压栈、出栈操作时,总是在栈顶进行。堆栈一旦初始化(即确定了栈底在内存中的位置)后,SP的内容(即栈顶位置)使由CPU自动管理。 C)标志寄存器也称程序状态字(PSW)寄存器,用来存放算术、逻辑运算指令执行后的结果特征,如结果为0时,产生进位或溢出标志等。 定时与控制逻辑是微处理器的核心控制部件,负责对整个计算机进行控制、包括从存储器中取指令,分析指令(即指令译码)确定指令操作和操作数地址,取操作数,执行指令规定的操作,送运算结果到存储器或I/O端口等。它还向微机的其它各部件发出相应的控制信号,使C PU内、外各部件间协调工作。

单片机及微处理器种类及介绍

1.单片机:1)51系列单片机51 单片机目前已有多种型号,8031/8051/8751是Intel公司早期的产品,而ATMEL 公司的AT89C51、A T89S52则更实用。ATMEL公司的51系列还有AT89C2051、AT89C1051等品种,这些芯片是在AT89C51的基础上将一些功能精简掉后形成的精简版。而市场上目前供货比较足的芯片还要算ATMEL 的51、52 芯片,HYUNDAI 的GMS97 系列,WINBOND 的78e52,78e58,77e58 等。2)PIC系列单片机在全球都可以看到PIC单片机从电脑的外设、家电控制、电讯通信、智能仪器、汽车电子到金融电子各个领域的广泛应用。PIC系列单片机又分:基本级系列,如PIC16C5X,适用于各种对成本要求严格的家电产品选用;中级系列,如PIC12C6XX,该级产品其性能很高,如内部带有A/D变换器、E2PROM数据存储器、比较器输出、PWM输出、I2C和SPI等接口;PIC中级系列产品适用于各种高、中和低档的电子产品的设计中。高级系列,如PIC17CXX 具有丰富的I/O控制功能,并可外接扩展EPROM和RAM,适用于高、中档的电子设备中使用。3)A VR系列单片机A VR单片机是1997年由ATMEL公司研发出的增强型内置Flash的RISC(Reduced Instruction Set CPU) 精简指令集高速8位单片机。A VR的单片机可以广泛应用于计算机外部设备、工业实时控制、仪器仪表、通讯设备、家用电器等各个领域。 2. CPLD/FPGA CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。许多公司如今都开发出了CPLD可编程逻辑器件。比较典型的就是Altera、Lattice、Xilinx 世界三大权威公司的产品,这里给出常用芯片:Altera EPM7128S(PLCC84)、Lattice LC4128V (TQFP100)、Xilinx XC95108 (PLCC84) FPGA是英文Field-Programmable Gate Array 的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。目前FPGA的品种很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FIEX系列等。 3. DSP DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。目前主流的DSP芯片主要有TI公司的TI 2000系列、TI 5000系列、TI6000系列以及ADI公司的ADI DSP系列。 4.ARM ARM 即Advanced RISCMachines的缩写是对一类微处理器的通称. ARM同时还是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。技术具有性能高、成本低和能耗省的特点。适用于多种领域,比如嵌入控制、消费/教育类多媒体、DSP和移动式应用等。目前ARM的主流分以下几类:ARM7TDMI 应用于Game Boy Advance,Nintendo DS,iPod ARM9TDMI Armadillo,GP32,GP2X(第一颗内核), Tapwave Zodiac(Motorolai. MX1);GP2X(第二颗内核)ARM9E Nintendo DS,Nokia N-GageConexant 802.11 chips;ST Micro STR91xF,ARM11 Nokia N93,Zune,Nokia N800,NOKIA E72 Cortex Texas Instruments OMAP3;Broadcomis a user;Luminary Micro[3] 微控制器家族 5. MIPS MIPS是世界上很流行的一种RISC处理器。MIPS 的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。MIPS最早是在80年代初期