DDS技术之生成正弦波

https://www.sodocs.net/doc/149552396.html,/csf111/article/details/6944148

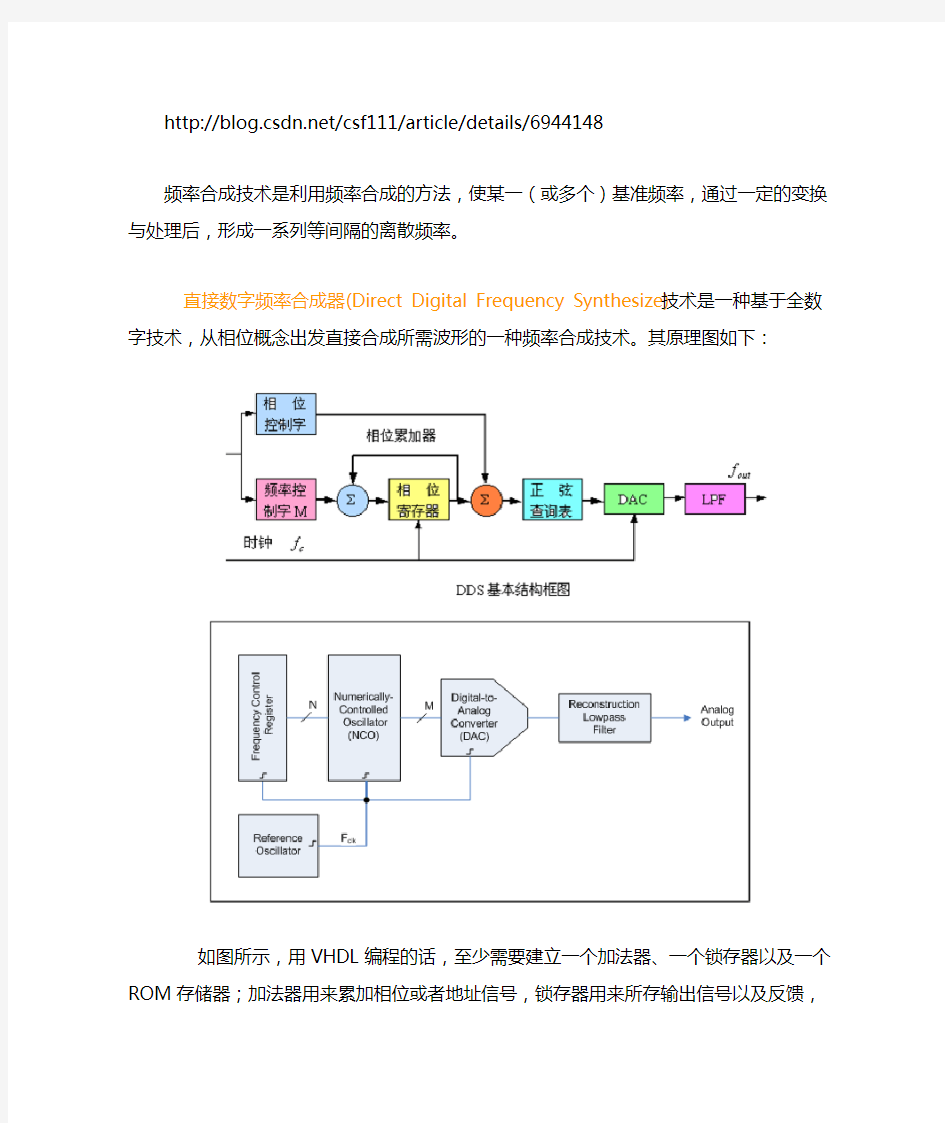

频率合成技术是利用频率合成的方法,使某一(或多个)基准频率,通过一定的变换与处理后,形成一系列等间隔的离散频率。

直接数字频率合成器(Direct Digital Frequency Synthesize)技术是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。其原理图如下:

如图所示,用VHDL编程的话,至少需要建立一个加法器、一个锁存器以及一个ROM存储器;加法器用来累加相位或者地址信

号,锁存器用来所存输出信号以及反馈,ROM存储器则用来存储波形数据的数字幅度;最后还需要一个总得模块将三者结合在一起。

首先:建立ROM表;

在quartus II上面使用LPM_ROM,就必须学会MegaWizard Plug-in Manager的用法,要用MegaWizard Plug-in Manager,那么就必须先学会创建mif或者hex文件,下面具体以正弦波为例,介绍mif文件的创建方法以及如何调用LPM_ROM。

1、创建mif文件的三种方法(其实不只三种,下面就我调试成功的来一一说明,并且附上源代码吧):

根据需要设置每个字的位宽WIDTH和总字数DEPTH。然后设置地址和数据的进制基数ADDRESS_RADIX、DATA_RADIX,使用无符号数UNS。然后用如下方法生成需要的数据(按上边的格式,注意中间“:”,最后“;”),往CONTENT BEGIN和END中间一贴就行了。

1)用VC++软件编程实现:

[cpp]view plaincopyprint?

1.#include

2.#include

3.#include

4.void main()

5.{

6.double pi=3.141593;

7.double step=pi*2/256;

8. ofstream outfile;

9. outfile.open("si

n.mif");

10. outfile<<"--Maxplus Memory Initiallization F

ile"< 11. outfile<<"--sin.mif"< 12. outfile<<"WIDTH=8;"< 13. outfile<<"DEPTH=256;"< 14. outfile<<"ADDRESS_RADIX=HEX;"< 15. outfile<<"DATA_RADIX=DEC;"< 16. outfile<<"CONTENT BEGIN"< 17.for(int i=0;i<256;i++) 18. { 19. outfile<<he x< 20. } 21. outfile<<"END;"; 22.} 2)用Matlab编程实现: 创建.m文件 [cpp]view plaincopyprint? 1.width=8; %数据宽度为10位; 2.depth=2^width; 3.N=0:1:depth-1; 4.s=sin(pi*N/depth); %计算0~pi/2的Sin 值; 5.fidc=fopen('sin_matlab.mif','wt'); %以"wt" 的形式打开,\n为换行 6.% 写入 sin_matlab.mif % 7.fprintf(fidc,'width=%d;\n',width); 8.fprintf(fidc,'depth=%d;\n',depth); 9.fprintf(fidc,'address_radix=uns;\n'); 10.f printf(fidc,'data_radix = uns;\n'); 11.f printf(fidc,'content begin\n'); 12.f or(x=1:depth); 13.f printf(fidc,'%d:%d;\n',x-1, round( (depth/2-1)* sin(pi*(x-1)/(depth/2)) + depth/2) ); 14.e nd 15.f printf(fidc,'end;'); 16.f close(fidc); 3)用软件Guagle_wave.exe自动生成mif或者hex文件 软件下载地址:https://www.sodocs.net/doc/149552396.html,/detail/csf111/3766264 2、使用tools\MegaWizard Plug-in Manager来新建LPM_ROM,具体方法不讲述,只要quartus II软件当中去了,相应的设置选项都很容易懂的,主要是要设置你的ROM地址宽度和数据点数,其间需要调用mif文件的,选择你刚才建立的mif即可; 3、上面几步完成之后,quartus II 就会自动生成一个VHD文件,如下: [cpp]view plaincopyprint? 1.-- megafunction wizard: %ROM: 1-PORT% 2.-- GENERATION: STANDARD 3.-- VERSION: WM1.0 4.-- MODULE: lpm_rom 5. 6.-- ============================================== ============== 7.-- File Name: lpm_rom8.vhd 8.-- Megafunction Name(s): 9.-- lpm_rom 10.-- 11.-- Simulation Library Files(s): 12.-- lpm 13.-- ============================================= =============== 14.-- ********************************************* *************** 15.-- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! 16.-- 17.-- 8.1 Build 163 10/28/2008 SJ Full Version 18.-- ********************************************* *************** 19. 20. 21.--Copyright (C) 1991-2008 Altera Corporation 22.--Your use of Altera Corporation's design tools, logic functions 23.--and other software and tools, and its AMPP par tner logic 24.--functions, and any output files from any of th e foregoing 25.--(including device programming or simulation fi les), and any 26.--associated documentation or information are ex pressly subject 27.--to the terms and conditions of the Altera Prog ram License 28.--Subscription Agreement, Altera MegaCore Functi on License 29.--Agreement, or other applicable license agreeme nt, including, 30.--without limitation, that your use is for the s ole purpose of 31.--programming logic devices manufactured by Alte ra and sold by 32.--Altera or its authorized distributors. Please refer to the 33.--applicable agreement for further details. 34. 35. 36.L IBRARY ieee; 37.U SE ieee.std_logic_1164.all; 38. 39.L IBRARY lpm; 40.U SE lpm.all; 41. 42.E NTITY lpm_rom8 IS 43. PORT 44. ( 45. address : IN STD_LOGIC_VECTOR (7 DOW NTO 0); 46. inclock : IN STD_LOGIC ; 47. q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) 48. ); 49.E ND lpm_rom8; 50. 51. 52.A RCHITECTURE SYN OF lpm_rom8 IS 53. 54. SIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DO WNTO 0); 55. 56. 57. 58. COMPONENT lpm_rom 59. GENERIC ( 60. intended_device_family : STRING; 61. lpm_address_control : STRING; 62. lpm_file : STRING; 63. lpm_outdata : STRING; 64. lpm_type : STRING; 65. lpm_width : NATURAL; 66. lpm_widthad : NATURAL 67. ); 68. PORT ( 69. address : IN STD_LOGIC_VECTOR (7 DOW NTO 0); 70. inclock : IN STD_LOGIC ; 71. q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) 72. ); 73. END COMPONENT; 74. 75.B EGIN 76. q <= sub_wire0(7 DOWNTO 0); 77. 78. lpm_rom_component : lpm_rom 79. GENERIC MAP ( 80. intended_device_family => "FLEX10K", 81. lpm_address_control => "REGISTERED", 82. lpm_file => "sin_soft.mif", 83. lpm_outdata => "UNREGISTERED", 84. lpm_type => "LPM_ROM", 85. lpm_width => 8, 86. lpm_widthad => 7 87. ) 88. PORT MAP ( 89. address => address, 90. inclock => inclock, 91. q => sub_wire0 92. ); 93. 94. 95. 96.E ND SYN; 97. 98.-- ============================================= =============== 99.-- CNX file retrieval info 100.-- ========================================== ================== 101.-- Retrieval info: PRIVATE: ADDRESSSTALL_A NU MERIC "0" 102.-- Retrieval info: PRIVATE: AclrAddr NUMERIC "0" 103.-- Retrieval info: PRIVATE: AclrByte NUMERIC "0" 104.-- Retrieval info: PRIVATE: AclrOutput NUMERI C "0" 105.-- Retrieval info: PRIVATE: BYTE_ENABLE NUMER IC "0" 106.-- Retrieval info: PRIVATE: BYTE_SIZE NUMERIC "8" 107.-- Retrieval info: PRIVATE: BlankMemory NUMER IC "0" 108.-- Retrieval info: PRIVATE: CLOCK_ENABLE_INPU T_A NUMERIC "0" 109.-- Retrieval info: PRIVATE: CLOCK_ENABLE_OUTP UT_A NUMERIC "0" 110.-- Retrieval info: PRIVATE: Clken NUMERIC "0" 111.-- Retrieval info: PRIVATE: IMPLEMENT_IN_LES NUMERIC "0" 112.-- Retrieval info: PRIVATE: INIT_FILE_LAYOUT STRING "PORT_A" 113.-- Retrieval info: PRIVATE: INIT_TO_SIM_X NUM ERIC "0" 114.-- Retrieval info: PRIVATE: INTENDED_DEVICE_F AMILY STRING "FLEX10K" 115.-- Retrieval info: PRIVATE: JTAG_ENABLED NUME RIC "0" 116.-- Retrieval info: PRIVATE: JTAG_ID STRING "N ONE" 117.-- Retrieval info: PRIVATE: MAXIMUM_DEPTH NUM ERIC "0" 118.-- Retrieval info: PRIVATE: MIFfilename STRIN G "sin_soft.mif" 119.-- Retrieval info: PRIVATE: NUMWORDS_A NUMERI C "128" 120.-- Retrieval info: PRIVATE: OutputRegistered NUMERIC "0" 121.-- Retrieval info: PRIVATE: RAM_BLOCK_TYPE NU MERIC "0" 122.-- Retrieval info: PRIVATE: RegAdd NUMERIC "1 " 123.-- Retrieval info: PRIVATE: RegAddr NUMERIC " 1" 124.-- Retrieval info: PRIVATE: RegOutput NUMERIC "0" 125.-- Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN _POSTFIX STRING "0" 126.-- Retrieval info: PRIVATE: SingleClock NUMER IC "0" 127.-- Retrieval info: PRIVATE: UseDQRAM NUMERIC "0" 128.-- Retrieval info: PRIVATE: WidthAddr NUMERIC "7" 129.-- Retrieval info: PRIVATE: WidthData NUMERIC "8" 130.-- Retrieval info: PRIVATE: rden NUMERIC "0" 131.-- Retrieval info: CONSTANT: INTENDED_DEVICE_ FAMILY STRING "FLEX10K" 132.-- Retrieval info: CONSTANT: LPM_ADDRESS_CONT ROL STRING "REGISTERED" 133.-- Retrieval info: CONSTANT: LPM_FILE STRING "sin_soft.mif" 134.-- Retrieval info: CONSTANT: LPM_OUTDATA STRI NG "UNREGISTERED" 135.-- Retrieval info: CONSTANT: LPM_TYPE STRING "LPM_ROM" 136.-- Retrieval info: CONSTANT: LPM_WIDTH NUMERI C "8" 137.-- Retrieval info: CONSTANT: LPM_WIDTHAD NUME RIC "7" 138.-- Retrieval info: USED_PORT: address 0 0 7 0 INPUT NODEFVAL address[6..0] 139.-- Retrieval info: USED_PORT: inclock 0 0 0 0 INPUT NODEFVAL inclock 140.-- Retrieval info: USED_PORT: q 0 0 8 0 OUTPU T NODEFVAL q[7..0] 141.-- Retrieval info: CONNECT: @address 0 0 7 0 address 0 0 7 0 142.-- Retrieval info: CONNECT: q 0 0 8 0 @q 0 0 8 0 143.-- Retrieval info: CONNECT: @inclock 0 0 0 0 inclock 0 0 0 0 144.-- Retrieval info: LIBRARY: lpm lpm.lpm_compo nents.all 145.-- Retrieval info: GEN_FILE: TYPE_NORMAL lpm_ rom8.vhd TRUE 146.-- Retrieval info: GEN_FILE: TYPE_NORMAL lpm_ rom8.inc FALSE 147.-- Retrieval info: GEN_FILE: TYPE_NORMAL lpm_ rom8.cmp TRUE 148.-- Retrieval info: GEN_FILE: TYPE_NORMAL lpm_ rom8.bsf FALSE 149.-- Retrieval info: GEN_FILE: TYPE_NORMAL lpm_ rom8_inst.vhd FALSE 150.-- Retrieval info: LIB_FILE: lpm 其次,建立锁存器模块; [cpp]view plaincopyprint? 1.LIBRARY IEEE; https://www.sodocs.net/doc/149552396.html,E IEEE.STD_LOGIC_1164.ALL; 3.ENTITY REG8B IS 4. PORT ( Load : IN STD_LOGIC; 5. DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 6. DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); 7.END REG8B; 8.ARCHITECTURE behav OF REG8B IS 9.BEGIN 10. PROCESS(Load, DIN) 11. BEGIN 12. IF Load'EVENT AND Load = '1' THEN -- 时钟到 来时,锁存输入数据 13. DOUT <= DIN; 14. END IF; 15. END PROCESS; 16.E ND behav; 第三,建立加法器模块; [cpp]view plaincopyprint? 1.LIBRARY IEEE; https://www.sodocs.net/doc/149552396.html,E IEEE.STD_LOGIC_1164.ALL; https://www.sodocs.net/doc/149552396.html,E IEEE.STD_LOGIC_UNSIGNED.ALL; 4.ENTITY ADDER8B IS 5. PORT ( A : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 6. B : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 7. S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)) ; 8.END ADDER8B; 9.ARCHITECTURE behav OF ADDER8B IS 10. BEGIN 11. S <= A + B; 12.E ND behav; 第四,顶层模块的设计; [cpp]view plaincopyprint? 1.------------------------------------------------- -------------------- 2.-- Designed By Michael Chen( chen sifan) --- 3.-- 2 011\11\07 --- 4.------------------------------------------------- -------------------- 5.LIBRARY IEEE; https://www.sodocs.net/doc/149552396.html,E IEEE.STD_LOGIC_1164.ALL; https://www.sodocs.net/doc/149552396.html,E IEEE.STD_LOGIC_UNSIGNED.ALL; 8.------------------------------------------------- -------------------- 9.ENTITY mydds IS -- 顶层设计 10. PORT ( 11. CLK : IN STD_LOGIC; 12. FWORD : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 13. FOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); 14.E ND mydds; 15.------------------------------------------------ --------------------- 16.A RCHITECTURE behav OF mydds IS 17.------------------------------------------------ --------------------- 18. COMPONENT REG8B --load 'event and load = 1 --dout <= din; 19. PORT ( 20. LOAD : IN STD_LOGIC; 21. DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 22. DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); 23. END COMPONENT; 24.------------------------------------------------ --------------------- 25. COMPONENT ADDER8B 26. PORT ( 27. A : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 28. B : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 29. S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)) ; 30. END COMPONENT; 31.------------------------------------------------ --------------------- 32. COMPONENT lpm_rom8 33. PORT ( 34. address : IN STD_LOGIC_VECTOR(7 DOWN TO 0); 35. inclock : IN STD_LOGIC ; 36. q : OUT STD_LOGIC_VECTOR(7 DOW NTO 0)); 37. END COMPONENT; 38.------------------------------------------------ ----------------------- 39. SIGNAL F8B : STD_LOGIC_VECTOR( 7 DOWNTO 0); 40. SIGNAL A8B : STD_LOGIC_VECTOR( 7 DOWNTO 0); 41. SIGNAL B8B : STD_LOGIC_VECTOR( 7 DOWNTO 0); 42. SIGNAL C8B : STD_LOGIC_VECTOR( 7 DOWNTO 0); 43.------------------------------------------------ --------------------- 44.B EGIN 45. F8B<=FWORD; 第1章 绪论 1.1 DSP 简介 数字信号处理(Digital Signal Processing ,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。在过去的二十多年时间里,信号处理已经在通信等领域得到极为广泛的应用。 图一是数字信号处理系统的简化框图。此系统先将模拟信号转换为数字信号,经数字信号处理后,再转换成模拟信号输出。其中抗混叠滤波器的作用是将输入信号 x(t)中高于折叠频率的分量滤除,以防止信号频谱的混叠。随后,信号经采样和A/D 转换后,变成数字信号x(n)。数字信号处理器对x(n)进行处理,得到输出数字信号 y(n),经D/A 转换器变成模拟信号。此信号经低通滤波器,滤除不需要的高频分量, 最后输出平滑的模拟信号y(t)。 图1.1 数字信号处理系统简化框图 数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。近来新兴的一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分。可以说,数字信号处理是把许多经典的理论体系作为自己的理论基础,同时又使自己成为一系列新兴学科的理论基础。 抗混叠 滤波器 A/D 数字信号处理 D/A 低通滤波器 x(n) y(n) x(t) y(t) DDS基本原理及技术指南 2012年03月20日12:03 eechina 分享 关键词:DDS , 频率合成 随着数字技术在仪器仪表和通信系统中的广泛使用,可从参考频率源产生多个频率的数字控制方法诞生了,即直接数字频率合成(DDS)。其基本架构如图1所示。该简化模型采用一个稳定时钟来驱动存储正弦波(或其它任意波形)一个或多个整数周期的可编程只读存储器(PROM)。随着地址计数器逐步执行每个存储器位置,每个位置相应的信号数字幅度会驱动DAC,进而产生模拟输出信号。最终模拟输出信号的频谱纯度主要取决于DAC。相位噪声主要来自参考时钟。 DDS是一种采样数据系统,因此必须考虑所有与采样相关的问题,包括量化噪声、混叠、滤波等。例如,DAC 输出频率的高阶谐波会折回奈奎斯特带宽,因而不可滤波,而基于PLL的合成器的高阶谐波则可以滤波。此外,还有其它几种因素需要考虑,稍后将会讨论。 图1:直接数字频率合成系统的基本原理 这种简单DDS系统的基本问题在于,最终输出频率只能通过改变参考时钟频率或对PROM重新编程来实现,非常不灵活。实际DDS系统采用更加灵活有效的方式来实现这一功能,即采用名为数控振荡器(NCO)的数字硬件。图2所示为该系统的框图。 图2:灵活的DDS系统 系统的核心是相位累加器,其内容会在每个时钟周期更新。相位累加器每次更新时,存储在△相位寄存器中的数字字M就会累加至相位寄存器中的数字。假设△相位寄存器中的数字为00...01,相位累加器中的初始内容为00...00。相位累加器每个时钟周期都会按00...01更新。如果累加器为32位宽,则在相位累加器返回至00...00前需要232(超过40亿)个时钟周期,周期会不断重复。 相位累加器的截断输出用作正弦(或余弦)查找表的地址。查找表中的每个地址均对应正弦波的从0°到360°的一个相位点。查找表包括一个完整正弦波周期的相应数字幅度信息。(实际上,只需要90°的数据,因为两个MSB中包含了正交数据)。因此,查找表可将相位累加器的相位信息映射至数字幅度字,进而驱动DAC。图3用图形化的“相位轮”显示了这一情况。 考虑n = 32,M = 1的情况。相位累加器会逐步执行232个可能的输出中的每一个,直至溢出并重新开始。相应的输出正弦波频率等于输入时钟频率232分频。若M=2,相位累加器寄存器就会以两倍的速度“滚动”计算,输出频率也会增加一倍。以上内容可总结如下: 图3:数字相位轮 ORG 0000H KB:MOV P1,#0FFH;置P0口为输入方式MOV A,P1;读键值 CPL A ANL A,#1FH;屏蔽高三位 JZ KB;无键闭合继续检测 ACALL DL Y_10MS;延时10ms,去抖动MOV A,P1;再次检测有无键闭合 CPL A ANL A,#1FH JZ KB CJNE A,#01H,KB01 LCALL FANGBO;调用方波子程序SJMP KB KB01:CJNE A,#02H,KB02 LCALL JVCHI;调用锯齿波子程序SJMP KB KB02:CJNE A,#04H,KB03 LCALL TIXING;调用梯形波子程序SJMP KB KB03:CJNE A,#08H,KB04 LCALL SANJIAO;调用三角波子程序SJMP KB KB04:CJNE A,#10H,KB LCALL ZHENGXIAN;调用正弦波子程序SJMP KB ;方波子程序////////////// FANGBO: MOV DPTR,#0FFFEH LP1: MOV A,0 MOVX @DPTR,A LCALL DELAY1 MOV A,#0FFH MOVX @DPTR,A LCALL DELAY1 AJMP LP1 ;锯齿波子程序///////////// JVCHI: MOV DPTR,#0FFFEH MOV A,#0FFH WW:MOVX @DPTR,A DEC A NOP NOP NOP AJMP WW ;梯形波子程序 TIXING: MOV DPTR,#0FFFEH MOV R2,#07DH MOV R4,#0AFH MOV A,#00H D1:MOVX @DPTR,A LCALL DELAY2 ADD A,R2 DJNZ R4,D1 AJMP D1 ;三角波子程序/////////////// SANJIAO: MOV DPTR,#0FFFEH MOV R6,#10H MOV A,#00H LOOP1: MOVX @DPTR,A ADD A,R6 CJNE A,#0FFH,LOOP1 LOOP2: MOVX @DPTR,A SUBB A,R6 CJNE A,#07H,LOOP2 AJMP LOOP1 ;正弦波子程序///////////////// ZHENGXIAN: MOV R1,#00H QZ:MOV A,R1 MOV DPTR,#SETTAB MOVC A,@A+DPTR MOV DPTR,#0FFFEH MOVX @DPTR,A INC R1 AJMP QZ ;延时程序2 DELAY2:MOV 31H,#02H PW:DJNZ 31H,PW RET ;延时子程序1 DELAY1: MOV 30H,#0FFH 基于DSP设计正弦信号发生器 一.设计目的 设计一个基于DSP的正弦信号发生器 二.设计内容 利用基于CCS开发环境中的C54X汇编语言来实现正弦信号发生装置。三.设计原理 一般情况,产生正弦波的方法有两种:查表法和泰勒级数展开法。查表法是使用比较普遍的方法,优点是处理速度快,调频调相容易,精度高,但需要的存储器容量很大。泰勒级数展开法需要的存储单元少,具有稳定性好,算法简单,易于编程等优点,而且展开的级数越多,失真度就越小。本文采用了泰勒级数展开法。一个角度为θ的正弦和余弦函数,可以展开成泰勒级数,取其前5项进行近似得: 式中:x为θ的弧度值,x=2πf/fs(fs是采样频率;f是所要发生的信号频率。 正弦波的波形可以看作由无数点组成,这些点与x轴的每一个角度值相 对应,可以利用DSP处理器处理大量重复计算的优势来计算x轴每一点对应的y的值(在x轴取N个点进行逼近)。整个系统软件由主程序和基于泰勒展开法的SIN子程序组成,相应的软件流程图如图。 三.总体方案设计 本设计采用TMS320C54X系列的DSP作为正弦信号发生器的核心控制芯片。 通过计算一个角度的正弦值和余弦值程序可实现正弦波,其步骤如下: 1.利用sinx和cosx子程序,计算0°~45°(间隔为0.5°)的正弦和余弦值 2.利用sin(2x)=2sin(x)cos(x)公式,计算0°~90°的正弦值(间隔为1°) 3.通过复制,获得0°~359°的正弦值 4.将0°~359°的正弦值重复从PA口输出,便可得到正弦波 四.软件操作 DSP 集成开发环境 CCS是 Code Composer Studio 的缩写,即代码设计工作室。它是 TI 公司推出的集成可视化 DSP 软件开发工具。DSP CCS 内部集成了以下软件工具:◆ DSP 代码产生工具(包括 DSP 的 C 编译器、汇编优化器、汇编器和链接器)◆ CCS 集成开发环境(包括编辑、建立和调试 DSP 目标程序)◆ 实时基础软件 DSP/BIOS (必须具有硬件开发板)◆ RTDX、主机接口和 API(必须具有硬件开发板)在 CCS 下,用户可以对软件进行编辑、编译、调试、代码性能测试(profile)和项目管理等工作。CCS 可以提供如下功能:◆ 设置断点◆ 在断点处自动修改窗口◆ 观察变量◆ 观察和编辑存储器和寄存器◆ 利用测试点使数据流在目标系统和文件之间流动◆ 观察调用堆栈◆ 观察图形信号◆ 代码性能测试(profiling)◆ 观察反汇编和 C 指令执行◆ 提供 GEL (通用扩展语言)语言。此语言能增加一个函数或功能到 CCS 菜单中来完成用户自己设定的任务,是扩展 CCS 功能的专用语言。使用 CCS,可以加速 DSP 的开发进程,是 DSP 开发应用的得力助手。这里以 C54x DSP 的 CCS 3.1 为例介绍正弦波的产生。 利用 CCS 集成开发环境,用户可以在一个开发环境下完成工程定义、程序编辑、编译链接、调试和数据分析等工作环节。 1.创建工程(project)文件 选择Project→New,在“Project”文本框中键入将要创建的工程项目名,本例工程项目名为“sin” 电磁无损检测中信号发生器的设计与实 现 [日期:2005-6-24] 来源:国外电子元器件作者:彭国标 [字体:大中 小] 摘要:在电磁无损检测系统中,信号频率及其稳定性对检测效果影响很大,为了解决该难题,文中给出了一种应用DDS技术设计的新型信号发生器解决方案。该信号发生器具有频率精度高、稳定性好、分辨率高的特点,有利于提高电磁无损检测的效果。 关键词:电磁无损检测;信号发生器;直接数字频率合成 电磁无损检测(如涡流)是基于电磁感应原理的无损检测技术。当载有交变电流的检测线圈靠近导体时,由于交变电流在周围空间中会产生交变磁场,因而在被测试件(导体)表面产生趋肤效应并感应出交变电流。通过优化设计可使被测试件表面电流达到均匀分布,从而使周围磁场也达到均匀,而当被测试件表面有缺陷时,电流就会发生畸变,均匀磁场随之发生变化,这样,直接或间接测量出该磁场的变化,就能检测试件的缺陷。虽然人们在电磁无损检测方面已取得了许多进展,但仍有许多不尽人意之处,其中一个重要的因素便是检测系统信号的稳定性,这一点对测量结果会产生严重的影响。因为信号发生电路是整个检测系统的信号源,它的信号频率是否稳定将对整个检测系统的工作起十分关键的作用,信号频率不稳定会给信号的后续处理带来极大的困难,甚至使电磁检测难以进行。为了解决上述问题,笔者应用DDS技术设计了一个高稳定性信号发生器。 1DDS的工作原理 直接数字合成(DDS-DirectDigitalSynthesizer)是近几年发展起来的一种新的频率/波形合成技术。该技术具有频率分辨率高、转换速度快、信号纯度高、相位可控、输出信号无电流脉冲叠加、输出可平稳过渡且相位保持连续变化等优点。近年来在通讯、雷达、GPS、蜂窝基站、图像处理及HDTV等领域得到了广泛应用。 单片机控制DAC0832输出正弦波三角波汇 编程序 org 0000h LJMP MAIN ORG 0003H LJMP L0 MAIN:MOV R2,#0aH ;调幅倍数 MOV R4,#01H ;增减选择 MOV R5,#01H pp: SETB EA SETB EX0 ;延时计数个数 MOV A,#0FFH ;读取波形状态 MOV P1,A MOV A,P1 JNB ACC.0,ZXB ;P1.0=0 则选择正弦波 JNB ACC.1,SJB ;P1.1=0 则选择三角波 JNB ACC.2,FB ;P1.2=0 则选择方波 AJMP PP ZXB:MOV R1,#00H . LOOP1:MOV A,R1 MOV DPTR,#TABLE1 ;读取正弦波数据首地址 MOVC A,A+DPTR ;去表格数据 MOV B,R2 MUL AB ;幅度大小 INC R1 XCH A,R1 CLR C SUBB A,#0AH ;是否已采样半个周期 JNC LK1 ;C=0跳转,即R1大于0A,以采样半个周期以上 ADD A,#0AH XCH A,R1 ;还原R1 ADD A,#80H ;8OH为零点,取得正的幅度值 AJMP LK0 LK1:ADD A,#0AH XCH A,R1 MOV R3,A MOV A,#80H CLR C . SUBB A,R3 ;80H为零点,取得负的幅度值LK0:MOV DPTR,#8000H ;送DA转换入口地址 MOVX DPTR,A MOV A,R5 KD:DEC R5 ;调用延时 CALL DELAY CJNE R5,#00H,KD MOV R5,A CJNE R1,#12H,LOOP1 LJMP PP FB:MOV R1,#00H LOOP2:MOV A,R1 MOV DPTR,#TABLE2 ;读取方波数据首地址 MOVC A,A+DPTR ;去表格数据 MOV B,R2 MUL AB ;幅度大小 INC R1 XCH A,R1 CLR C SUBB A,#0AH ;是否已采样半个周期 . 2 基本原理 2.1 直接数字频率合成器 直接数字合成(Direct Digital Synthesis,简称DDS)技术是从相位概念出发,直接对参考正弦信号进行抽样,得到不同的相位,通过数字计算技术产生对应的电压幅度,最后滤波平滑输出所需频率。 2.1.1 DDS工作原理 下面,通过从相位出发的正弦函数产生描述DDS的概念。 图1表示了半径R为1的单位圆,半径R绕圆心旋转与X轴的正方向形成夹角θ(t),即相位角。 图1 单位圆表示正弦函数S= R sinθ(t) DDS的原理框图如图2所示。图中相位累加器可在每一个时钟周期来临时将频率控制字(FTW)所决定的相位增量M累加一次,如果记数大于2N,则自动溢出,而只保留后面的N位数字于累加器中[9]。 图2 DDS原理框图 DDS的数学模型可归结为:在每一个时钟周期T c 内,频率控制字M与N比特相位累加器累加一次,并同时对2N取模运算,得到的和(以N位二进制数表示)作为相位值,以二进制代码的形式去查询正弦函数表ROM,将相位信息转变成相应的数字量化正弦幅度值,ROM输出的数字正弦波序列再经数模转换器转变为阶梯模拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号。 由于ROM表的规模有限,相位累加器一般仅取高位作为寻址地址送入正弦查询表获得波形幅度值。正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。 2.1.2 DDS的结构 DDS的基本结构包括相位累加器、正弦查询表(ROM)、数模转换器(DAC)和低通滤波器(LPF),其中从频率控制字到波形查询表实现由数字频率值输入生成相应频率的数字波形,其工作过程为: ⑴确定频率控制字M; ⑵在时钟脉冲f c 的控制下,该频率控制字累加至相位累加器生成实时数字相位值; ⑶将相位值寻址ROM转换成正弦表中相应的数字幅码。 模块DAC实现将数字幅度值高速且线性地转变为模拟幅度值,DDS产生的混叠干扰由DAC之后的低通滤波器滤除]7[。 ㈠相位累加器 相位累加器是DDS最基本的组成部分,用于实现相位的累加并存储其累加结果。 若当前相位累加器的值为Σ n ,经过一个时钟周期后变为Σ 1+ n ,则满足 Σ 1+ n =Σ n +M Σ n 为一等差数列,不难得出:Σ n =nM+Σ 其中Σ 为相位累加器的初始相位值。 ㈡正弦查询表(ROM) DDS查询表所存储的数据是每一个相位所对应的二进制数字正弦幅值,在每一个时钟周期内,相位累加器输出序列的高m位对其进行寻址,最后的输出为该相位相对应的二进制正弦幅值序列。 ㈢数模转换器(DAC) 数模转换器的作用是将数字形式的波形幅值转换成所要求合成频率的模拟形式 本科生实验报告 实验名称:数模转换器DAC0832双缓冲输出设计 一、实验目的 1)了解DAC0832芯片引脚、内部结构及工作原理; 2)掌握应用单片机I/O 端口控制DAC0832实现数模转换的方法; 3)掌握DAC0832单缓冲和双缓冲控制技术及编程设计方法; 二、实验原理 DAC0832是8位分辨率的数模转换集成芯片,内部采用倒T 形网络,电流型 输出模式,电流输出稳定时间为1us ,采用单电源供电。 片内部由一个8位输入锁存器、一个8位DAC 寄存器和一个8位D/A 转换器构成,内部具有双缓冲结构,可以实现单缓冲、双缓冲数字输入。 双缓冲同步控制方式 : 针对多个模拟量需要同时输出的控制系统,可以采用双缓冲同步控制方式。D/A 转换数据的输入锁存和D/A 转换输出分两步完成。首先,CPU 分时向各路D/A 转换器输入要转换的数字量并锁存在各自的输入锁存器中,然后,CPU 同时对所有D/A 转换器发出输入所存数据打入DAC 寄存器的控制信号,即可实现 VREF IOUT2 IOUT1 DGND VCC AGND RFB 多通道的同步模拟量数据输出。 应用双缓冲方式,可以在输出模拟信号的同时采集下一个数字量,有效地提高转换速度。另外,可以在多个D/A转换器同时工作时,利用双缓冲模式实现多路D/A的同步输出。 三、实验内容 通过单片机I/O端口控制两路DAC0832实现数模转换,控制方式采用双缓冲控制方式。 1.阅读理解双缓冲控制电路图,分析双缓冲模式下DAC0832与单片机接口电路的设计及两次DA转换实验在控制电路上的异同。 2.设计程序,实现双缓冲模式下DA转换的同步输出。 首先,CPU分时向各路D/A转换器输入要转换的数字量并锁存在各自的输入锁存器中,然后,通过按键控制,同时对两个DAC0832锁存数据进行数模转换,同步产生三角波、正弦波模拟输出信号。 四、实验过程 1,实验原理图 2,实验源程序 #include 基于DSP的信号发生器设计设计题目:正弦信号发生器 专业班级电科11级-1班 学号 311108001417 学生姓名王博 指导教师王科平 摘要 正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。 目前,常用的信号发生器绝大部分是由模拟电路构成的,当这种模拟信号发生器用于低频信号输出往往需要的RC值很大,这样不但参数准确度难以保证,而且体积大和功耗都很大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,价格较贵,而本文借助DSP运算速度高,系统集成度强的优势设计的这种信号发生器,比以前的数字式信号发生器具有速度更快,且实现更加简便。正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。 目前,常用的信号发生器绝大部分是由模拟电路构成的,当这种模拟信号发生器用于低频信号输出往往需要的RC值很大,这样不但参数准确度难以保证,而且体积大和功耗都很大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,价格较贵,而本文借助DSP运算速度高,系统集成度强的优势设计的这种信号发生器,比以前的数字式信号发生器具有速度更快,且实现更加简便。 目录 一、概述 (3) 二、系统设计 (4) 2.1 总体方案 (4) 2.2正弦波信号发生器 (4) 三、硬件设计 (5) 3.1硬件组成部分 (5) 3.2控制器部分 (6) 3.4人机接口部分 (7) 四、软件设计 (8) 4.1流程图 (8) 4.2 正弦信号发生器程序清单 (9) 五、总结 (14) 参考文献 (14) DDS原理及AD9851电路设计、测试 鼎峰电子https://www.sodocs.net/doc/149552396.html, 一.DDS(Direct Digital Synthesis)直接频率合成技术概况在频率合成(FS, Frequency Synthesis)领域中,常用的频率合成技术有模拟锁相环、数字锁相环、小数分频锁相环(fractional-N PLL Synthesis)等,直接数字合成(Direct Digital Synthesis-DDS)是近年来新的FS技术。单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。DDS是产生高精度、快速变换频率、输出波形失真小的优先选用技术。DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波经过一个模拟滤波器后,得到最终的模拟信号波形。如图2所示,通过高速DAC产生数字正弦数字波形,通过带通滤波器后得到一个对应的模拟正弦波信号,最后该模拟正弦波与一门限进行比较得到方波时钟信号。 DDS系统一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。除此之外,DDS的固有特性还包括:相当好的频率和相位分辨率(频率的可控范围达μHz级,相位控制小于0.09°),能够进行快速的信号变换(输出DAC的转换速率300百万次/秒)。这些特性使DDS在军事雷达和通信系统中应用日益广泛。 其实,以前DDS价格昂贵、功耗大(以前的功耗达Watt级)、DAC器件转换速率不高,应用受到限制,因此只用于高端设备和军事上。随着数字技术和半导体工业的发展,DDS芯片能集成包括高速DAC器件在内的部件,其功耗降低到mW级(AD9851在3.3v 时功耗为650mW),功能增加了,价格便宜。因此,DDS也获得广泛的应用:现代电子器件、通信技术、医学成像、无线、PCS/PCN系统、雷达、卫星通信。 智能仪器课程设计 设计题目:函数信号发生器设计 学生姓名:赵鑫、罗承波、江再农 学院名称:机械工程学院 班级:测控技术与仪器062班 学号:200646000227、20064600222、20064600215 指导教师:袁锋伟、王玉林、蒋彦 2009年6月 设计任务: 设计一个函数信号发生器,具体指标如下: 1采用AT89S51及DAC0832设计函数信号发生器; 2输出函数信号为正弦波或三角波或阶梯波; 3输出信号频率为100Hz,幅度0-10V可调; 4必须具有信号输出及外接电源、公共地线接口 低频函数信号发生器的设计 摘要:信号发生器是一种常用的信号源,广泛地应用于电子电路、自动控制系统和教学实验等领域。目前使用的信号发生器大部分是利用分立元件组成的体积大,可靠性差,准确度低。课程设计需要各个波形的基本输出,这些波形的实现的具体步骤:正弦波的实现是非常麻烦的。它的实现过程是通过定义一些数据,然后执行时直接输出定义的数据就可以了。而三角波,则每次累加1,当达到初值时,每次累减1,算出延时时间,也就达到要求了,阶梯波和三角波类似!该设计使用的是AT89S51单片机构成的发生器,可产生三角波、方波、正弦波等多种波形,波形的频率可用程序控制改变。在单片机上加外围器件独立式开关,通过开关控制波形的选择。在单片机的输出端口接DAC0832进行DA转换,再通过运放进行波形调整,最后输出波形接在示波器上显示。 关键词:信号发生器;单片机;波形调整 The design of low-frequency function signal-generator Abstract:Signal generator is a common signal source, widely used in electronic circuits, automatic control systems and experiments in areas such as teaching. Currently used by most of the signal generator is composed of discrete components use bulky, poor reliability, low accuracy. Curriculum design of the basic needs of all the output waveform, the waveform of the specific steps to achieve: the realization of sine wave is very troublesome. It is through the implementation of the definition of some data, and then direct the output when the definition of the implementation of the data on it. The triangle wave, then add 1 each time, when the initial value to reach every tired by 1, calculate the delay time, they meet the requirement, the ladder-wave and triangular wave similar! The design is composed of single-chip AT89S51 generator can produce the triangular wave, square wave, sine wave, etc., 第1章绪论 1.1 DSP简介 数字信号处理(Digital Signal Processing,简称DSP>是一门涉及许多学科而又广泛应用于许多领域地新兴学科.20世纪60年代以来,随着计算机和信息技术地飞速发展,数字信号处理技术应运而生并得到迅速地发展.数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号地方法,这些信号由数字序列表示.在过去地二十多年时间里,信号处理已经在通信等领域得到极为广泛地应用. ,经 x(t>,信号经采样和A/D 转换后,得到输出数字信号y(n>,, 图1.1数字信号处理系统简化框图 数字信号处理是以众多学科为理论基础地,它所涉及地范围极其广泛.例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理地基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关.近来新兴地一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分.可以说,数字信号处理是把许多经典地理论体系作为自己地理论基础,同时又使自己成为一系列新兴学科地理论基础. 1.2 课题来源 数字信号处理器(DSP>是在模拟信号变成数字信号以后进行高速实时处理地专用处理器.DSP芯片以其独特地结构和快速实现各种数字信号处理算法地突出优点,发展十分迅速.数字信号发生器是在电子电路设计、自动控制系统和仪表测量校正调试中应用很多地一种信号发生装置和信号源.而正弦信号是一种频率成分最为单一地常见信号源,任何复杂信号(例如声音信号>都可以通过傅里叶变换分解为许多频率不同、幅度不等地正弦信号地叠加,广泛地应用在电子技术实验、自动控制系统和通 DDS的原理及镜像频谱分析 1.目的: (1)了解DDS的原理。 (2)分析DDS的镜像频谱 2.DDS的原理 2.1.DDS的概述 直接数字式频率综合器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字对系统时钟进行分频以产生所需要的频率。DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit或者更高),频率分辨率高。 图1是DDS的内部结构图,它主要分成3部分:相位累加器(PHASE_ACCMULATOR),相位幅度转换(AMPLITUDE/SINE_CONV.ALGORITHM),数模转换器(D/A_CONVERTER) 图1 DDS的结构框图 2.2.DDS的组成 1、相位累加器:一个正弦波,它的幅度不是线性的,但是它的相位却是线性增加的。DDS就是 利用了这一特点来产生正弦信号。如图 2,根据DDS的频率控制字的位数N,把 360°平均分成了2N等份。假设系统时钟为Fc,输出频率为Fout。每次转动一个 角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。那么只要 选择恰当的频率控制字M,使得Fout/Fc= M/2N,就可以得到所需要的输出频率 Fout=Fc*M /2N。 图2 相位累加器原理 2、相位幅度转换:通过相位累加器,我们已经得到了合成Fout频率所对应的相位信息,然后相 位幅度转换器把0°~360°的相位转换成相位相应的幅度值。比如当DDS选 择为2Vp-p的输出时,45°对应的幅度值为 0.707V,这个数值则以二进制的 形式被送入DAC。这个相位到幅度的转换是通过查表完成的。 3、数模转换器:的二进制数字信号被送入DAC中,并转换成为模拟信号输出。★注意★DAC 的 位数并不影响输出频率的分辨率。输出频率的分辨率是由频率控制字的位数决 定的。 3. DDS的镜像频谱分析: 我们已经知道DDS是一个分频器,在提供一个系统主频的情况下,能够输出低于系统主频,分辨率为2N的正弦波。即每一个主频周期,DAC都会输出一个点,而2N/M个点形成输出频率的一个周期。这就相当于以系统时钟的频率对输出时钟进行采样,根据奈奎斯特定律,这就是为什么输出频率要低于系统时钟的50%的原因。 下图3为DDS在300M主频,输出80M频率时的频谱。图4为AD9954(主频为400M)输出80M 频率时的频谱(无参考时钟倍频器)。 单片机控制DAC0832 输出正弦波三角 波 汇编程序 org 0000h LJMP MAIN ORG 0003H LJMP L0 MAIN:MOV R2,#0aH MOV R4,#01H MOV R5,#01H pp: SETB EA SETB EX0 MOV A,#0FFH MOV P1,A MOV A,P1 JNB ACC.0,ZXB JNB ACC.1,SJB JNB ACC.2,FB AJMP PP ZXB:MOV R1,#00H LOOP1:MOV A,R1 ;调幅倍数 ;增减选择 ;延时计数个数 ;读取波形状 态 ;P1.0=0 则选择正弦 波 ;P1.1=0 则选择三角波 ;P1.2=0 则选择方波 MOV DPTR,#TABLE1 ;读取正弦波数据首地址 MOVC A,@A+DPTR ;去表格数据 MOV B,R2 MUL AB ;幅度大小 INC R1 XCH A,R1 CLR C SUBB A,#0AH ;是否已采样半个周期 JNC LK1 ;C=0 跳转,即R1 大于0A,以采样半个周期以上 ADD A,#0AH XCH A,R1 ;还原R1 ADD A,#80H ;8OH 为零点,取得正的幅度值 AJMP LK0 LK1:ADD A,#0AH XCH A,R1 MOV R3,A MOV A,#80H CLR C SUBB A,R3 ;80H 为零点,取得负的幅度值LK0:MOV DPTR,#8000H ;送DA 转换入口地址MOVX @DPTR,A MOV A,R5 KD:DEC R5 ;调用延时 CALL DELAY CJNE R5,#00H,KD MOV R5,A CJNE R1,#12H,LOOP1 LJMP PP FB:MOV R1,#00H LOOP2:MOV A,R1 MOV DPTR,#TABLE2 ;读取方波数据首地址 MOVC A,@A+DPTR ;去表格数据 MOV B,R2 MUL AB ;幅度大小 INC R1 基于Matlab/DSP Builder的正弦信号发生器设计 引言 近年来随着通信技术的不断发展,信号的正确传输显得日益重要,也就是说要有一个可靠的能产生稳定确信号的发生器,基于Matlab/DSP Builder的正弦信号发生器是利用Matlab/DSP Builder的模块进行的模快化设计,软件的设计采用模块化结构,使程序设计的逻辑关系更加简洁明了、易懂、易学。使硬件在软件的控制下协调运作。 DSP Builder可以帮助设计者完成基于FPGA的DSP系统设计设计,除了图形化的系统建模外,还可以完成及大部分的设计过程和仿真,直至将设计文件下载到DSP 开发板上。此次实验的目的就是将两者的优势有机的结合在一起,利用DSP的优势开发正弦信号发生器。 在设计中主要采用DSP Builder库中的模块进行系统的模型设计,然后再进行Simulink仿真。 1.设计思想 1.1 DSP Builder特点 DSP Builder系统级(或算法级设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模和RTL(硬件实现两个领域的设计工具连接起来,最大程度的发挥了两种工具的优势。DSP Builder依赖于MathWorks公司的数学分析工具 Matlab/Simulink,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compilder把Matlab/Simulink的设计文件(.mdl转换成相应的硬件描述语言VHDL 设计文件(.vhd,以及用于控制和编译的tcl脚本。而对后者的处理可以用Quartus II 来实现。 1.2 QuartusII特点 DDS波形发生器电路组成及功能 、DDS波形发生器电路的组成 本系统以单片机STC89C52为核心,采用了直接数字合成技术(DDS),实现了频 率任意调节的正弦波,方波,三角波以及特定的任意信号,产生的各类波形精度高,稳定性好,采用友好的人机界面,操作方便。系统总框图如下图所示: (1)相位累加地址发生器 使用可编程逻辑器件IC4 GAL16V8编程得到累加相位码,也就是波形的地址码。这里的GAL16V8是100进制计数器,相位累加时,对应一个波形100个数据的地址。 GAL16V8拥有8个输入端和8个输出端,可以单独选择每个输出端的极性,灵活的进行输出端的组合排列、可重复编程、频带范围宽,工作频率很高。使用GAL16V8做相位累加地址发生器使得电路更加简洁,保证在高频率下的稳定工作。 (2)数据存储器 使用外部ROM数据存储器IC5 27C64,已经预先把相关波形的量化数据写入该外部ROM中。 (3)D/A模数转换电路 使用数模转换集成芯片IC6 DAC0832,DAC0832是一个8位的电流式的数模转换器,就是把波形数据转化为波形真实的模拟信号。波形信号为电流信号,因此输出端还要接运算放大器,把电流信号转换为电压信号。 (4)双极性转换电路及滤波电路 可 编 程 .M 来 信 号 信 号 報 动 输 出 DDS波形发生器系统框图 采用反相比例运算放大电路IC7 TL084 中的A,B 运放,将D/A 输出的单极性信号转 换为双极性信号。 为确保产生波形的质量,减少波形失真度,使输出波形光滑,须用低通滤波器把高频分量滤掉。在此采用自动线性跟踪Butterworth 有源滤波器,在此采用二阶有源低通滤波器,即TL084 中的 C 运放及R19,C18,R20,C10 两节低通滤波器组成。 (5)显示及控制电路 本机器需要进行人机对话,根据系统设计要求,采用独立式微动按钮S2?7输入,八只七段LED1?8数码管作为输出显示,清晰可见。使用时可以选择方波、三角波和正弦波三种波形的输出;可调节不同波形的输出频率,并实现了1Hz 的频率步进。 (6)单片机电路 单片机电路是DDS 波形发生器的核心电路,它由微处理器IC12 AT89S52 及外围电路、元器件等组成。它由P0和P1共16个端口与显示电路相连接,把各种的输出波形的相关数据送到八只七段LED i?8数码管显示。 还与可编程逻辑器件IC4 ,外部ROM 数据存储器IC5 相连接,提供可编程基准信号:使用单片机定时器产生固定频率,波形稳定,为相位累加地址发生器提供基准信号。 另外由P2.0?P2.5接键盘的6只微动按钮S2?7,作控制输出信号之用。 微处理器IC12已经按功能要求,把相关的程序写入到芯片中。 (7)电源电路 本系统中,许多集成电路,如单片机、D/A 电路、运算放大器等都需要直流电源进行供电才能工作。单片机、EEPROM等都以5V电源供电,而运算放大器需要±2V供电,因此在电源板的设计过程中,要同时获得+5V、±2V的直流电压。LM7812输出电压为 +12V,LM7912输出电压为-12V,LM7805输出电压为+5V,三者的性能都能满足 设计要求。 在具体电路中,由市电AC220V经变压器降压为双AC12V后,接入到经由二极管VD3 组成的单相全波整流电桥整流,由电容器C8?11滤波后一路电压经过三端稳压器 ?6 LM7912稳压后输出+12V,另一路电压经过三端稳压器LMC7912稳压后输出-12V电压。 ±2V电压作为模拟放大器的电源电压,电容器C12?17是滤波电容。其中+12V电压经三端稳压器LM7805 稳压后输出+5V 电压,作为AT89S51、CAL16V8、27C64、URL2803、DAC0832、74LS244等数字集成电路的电源电压。考虑到D/A转换器在进行数模转换时,需要较稳定、精度较高的参考电压,在电源板设计过程中,将LM7812输出的+12V电 调试时,电源的质量需要较高,不然的话,波形不易观察看清楚。 //河北工程大学信电学院自动化系 //设计调试成功 ***************将DA输出的 0V ~ -5V范围扩展成 -5V ~ +5V范围,电路如下图:*************** 如若VO2输出更平滑一些,可以在VO2处接一个小电容,滤掉高频。 (一)过程分析计算如下: ?第一级运放出来的V o1=-N*V ref/256。当V ref为+5V时,V o1=0~ -5V。 其中,V ref为参考电压,N为8位数字量输出到DAC0832 ?并结合第二级运放,是否可以推出来如下式子: V o2=-(2*V o1+V ref)=-(2*-N*V ref/256+V ref) =-(-2N*V ref/256+V ref) =2N*V ref/256-V ref 当参考电压V ref=5V时,V o2=10N/256-5。 由于要求输出的是正弦波xsinθ,幅值x不定,下面考虑幅值x分别取5和1的情况: ●当输出波形为5 sinθ时:5 sinθ=V o2 =2N*V ref/256-V ref =10N/256-5 //此时V ref=+5V 得sinθ=2N/256-1 ●当输出波形为sinθ时:sinθ=V o2 =2N*V ref/256-V ref =10N/256-5 //此时V ref=+5V 得sinθ=10N/256-5 最后可以考虑输出波形的频率问题。例如要求输出特定频率的正弦波。 (二)针对输出的不同幅值波形 ?当输出波形为5 sinθ时:得sinθ=2N/256-1 这里我们要求进步为一度。具体到进步大小,和内存RAM或者ROM有关,即和你存放数据表的空间有关。放到哪个空间都可以。(这里周期采样最多256个点,步数可以为1、2、5等,自己视情况而定,这里由于是360度,256个采样点,故步的大小360/256=1.4=△θ,由此算的前三个 θ=0,1.4,2.8……,对应N为0x80,0x83,0x86……) 通过sinθ的特征和计算部分数据发现规律: 0~90度与90~180度大小是对称的;181~270度与270~359度是对称的。 故,不是所有数据都是计算的。 DDS介绍(自己整理) DDS概要 1971年,美国学者J.Tierney等人撰写的“A DIGITAL Frequency Synthesizer”-文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新给成原理。限于当时的技术和器件产,它的性牟指标尚不能与已有的技术盯比,故未受到重视。近1年间,随着微电子技术的迅速发展,直接数字频率合成器(Direct DIGITAL Frequency Synthesis简称DDS或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。 一、 DDS原理和结构 DDS的基本大批量是利用采样定量,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理可用图1来表示。 相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位加累加。由此可以看出,相位累加器在每一个中输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的出频率就是DDS输出的信号频率。 用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址。这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。 DDS在相对带宽、频率转换时间、高分头放力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。 下面以AD9850为例来谈一谈DDS的工作原理。DDS系统的核心是相位累加器,每来一个时钟脉冲,它的内容就更新一次。在每次更新时,相位增量寄存器的相位增量M就加到相位累加器中的相位累加值上。假设相位增量寄存器的M为00...01,相位累加器的初值为00...00。这时在每个时钟周期,相位累加器都要加上00...01。如果累加器位宽n是32位,相位累加器就需要232个时钟周期才能恢复初值(见图2)。 相位累加器的输出作为正弦查找表的查找地址。查找表中的每个地址代表一个周期的正基于DSP的正弦波信号发生器

DDS基本原理及技术指南

DAC0832的波形发生器(汇编)

基于DSP设计正弦信号发生器

dds工作原理

单片机控制dac0832输出正弦波三角波汇编程序

DDS信号发生器原理

微机原理及其应用报告数模转换器DAC0832双缓冲输出设计

基于DSP的信号发生器设计..

DDS原理及AD9851电路设计、测试

dac0832函数信号发生器.

DSP正弦波信号发生器

DDS的原理及镜像频谱分析

单片机控制DAC0832输出正弦波三角波汇编程序

基于Matlab_DSPBuilder的正弦信号发生器设计.

DDS波形发生器电路原理及功能

单片机制作简易正弦波信号发生器(DAC0832)

DDS介绍