用CD4046 组成的高倍锁相倍频器

-36-

《国外电子元器件》1998年第2期1998年2月

●新特器件应用

用CD4046组成的高倍锁相倍频器

电子工业部第22研究所

孙广俊张景伟

摘要:本文介绍了锁相环集成电路CD4046的内部结构功能及特点,并给出在高倍锁相倍频器中的应用。

关键词:锁相环锁相倍频

压控振荡

分频

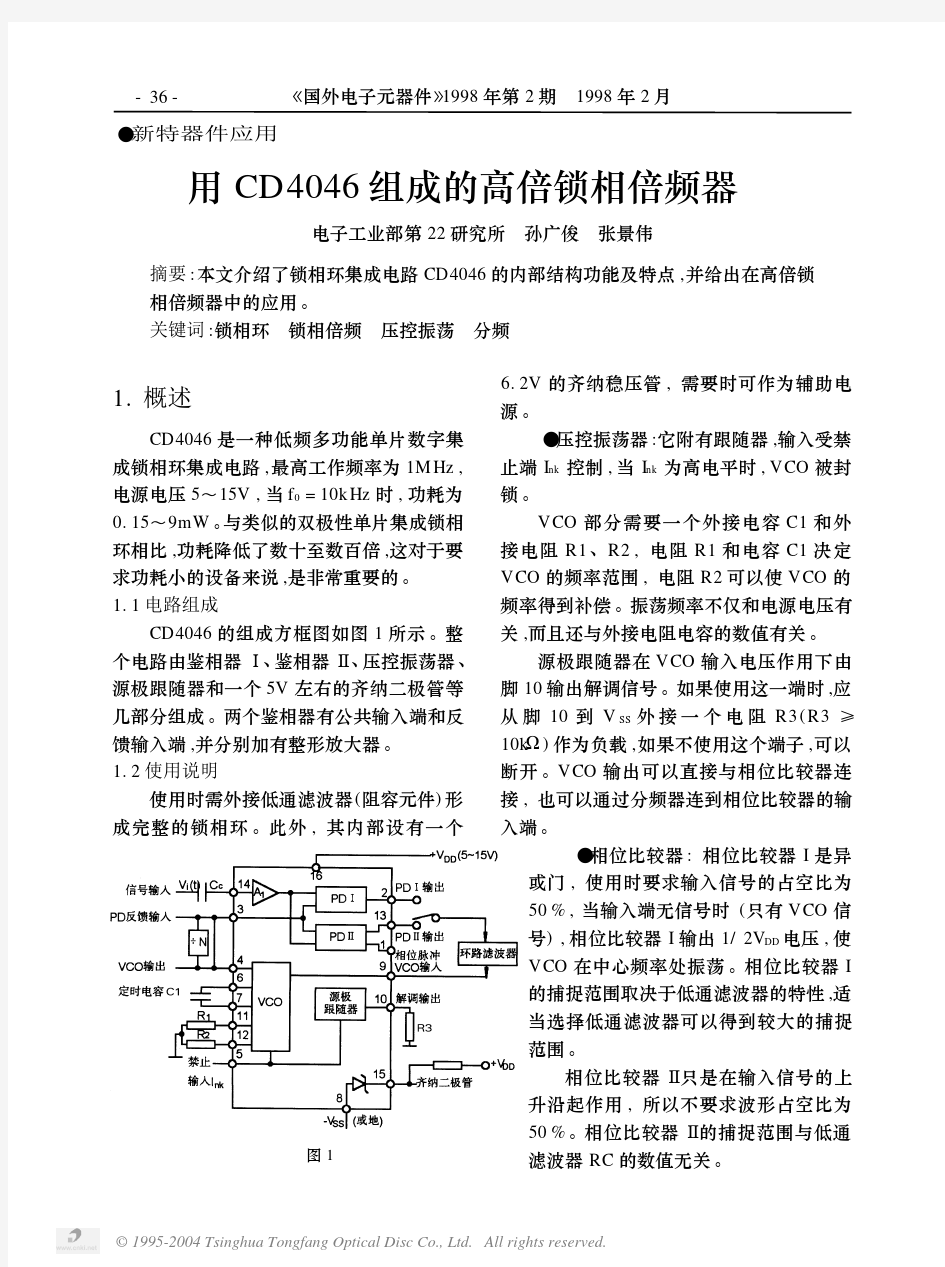

图1

1.概述

CD4046是一种低频多功能单片数字集

成锁相环集成电路,最高工作频率为1M Hz ,电源电压5~15V ,当f 0=10k Hz 时,功耗为

0.15~9mW 。与类似的双极性单片集成锁相

环相比,功耗降低了数十至数百倍,这对于要求功耗小的设备来说,是非常重要的。1.1电路组成

CD4046的组成方框图如图1所示。整个电路由鉴相器Ⅰ、鉴相器Ⅱ、压控振荡器、源极跟随器和一个5V 左右的齐纳二极管等几部分组成。两个鉴相器有公共输入端和反馈输入端,并分别加有整形放大器。1.2使用说明

使用时需外接低通滤波器(阻容元件)形成完整的锁相环。此外,其内部设有一个

6.2V 的齐纳稳压管,需要时可作为辅助电

源。

●压控振荡器:它附有跟随器,输入受禁止端I nk 控制,当I nk 为高电平时,VCO 被封锁。

VCO 部分需要一个外接电容C1和外

接电阻R1、R2,电阻R1和电容C1决定VCO 的频率范围,电阻R2可以使VCO 的频率得到补偿。振荡频率不仅和电源电压有关,而且还与外接电阻电容的数值有关。源极跟随器在VCO 输入电压作用下由脚10输出解调信号。如果使用这一端时,应从脚10到V SS 外接一个电阻R3(R3≥10k Ω)作为负载,如果不使用这个端子,可以断开。VCO 输出可以直接与相位比较器连接,也可以通过分频器连到相位比较器的输入端。

●相位比较器:相位比较器I 是异或门,使用时要求输入信号的占空比为50%,当输入端无信号时(只有VCO 信号),相位比较器I 输出1/2V DD 电压,使VCO 在中心频率处振荡。相位比较器I 的捕捉范围取决于低通滤波器的特性,适当选择低通滤波器可以得到较大的捕捉范围。

相位比较器Ⅱ只是在输入信号的上升沿起作用,所以不要求波形占空比为50%。相位比较器Ⅱ的捕捉范围与低通滤波器RC 的数值无关

。

-37-

2.应用实例

图2给出CD4046集成锁相环路在脉宽测量装置中作为锁相倍频器的应用实例,这是一个64倍锁相倍频器。

电路中,D 3是一个累加器,D 4是一个八输入与非门。由D 3、D 4、D2:2、D 5、D6实

现64分频功能,工作过程如下:当加到

D3的CL K 端来的输入脉冲个数达到128个时,使其输出端Q 1~Q 7的电平全为1,即D4的1、2、3、4、5、6、11脚的电平全为高电平,这样就使D4的输出端变为0,使D ∶2的SD 端变为低电平,D2的输出Q 变为低电平,从而使D3复位,准备新的一次倍频过程。

信号经过D2∶1(D 型触发器)进行

2分频以保证信号占空比为50%,满足锁

相环对信号占空比的要求。

从图2中还可以看出,只要将这一电路稍加改变就可以做成64倍频以下的多种倍频器。当然,如果将D3的Q 1~

Q 12全部利用上,可以做成更高倍的锁

相倍频器,因此该电路具有一定的代表性与通用性。参考文献

1.张风言、王建刚编著,《模拟集成电路及应用》,中国铁道出版社。

2.吴纯国等编著,《数字集成电路与逻辑技术》,黑龙江科学技术出版社。

咨询编号

:980210

用CD4046组成的高倍锁相倍频器

图2用CD4046组成的64

倍频锁相环

●元器件卡片

四通道256阶数字电位器SM2581

图1SM2581管脚排列图

SM 2581是一种全集成固态数字电位

器,与传统的模拟电位器的工作原理、外形、结构完全不同,它取消了活动件,克服了模拟电位器的主要缺点。

SM 2581有如下特点:

●内含四个电阻通道,分别作为四个可调电位器;

●根据后缀不同,可变阻值范围有10k Ω、50k Ω、100k Ω三种;

●每个电阻通道有256个滑臂阻值定位点,可用微处理器进行编程控制,也可手动控制;

(下转45页)

锁相环pll工作原理及verilog代码

锁相环的组成和工作原理 #1 1.锁相环的基本组成 . 许多电子设备要正常工作, 通常需要外部的输入信号与内部的振荡信 许多电子设备要正常工作, 号同步,利用锁相环路就可以实现这个目的。 号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路, 锁相环路是一种反馈控制电路,简称锁相环 )。锁相环的特点是 (PLL)。锁相环的特点是:利用外部输入的 )。锁相环的特点是: 参考信号控制环路内部振荡信号的频率和相 位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 相环通常用于闭环跟踪电路。锁相环在工作的过程中, 相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出 于闭环跟踪电路 信号的频率与输入信号的频率相等时, 信号的频率与输入信号的频率相等时,输出电压与输入电压保 持固定的相位差值,即输出电压与输入电压的相位被锁住,这 持固定的相位差值,即输出电压与输入电压的相位被锁住, 就是锁相环名称的由来。 就是锁相环名称的由来。 ( ) 锁相环通常由鉴相器 PD) 环路滤波器 LF) 、 ( ) 和压控振荡器 VCO) ( ) 三部分组成, 所示。 三部分组成,锁相环组成的原理框图如图 8-4-1 所示。 锁相环中的鉴相器又称为相位比较器, 它的作用是检测输入信号和输 锁相环中的鉴相器又称为相位比较器, 出信号的相位差,并将检测出的相位差信号转换成 uD(t)电压信号 出信号的相位差, ) 输出, 该信号经低通滤波器滤波后形成压控振荡器的控制电压 u(t) 输出, , C ) 对振荡器输出信号的频率实施控制。 对振荡器输出信号的频率实施控制。 施控制 2.锁相环的工作原理 . 锁相环中的鉴相器通常由模拟乘法器组成, 利用模拟乘法器组成的鉴 锁相环中的鉴相器通常由模拟乘法器组成, 相器电路如图 8-4-2 所示。 所示。

锁相放大器设计

C题:锁定放大器的设计 摘要:本设计对于检测微弱信号的锁存放大器进行论述,锁定放大器主要包括交流放大器、带通滤波器、相敏检波器、低通滤波器、直流放大器及液晶显示等几个部分。其中,交流放大器以INA128为主要构成部件,实现交流信号的放大从而作为带通滤波器的输入;带通滤波器用UAF42构成,实现对900Hz到1100Hz频带范围的滤波过程,其误差小于20%;相敏检波器的主要部件采用乘法器MPY634,得到的信号在输入低通滤波器经直流放大器放大后输入显示电路,显示出被测信号的幅度及有效值。另外,在相敏检波器部分的方波驱动信号由参考信道的参考信号经触发整形、移相、比较而来。同时,为了更好的检测出锁定放大器的性能,在信号的输入端增加加法器电路,实现被测信号与干扰信号的1:1叠加,当干扰信号的频率为1050Hz—2100Hz时,输出端的测量误差小于10%。锁定放大器在实际应用中用途广泛,尤其对于微弱信号检测方向站着主导地位,随着科技的发展已渐渐的融入人类的生活之中,拥有很好的发展前景。 关键词:带通滤波器;相敏检波器;显示;方波驱动

1 总体方案设计 1.1方案比较与选择 1.1.1微弱信号检测模块方案比较 方案一:采用滤波电路检测微弱信号,通过滤波电路将微弱信号从强噪声中检测出来,但滤波电路中心频率是固定的,而信号的频率是可变的,无法达到要求,由此可见该方案不满足要求。 方案二:采用取样积分电路检测小信号,采用取样技术,在重复信号出现的期间取样,并重复N次,则测量结果的信噪比可改善√N倍,但这种方法取样效率低,不利于重复频率的信号恢复。 方案三:采用锁相放大器检测小信号,锁相放大器由信号通道、参考通道和相敏检波器等组成,其中相敏检波器(PSD)是锁相放大器的核心,PSD把从信号通道输出的被测交流信号进行相敏检波转换成直流,只有当同频同相时,输出电流最大,具有良好的检波特性。由于该被测信号的频率是指定的且噪声强、信号弱,正好适用于锁相放大器的工作情况,故选择方案三。 1.1.2移相网络模块方案比较 方案一:数字法:采用数字相移的方法势必增加电路的难度,所以此法不可取。 方案二:模拟法:由于电路用的是锁相放大,所以要保持输入信号相位的一致,故需要对参考信号做移相处理,移相采用简单的RC电路搭成,可以很容易得到所需效果。所以采用方案二。 1.1.3电阻分压模块方案比较 电阻分压网络有串联分压和π型网络,π型网络的性能较好,适合在高频的条件下工作,而本设计要求的电压范围较小,故采用简单电路串联来作为分压网络就可以达到要求。 1.1.4显示模块方案 方案一:采用数码管显示。数码管只能显示简单的数字,其电路复杂,占用资源较多,显示信息少,不宜显示大量信息。 方案二:采用液晶显示。液晶显示增加了显示信息的可读性,看起来更方便。而QC12864B字符点阵液晶模块有明显的优点:微功耗、尺寸小、显示信息量大、显示清晰、易控制,抗干扰能力强。

锁相环PLL及APBDIV

第十五篇锁相环PLL及APBDIV 关于锁相环的内容早就应该涉及,因为之前的定时器计数周期,和之后的串口波特率、AD转换频率等都与此相关。 锁相环的英文名为:Phase Locked Loop,其实它的作用就是一个倍频器,它把外部晶振频率(Fosc)加倍后得到系统时钟(Fcclk)给CPU使用,即:Fcclk=Fosc*M,这个M值是可设定的,它就是寄存器PLLCFG 的低五位决定,但M值不能随意设定,比如LPC2103的Fcclk不能超过60MHz。 还有一个频率叫Fcco,它是PLL内部的CCO(电流控制振荡器current controlled oscillator)的频率,Fcco=Fcclk*2*P,P由PLLCFG[6:5]决定,我们不要对它有过多注意力,因为外围电路和Fcco无关,CCO 只是为了保证PLL正常工作且在其内部的一个部件(想知道具体机制查相关资料),我们唯一要做的是使Fcco处于正常的范围(LPC2000系列ARM的CCO要求工作在156~320MHz)之内就行了。 还有,Fpclk是我们必须注意的,芯片外设工作于PCLK(APB clock),(APB和AHB是外围电路中的两种总线,AHB速度快,用于VIC;APB用于其它外设:定时器、串口等),PCLK由FCCLK分频得到(通过APB分频器),分频值由寄存器APBDIV[1:0]决定,其它位保留。 上述频率的关系如下图: 下面具体说明程序中应该如何设置这些频率值: 首先说一下这些倍数的配置寄存器: 所谓M由PLLCFG[4:0]决定,并不是二者相等,而是M=PLLCFG[4:0]+1; 还有P=2^PLLCFG[6:5](2的n次幂); 还有: APBDIV[1:0]=00,Fcclk/Fpclk=1/4; APBDIV[1:0]=01,Fcclk/Fpclk=1; APBDIV[1:0]=10,Fcclk/Fpclk=1/2; APBDIV[1:0]=11,保留。

锁相放大器技术详解

https://www.sodocs.net/doc/1f9798472.html,/st1272/article_22104.html 锁相放大器采用在无线电电路中已经非常成熟的外差式振荡技术,把被测量的信号通过频率变换的方式转变成为直流。 在外差式振荡技术中被称为本地振荡(Local Oscillation)的、用于做乘法运算的信号,在锁相放大器中被称为参照信号,是从外面输入的。锁相放大器能够(从被测量信号中)检测出与这个参照信号频率相同的分量。在被测量的信号里所包含的各种信号分量中,只有与参照信号频率相同的那个分量才会被转换成为直流,因而才能够通过低通滤波器(LPF)。其他频率的分量因为被转换成为频率不等于零的交流信号,所以被低通滤波器(LPF)滤除。在频率域中,如下图所示。 锁相放大器对于噪声的抑制能力,是由上图中低通滤波器(LPF)的截止频率来确定的。例如,在测量10kHz的信号时,如果使用1mHz的低通滤波器(LPF),那么就等效于在使用10kHz±1mHz的带通滤波器时的噪声抑制能力。如果换算成为Q值,就相当于5×106。要想真正制造这样高的Q值的带通滤波器,那是不可能的。但是,使用锁相放大器,这就很容易实现了。 如同前面所解说的那样,在使用通频带非常狭窄的带通滤波器(BPF)时,如果其中心频率与被测量信号的频率有所偏离,那么就会产生测量误差,最糟糕的情况下可能会把被测量信号也滤除了。 与这种情况相比较,对于锁相放大器来说,即使低通滤波器的截止频率多少有些偏离,只要还能够让直流通过,那么对测量结果也不会有大的影响。与带通滤波器相比较,锁相放大器更容易实现通频带非常狭窄的低通滤波器,不管通频带多么狭窄都能实现。由此可见,锁相放大器具有强大的能力从噪声中检测出被掩埋的信号。 那么,实际的锁相放大器又是什么样的呢? ■使用PSD(相敏检波器)作为乘法器。

最新专科模板-简易锁相放大器设计-终稿

专科模板-简易锁相放大器设计-终稿

电子科技大学 毕业论文简易锁相放大器设计 指导教师:张萍职称:讲师 学生姓名:文国江专业: 电子信息工程班级:英特尔班学号:V08024843152 2010年 06 月 01 日 电子科技大学成教院制

目录 第一章选题背景 1.1 背景说明 (3) 1.2 选题依据 (3) 1.3 本文工作 (4) 第二章锁相放大器的原理 (5) 第三章研究与分析 (8) 3.1 参考信号产生的方法比较与选择 (8) 3.2 前端放大器的设计 (8) 3.3 移相方法比较与选择 (8) 3.4 相敏检波器的方法比较与选择 (8) 第四章系统设计 (10) 4.1 总体设计 (10) 4.2 硬件设计 (11) 4.2.1 前置放大器的设计 (11) 4.2.2 移相电路的设计 (12) 4.2.3 相敏检波的设计 (13) 4.2.4 低通滤波器的设计 (14) 4.3 软件设计 (15) 第五章系统测试 (16) 第六章附录 (18) 总结 (26) 致谢 (27) 参考文献 (28)

第一章选题背景 1.1背景说明 1962年美国 EG&G PARC(SIGNAL RECOVERY公司的前身 )的第一台锁相放大器 (Lock-in Amplifier,简称 LIA)的发明,使微弱信号检测技术得到标志性的突破,极大地推动了基础科学和工程技术的发展。目前,微弱信号检测技术和仪器的不断进步,已经在很多科学和技术领域中得到广泛的应用,未来科学研究不仅对微弱信号检测技术提出更高的要求,同时新的科学技术发展反过来促进了微弱信号检测新原理和新方法的诞生。 早期的 LIA是由模拟电路实现的,随着数字技术的发展,出现了模拟与数字混合的 LIA,这种LIA只是在信号输入通道,参考信号通道和输出通道采用了数字滤波器来抑制噪声,或者在模拟锁相放大器(简称 ALIA)的基础上多了一些模数转换( ADC)、数模转换( DAC)和各种通用数字接口功能,可以实现由计算机控制、监视和显示等辅助功能,但其核心相敏检波器 (PSD)或解调器仍是采用模拟电子技术实现的,本质上也是 ALIA。直到相敏检波器或解调器用数字信号处理的方式实现后,就出现了数字锁相放大器(简称 DLIA),DLIA 比 ALIA有许多突出的优点而倍受青睐,成为现在微弱信号检测研究的热点,但是在一些特殊的场合中, ALIA仍然发挥着 DLIA不可替代的作用。 1.2选题依据 微弱信号检测技术是一门新兴的技术科学,它运用近年来迅速发展起来的电子学、信息论和物理学方法,分析噪声产生的原因和规律,研究被测信号和噪声的统计特性及其差别,采用一系列的信号处理方法,达到检测被背景噪声覆盖的微弱信号。运用微弱信号检测技术可以测量到传统观念认为不能测量的微弱信号,如弱光、小位移、微震动、微温差、小电容、弱磁、弱声、微电导、微电流等,使微弱信号测量精度得到很大的提高。 “微弱信号"不仅意味着信号的幅度小,而且主要指的是被噪声淹没的信号,“微弱”是相对于噪声而言的。为了检测被噪声覆盖的微弱信号,人们进行了长期的研究工作,分析噪声产生的原因与规律,研究被测信号的特点、相关性及噪声的统计特性,以寻造出从背景噪声中检测出有用信号的方法。微弱信号检测技术大量应用在光谱学、物理、化学、天文、光通讯、雷达、声纳、以及生物医学工程领域。目前的微弱信号检测的方法有窄带滤波、取样积分、

基于数字锁相环的同步倍频器设计

一、主要内容与要求 1.掌握应用电子设计自动化(EDA)技术设计电子系统的方法; 2.采用超高速集成电路硬件描述语言(Verilog)设计一种基于数字锁相环的倍频器; 3.重点设计数字环路滤波器和数控振荡器; 4.利用计算机仿真技术进行验证; 5.阅读并翻译3000单词以上的英文资料。 二、主要技术要求 n倍频;2 1.系统能够实现输出信号为输入信号的2.改变系统参数可以得到不同的倍频信号,且始终能够使输出信号与输入信号保持同步; 3.用Verilog语言编写设计程序,利用计算机仿真予以验证。 三、研究方法 1.在查阅大量技术资料的基础上,进行设计方案的比较; 2.确定全数字锁相环系统的设计方案; 3.采用自顶向下的设计方法,进行系统模块的划分,并确定用Verilog设计各功能模块的算法; 4.编写系统设计程序,并进行仿真验证,经过反复修改使电路系统达到设计要求。 四、工作进度安排 1.2012年12月学习掌握Verilog设计技术,收集和整理与毕业设计有关的资料; 2.2013年1月在分析和整理资料的基础上写开题报告,确定设计方案和研究技术路线; 3.2013年3月完成环路滤波器和数控振荡器的设计与仿真; 4.2013年4月完成全数字倍频器的系统设计与仿真; 5.2013年5月撰写毕业设计说明书和准备毕业答辩稿; 6.2013年6月初毕业答辩。 指导教师 南华大学本科生毕业设计(论文)开题报告

设计(论文)题目基于数字锁相环的同步倍频器设计 省部级课题设计(论文)题目来源起止时工程设计2012.12013.6 设计(论文)题目类 一、设计(论文)依据及研究意义 锁相(phase-locked loop是一种反馈控制电路,作用是实现设备外部输入信号与内部的震荡信号同步其基本组成包括鉴相 phasedetector环路滤波器loopfilter)和压控振荡器 voltagecontroloscillato) 倍频器frequencymultiplie)是使输出信号频率等于输入信号频率整倍的电路利用非线性电路产生高次谐波或者利用频率控制回路都可以构成倍器倍频器也可由一个压控振荡器和控制环路构成它的控制电路产生一控制压,使压控振荡器的振荡频率严格地锁定在输入频f的倍乘fnf 因为非线性变换过程中产生的大量谐波使输出信号相位不稳定所以其构的倍频器,倍频噪声较大。倍频次数越高,倍频噪声就越大,使倍频器的应用到限制在要求倍频噪声较小的设备中可采用根据锁相环原理构成的锁相环步倍频器 模拟锁相环主要由相位参考提取电路压控振荡器相位比较器控制电等组成压控振荡器输出的是与需要频率很接近的等幅信号把它和由相位参提取电路从信号中提取的参考信号同时送入相位比较器用比较形成的误差通控制电路使压控振荡器的频率向减小误差绝对值的方向连续变化实现锁相而达到同步 数字锁相环主要由相位参考提取电路、晶体振荡器、分频器、相位比较器脉冲补抹门等组成分频器输出的信号频率与所需频率十分接近把它和从信中提取的相位参考信号同时送入相位比较器比较结果示出本地频率高了时就过补抹门抹掉一个输入分频器的脉冲相当于本地振荡频率降低相反若示本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲相当于本振荡频率上升,从而达到同步。.

TDS用锁相放大器电路设计

研究与设计 电 子 测 量 技 术 ELECTRONIC MEASUREMENT T ECHNOLOGY第35卷第4期2012年4月 TDS用锁相放大器电路设计 蒋 鹏 赵国忠 (首都师范大学物理系THz实验室 北京 100048 )摘 要:小型或微型锁相放大器(lock-in amplifier)目前市场罕有,小型THz时域光谱仪(TDS)需要此种仪器。提出了一种LIA设计方案,用于TDS提取与THz波电场强度相关的信号。将差分探测器的信号进行预滤波和放大,后接带通滤波器,同时斩波器输出的信号经移相与前者分别送入AD630的信号端和同步端。锁相后信号经低通滤波器,送入ADC。ADC采集的数据送至上位机进行二滤波处理。整个LIA系统放大微弱信号1 000倍左右,信噪比700dB以上,电路板面积11cm×5.5cm, 达到基本指标。关键词:锁相放大器;AD630;太赫兹探测;互相关;Multisim中图分类号:TN911 文献标识码:A Design of lock-in amp lifier circuit for TDSJiang Peng Zhao Guozhong(THz Lab,Department of Physics,Capital Normal University,Beijing 100048)Abstract:A small or miniature lock-in amplifier(LIA)is rare on market,which is used for small Terahertz time domainsp ectrometer(TDS).LIA scheme design is proposed,and it is used for TDS to extract weak signal,which is related toTHz wave field strength.The signal of differential detector is to be pre-filted and amplificated,then it is connected withband-pass filter.While together with the signal from chopper are put into the AD630 s output terminals andsynchronization port respectively.The signal after lock-in amp lifier is put into low-pass filter then to ADC.Then it isp ut into host computer for filtering.The signal after system has 1000times amplification,more than 700db SNR,andsy stem size is 11cmx5.5cm,which meet the basic indicators.Key words:lock-in amplifier;AD630;THz detector;correlation;Multisim 本文于2 012年3月收到。0 引 言 作为一种精密的测试仪器 [1] ,锁相放大器被广泛的用 在科研领域,尤其是在检测微弱小信号方面。但灵活小巧,轻便的小型或微型锁相放大器市场少有,而一些便携式光谱仪则需要用到小型锁相放大器。在THz时域光谱仪(TDS)[2 ],尤其是小型TDS系统里,更需要小型或者微型锁相放大器。太赫兹时域光谱仪已经在各种材料的检测领域应用广泛, 例如爆炸物或者毒品的检测。但是国内目前在小型TDS系统的发展上出现一些瓶颈,系统中需要有小型锁相放大器。 1 原 理 锁相放大器是基于互相关检测原理(见图1)来实现从大背景噪声中提取微弱的有用信号。当输入信号与参考信号频率完全一致的信号在乘法器的输出端得到直流偏量, 其他信号在输出端都是交流信号,要是在乘法器后加一个低通滤波器, 滤除交流分量,那么剩下的直流分量,而这个直流分量只是正比于输入信号中的特定频率的信号分量的幅值。 图1 互相关检测原理 2 实施方案 为实现低成本小体积的锁相放大器,采集太赫兹时域光谱仪中的差分探头产生的信号。通过核心器件AD630 (平衡调制解调器)做锁相放大,以提取被噪声淹没的微弱

PLL 锁相环原理

什么是锁相环(PLL)工作原理及对硬件电路连接的要求锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同 步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在 比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。 在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。因此,所有板卡上各自的本地80MHz 和20MHz时基的相位都是同步的,从而采样时钟也是同步的。因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。 通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的 10MHz背板时钟同步来实现锁相环同步的。 锁相环(PLL)的工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的 原理框图如图8-4-1所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

锁相放大器原理

如何测量被噪声埋没了的信号? 在测量各种物理量(温度、加速度等)时,用传感器将其变换成为电信号,然后输入到分析仪器(测量仪器)中去。但是,仅想获得必要的信号是很难做到的。通常是连不必要的信号(也就是噪声)也一起被测量了。在各种情况下,噪声都有可能混进来。 噪声并不仅限于电信号,也有包含在被测量的物理量中的情况。另外,根据不同场合,也出现噪声强度远远高出所需要的目的信号电平的情况。想要测量的信号越微弱,那么噪声就相对地越大。 在这里,让我们来看一下用交流电压表来测量不同电平的1kHz 的正弦波信号的结果。 在信号上叠加了0.1Vmrs 的白噪声。“毫伏计”是一般的交流电压表,“锁相放大器”是一种专门测量微小信号的(特殊的)交流电压表。 信号电平 (正弦波信号) 波 形 (叠加了噪声的波形) 毫伏计的 测量结果 锁相放大器的 测量结果 1Vrms 1Vrms 0.999Vrms 100mVrms 140mVrms 99mVrms

1mVrms 105mVrms 1.01mVrms 0.1mVrms 105mVrms 0.107mVrms 毫伏计也同时测量噪声。即使用数字万用表(DMM )来测量,也会得到与毫伏计相同的测量结果。 但锁相放大器,能在比目的信号(1kHz 正弦波)强1000倍的噪声中把目的信号几乎准确无误地检测出来。 在测量埋没在噪声中的信号时,使用锁相放大器最为合适。 为什么锁相放大器具有那么强的抗噪声能力? 锁相放大器不容易受到噪声影响的原因,是因为很好地利用了噪声(白噪声)与目的信号(正弦波)之间在性质上的差别。 在这里,我们一方面整理白噪声的性质和正弦波的性质,一方面解说为什么锁相放大器会具有很强的噪声抑制能力。 噪声的性质 ■平坦的频谱 在宽阔的频率范围内,该信号具有几乎相同的频谱。信号的瞬时电平成为预测不到的随机的值。

倍频器原理

4、倍频器 (1)功能。倍频器实质上就是一种输出信号等于输入信号频率整数倍的电路,常用的是二倍频和三倍频器。在手持移动电话中倍频器的主要作用是为了提升载波信号的频率,使之工作于对应的信道;同时经倍频处理后,调频信号的频偏也可成倍提高,即提高了调频调制的灵敏度,这样可降低对调制信号的放大要求。采作倍频器的另一个好处是:可以使载波主振荡器与高频放大器隔离,减小高频寄生耦合,有得于减少高频自激现象的产生,提高整机工作稳定性。 (2)倍频原理。由晶体三极管组成的倍频电路如下图所法,它的基本原理是:三极管VT1的基极不设置或设置很低的静态工作点,三极管工作于非线性状态,于是输入信号经管子放大,其集电极电流会产生截止切割失睦,输出信号信号丰富的谐波分量,利用选频网络选通所需的倍频信号,而滤除基波和其他谐波分量后,这就实现了对输入信号 的倍频功能。 5、射频功率放大器手持移动电话发射端的高频信号功率越大,天线转换成电磁波的能量也越大,天线转换成电磁波的能量也越大,通信距离就越远;反之,输出高频信号功率越小,通信距离就越近。为了保证一定距离的无线电通信正常,必须对射频信号进行功率放大。对手机射频功率放大器的主要要求有以下四个方面。 (1)输出功率能达到要求,电路有一定的输出功率功率余量。 (2)电路效率高,以节约直流电源用电量。

(3)具有良好的谐波抑制能力,杂波辐射量要小。 (4)具有功率自动控制电路,以防止电源电压变化或振荡输出电 压幅度不稳定引起的过激励,避免末级功放电路的烧毁。 目前手持移动电话的射频功率放大器广泛应用厚膜混合集成功放块,其特点是将射频功放器件组成整件,体积小,可*性高,组装及检修方便。功率自动控制电路使输出功率保持在一定范围内,其工作原理框图如下图所示。末级功放输出的信号经耦合器采样取出部分信号功率,经过检波变成直流送入放大器放大,放大后的电平再耦合至微处理器进行检测,并由微处理器送出一个控制指令到功率放大器,从而调整 功率电平使之能满足要求。 三、锁相环频率合成器 1、电路组成 基本锁相环频率合成器主要由鉴相器、低通滤波器、压控振荡器和 可编程分频器组成。 鉴相器又称相位比较器,其作用是将检测信号与基准信号进行相位比较,并输出一个反映两信号相位差大小的电压。 低通滤波器的作用是滤除鉴相器输出电压的干扰成分,使之更加纯净地反映两比较信号相位差的大小。 压控振荡器是一个振荡频率受电压大小控制的振荡电路,实际上是 一个调频振荡电路。

锁相放大器

锁相放大器实验 锁相放大器实验(Lock-in amplifier),简称LIA。它是一个以相关器为核心的检测微弱信号仪器,它能在强噪声情况下检测微弱正弦的幅度和相位。学习本实验的目的是使同学了解锁相放大器的基本组成,掌握锁相放大器的正确使用方法。 一、锁相放大器的基本组成 结构框图如图1所示。它有四个主要部分组成:信号通道、参考通道、相关器(即相关检测器)和直流放大器。 图1 锁相放大器的基本结构框架 1.信号通道 信号通道包括:低噪音前置放大器、带通滤波器及可变增益交流放大器。 前置放大器用于对微弱信号的放大,主要指标是低噪音及一定的增益(100~1000倍)。 可变增益放大器是信号放大的主要部件,它必须有很宽的增益调节范围,以适应不同的信号的需要。例如,当输入信号幅度为10nV,而输出电表的满刻度为10V时,则仪器总增益为10V/10nV =109若直流放大器增益为10倍,前置放增益为103,则交流放大器的增益达105。 带通滤波器是任何一个锁相放大器中必须设置的部件,它的作用是对混在信号中的噪音进行滤波,尽量排除带外噪音。这样不仅可以避免PSD(相敏检波器)过载,而且可以进一步增加PSD输出信噪比,以确保微弱信号的精确测量。常用的带通滤波器有下列几种:

图2为一个高通滤波器和一个低通波滤 波器组成的带通滤波器,其滤波器的中心频 率f0及带宽B由高低滤波器的截止频率f c1 决定和f c2决定。锁相放大器中一般设置几种 截止频率,从而根据被测信号的频率来选择 合适的频率f0及带宽B。但是带宽滤波器带 宽不能过窄,否则,由于温度、电源电压波 动使信号频谱离开带通滤波器的通频带,使 输出下降。 为了消除电源50Hz的干扰,在信号通道 中常插入组带滤波器。 (2)同步外差技术 上述高低通滤波器的主要缺点是随着被 测信号频率的改变,高低通滤波器的参数也 要改变,高低通滤波器的参数也要改变,应 用很不方便。为此,要采用类似于收音机的 同步外差技术,原理框图如图3所示。这是一种单外差技术,PSD1实际上是一个混频器, 图2 高低通频滤波器原理,具有频率f0信号经放大滤波后进入混频PSD,其输出为和频项(f i+2f0)及差频f i,再经具有中心频率为f i带通滤波后,输出变为中频信号f i , (幅度仍与被测信号的幅度成正比)再后,通过PSD2完成相敏检波后,得到解调输出U0,达到了对信号幅度的测量。外差方式的优点是采用固定中频f i 的带通滤波器,因而对不同被测信号频率均能适用;其次,由于采用固定中频带通滤波器,故滤波器的带宽及形状可以专门设计,所 以本电路具有很强的抑制噪音的能力。 图 3 同步外差技术原理框图 (3)同步积分技术

锁相放大器综述

题目: 锁相放大器的原理及应用 姓名: 单位: 学号: 联系方式:

摘要 锁相放大器又称锁定放大器是对正弦信号(含具有窄带特点的调幅信号)进行相敏检波的放大器,它实际上是一个模拟的傅立叶变换器,在强噪声下,利用有用信号的频率值准确测出有用信号的幅值。应用在科学研究的各个领域中:如通讯、工业、国防、生物、海洋等。本文主要介绍了锁相放大器原理,发展过程,基本组成,重要参数和在各方面的应用。 关键词:锁相放大器,噪声,傅立叶变换

一、锁相放大器的定义 锁相放大器是一种对交变信号进行相敏检波的放大器。它利用和被测信号有相同频率和相位关系的参考信号作为比较基准,只对被测信号本身和那些与参考信号同频(或者倍频)、同相的噪声分量有响应。因此,能大幅度抑制无用噪声,改善检测信噪比。此外,锁相放大器有很高的检测灵敏度,信号处理比较简单,是弱光信号检测的一种有效方法。锁相放大器又称锁定放大器是对正弦信号(含具有窄带特点的调幅信号)进行相敏检波的放大器,它实际上是一个模拟的傅立叶变换器,在强噪声下,利用有用信号的频率值准确测出有用信号的幅值。应用在科学研究的各个领域中:如通讯、工业、国防、生物、海洋等。 二、锁相放大器的历史 上世纪六十年代美国公司研制出第一台利用模拟电路实现微弱正弦信号测量的锁相放大器,使微弱信号检测技术突破性飞越,为解决大量电子测量做出贡献,在物质表面组份分析以及表面电子能态研宄方面有重大意义。自上世纪后期开始,国内外越来越多的人开始研宄锁相放大器,随着科技的发展,越来越多性能优良的锁相放大器被研发出来,在各个领域应用广泛,极大程度上推动了各个学科的发展,目前,从提高系统的灵敏度、减小噪声带宽、提高检测精度、改善信噪比上都有了很大的进步。近年来,数字电子技术飞速发展,锁相放大器也在这一契机下,出现了模数混合的锁相放大器与数字锁相放大器,这在一定程度上弥补了由于物理器件造成的模拟锁相放大器的缺点,极大改善了性能,提升了研究层次与扩大了应用范围。国外相较于国内而言,起步要早一些,己研发出一系列锁相放大器。美国公司、美国公司是行业的龙头企业,它们所研制的模拟型:、和数字型:、、、均已有较成熟的发展与应用。其中公司是世界范围内数字锁相放大器研制的佼佼者,该公司的产品在到的频率带宽内可测,具有自动获取、自动补偿功能,具有谐波抑制功能、度的相位分辨率和大于的动态保留,时间常数位从到可调,它的数字信号处理设计使它具有很大的动态存储,这就减少了使用带通滤波器时带进的噪声以及系统的不稳定性。就国内而言,南京大学唐鸿宾等对锁相放大器的研宄起步较早,研发出了系列锁相放大器,该校微弱信号检测中心顺势

锁相放大器实验报告BY陈群

锁相放大器实验报告BY陈群 浙江师范大学实验报告实验名称锁相放大实验班级物理071 姓名陈群学号 07180116 同组人刘懿钧实验日期 09/12/1 室温气温锁相放大实验 摘要: 锁相放大器(Lock-in amplifier,LIA)自问世以来,在微弱信号检测方面显示 出优秀的性能,它能够在较强的噪声中提取信号,使测量精度大大提高,在科学 研究的各个领域得到了广泛的应用。它利用待测信号和参考信号的互相关检测原理实现对信号的窄带化处理,能有效地抑制噪声,实现对信号的检测和跟踪。 因此,学生掌握锁相放大技术的原理与应用具有重要的意义。关键词: 锁相放大器微弱信号 PSD信号 引言: 在进展一日千里的现代科技领域中,精密量测技术的发展对于近代工业有关键 性的影响。当我们研究的系统日趋庞大,交互作用复杂,但所欲了解的现象却越来越精细时,如何在一大堆讯号中获得我们真正想要的信息便成为一个重要的课题。一般的线性放大器可以将微弱的电子讯号放大,但若我们所要的信号中伴随着噪声信号,则两者都会一起放大,亦即此伴随的噪声无法滤除。尤其当噪声强度远大于所要的信号时,即必须藉助特殊的放大器以同时放大讯号并滤去噪声。锁相放大器是一种能测量极微弱的连续周期性信号的仪器。这些微弱信号可以小至数奈伏特(nV),甚至隐藏在大它数千倍的噪声当中,亦能精确的测得。连续周期性信号与噪声不同之处,在于前者具有固定的频率及相位,

后者则杂乱无章。锁相放大器便是利用所谓”相位灵敏侦测(phase-sensitive detection,PSD)” 的技术以取得具有特定频率与相位的信号,而不同于此频率 的噪声则被抑制下来,使输出讯号不受噪声影响。 实验方案: 实验原理 锁相放大器的基本结构如图所示,包括信号通道、参考通道、相敏检测器(PSD)和低通滤波器(LPF)等。 信号通道对调制正弦信号输入进行交流放大,将微弱信号放大到足以推动相敏检测器工作的平台,并且要滤除部分干扰和噪声,以提高相敏检测的动态范围。 参考通道对参考输入进行放大和衰减,以适应相敏检测器对幅度的要求。参考通道的另一个重要功能是对参考输入进行移相处理,以使各种不同的相移信号的检测结果达到最佳。 锁相放大器的核心部件是PSD,它以参考信号r(t)为基准,对有用信号x(t)进行相敏检测,从而实现频谱迁移过程。将x(t)的频谱由ω=ω0处,再经LPF滤除噪声,输出直流信号,其幅度与两路输入信号幅度及它们的相位有关。其输出 u0(t)对x(t)的幅度和相位都敏感,这样就达到了既鉴幅又鉴相的目的。因为LPF 的频带可以做得很窄,所以可使锁相放大器达到较大的SNIR。下图为不同相位时 相敏检测器的输出波形

锁相放大器(Lock-in-Amplifier)的原理与应用

lock-in D y T nV?C a A i H μq C Lock-in-Amplifier D n u I ”ˉe ”?A q S v P A L o i q o C Lock-in-Amplifier ]PSD(phase sensitive detector)?A q S v B A L o L q H C Lock-in q n v A A O i A v f 1G )2sin(1111φπ+=f E e P )2sin(2222φπ+=f E e q L V (mixer)2V o μG G )2sin()2sin(221121213φπφπ++=×=f f E E e e e )]()(2cos[2 )]()(2cos[2212121212121φφπφφπ+++??+?= f f E E f f E E (difference frequency component) (sum frequency component) PSD AC A p q L C q o i A AC o C p G f 1μ¥f 2?éA difference frequency component DC A o p U PSD )cos(2 212 13φφ?= E E e )1)(cos(21≈?φφ

Lock-in lock-in i1V q A q I+P I- S C H q eμn u C B p U G 1.q e A i q q q A A P q q y p A o B n A P A q y a C 2.q(q u p)A i q(1M[B 10M[B100M[B1G[)M q y K q10K[(]q 10K[) 3. lock-in (1) ¥lock-in sensitivity A A lock-inμu(p G) μu C (2) °10-7A A i q10M[A q A A lock-in sensitivity A(1mV)A qμ 10V(q O lock-in q10μG)C (3) ?(OSC LvL)]1V A v(OSC F)P60 (p G23)A K P A(REF PH)Aμ(90o)μ0-V Bμê(270 o)μ0+V A(0 o B180 o)10V C p U G Lock-in A lock-inμq C 1.lock-in sensitivity A o i BP A time constant]1s A A lock-in I qμu(p)μu C 2. °10-7A A i q10M[A q A A lock-in sensitivity A(1mV)A qμ10V C

倍频器

3.3倍频器电路模块 10uF 3.3.1 CD4046芯片简介 锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如图1所示。 压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。这个平均值电压Ud朝

着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。 当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。 3.3.2 CD4046芯片引脚及引脚功能 图2是CD4046的引脚排列,采用16 脚双列直插式。 各引脚功能如下:

锁相放大器的工作原理

检测微弱信号的核心问题是对噪声的处理,最简单、最常用的办法是采用选频放大技术,使放大器的中心频率f 0与待测信号频率相同,从而对噪声进行抑制,但此法存在中心频度不稳、带宽不能太窄及对等测信号缺点。后来发展了锁相放大技术。它利用等测信号和参与信号的相互关检测原理实现对信号的窄带化处理,能有效的抑制噪声,实现对信号的检测和跟踪。目前,锁相放大技术已广泛地用于物理、化学、生物、电讯、医学等领域。因此,培养学生掌握这种技术的原理和应用,具有重要的现实意义。 1.锁相放大器的工作原理 1.相关检测及相关检测器。所谓相关,是指两个函数不相关(彼此独立); 如果它们的乘积对时间求平均(积分)为零,刚表明这两个函数的关系又可分为自相关和互相关两种。由于互相关检测抗干扰能力强,因此在微弱信号检测中大都采用互相关检测原理。 如果f1(t)和f2(t-τ)为两个功率有限信号,刚可定义它们的互相关函数为 (3.1.1) 令f1(t)=V1(t)+n1(t),f2(t)=V1(t)+n2(t),其中n1(t)和n2(t)分别代表与待测信号V1(t)及参考信号V2(t)混在一起的噪声,则式(3.1.1)可写成 (3.1.2) 式中Rsr(τ),Rr2(τ),Rr1(τ),R12(τ)分别是两信号之间,信号对噪声及噪声之间的函数。由于噪声的频率和相位都是随机量,他们的偶尔出现可用长时间积分使它不影响信号的输出。所以,可认为信号和噪声、噪声和噪声之间是互相独立的,他们的互相关函数为零。于是式(3.1.2)可写成 (3.1.3) 上式表明,对两个混有噪声的功率有限信号进行相乘和积分处理(即相关检测)后,可将信号从噪声中检出,噪声被抑制,不影响输出。根据此原理设计的相关检测器见图(3.1.1)所示。它是锁相放大器的心脏。

锁相环倍频器

锁相环倍频器

摘要 倍频器(frequency multiplier)使输出信号频率等于输入信号频率整数倍的电路。输入频率为f1,则输出频率为f0=nf1,系数n为任意正整数,称倍频次数。倍频器用途广泛,如发射机采用倍频器后可使主振器振荡在较低频率,以提高频率稳定度;调频设备用倍频器来增大频率偏移;在相位键控通信机中,倍频器是载波恢复电路的一个重要组成单元。 利用非线性电路产生高次谐波或者利用频率控制回路都可以构成倍频器。倍频器也可由一个压控振荡器和控制环路构成。它的控制电路产生一控制电压,使压控振荡器的振荡频率严格地锁定在输入频率f1的倍乘值f0=nf1上。

目录 一课题目 (4) 二课题介绍 (4) 三关键词 (4) 四锁相环介绍 (4) 五CD4046介绍 (6) 六CD4518介绍 (10) 七锁相环倍频器设计电路及工作原理 (12) 八电路元件清单 (13) 九焊接与制作 (13) 十实物图 (14) 十一心得体会 (14) 十二参考文献 (15) 十三致谢 (15)

题目锁相环倍频器 一.本次课程设计主要是配合《模拟电子技术》和数字电子技术》理论课程而设置的一次实践性课程,祈祷巩固所学知识,加强综合实力,培养电路设计能力,提高实验技术,启发创新思想的效果。 二.课程介绍 倍频器有晶体管倍频器、变容二极管倍频器、阶跃恢复二极管倍频器等。用其他非线性电阻、电感和电容也能构成倍频器,如铁氧体倍频器等。非线性电阻构成的倍频器,倍频噪声较大。这是因为非线性变换过程中产生的大量谐波使输出信号相位不稳定而引起的。倍频次数越高,倍频噪声就越大,使倍频器的应用受到限制。在要求倍频噪声较小的设备中,可采用根据锁相环原理构成的锁相环倍频器和同步倍频器。 三.关键词 锁相环CD4046 CD4518 四.锁相环介绍 锁相环(phase-locked loop):为无线电发射中使频率较 为稳定的一种方法,。锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如图1所示。